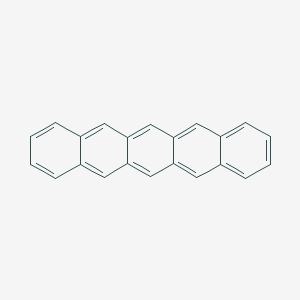

Pentacene

Beschreibung

Eigenschaften

IUPAC Name |

pentacene | |

|---|---|---|

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

InChI |

InChI=1S/C22H14/c1-2-6-16-10-20-14-22-12-18-8-4-3-7-17(18)11-21(22)13-19(20)9-15(16)5-1/h1-14H | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

InChI Key |

SLIUAWYAILUBJU-UHFFFAOYSA-N | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Canonical SMILES |

C1=CC=C2C=C3C=C4C=C5C=CC=CC5=CC4=CC3=CC2=C1 | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Molecular Formula |

C22H14 | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Related CAS |

78260-42-1 | |

| Record name | Pentacene, dimer | |

| Source | CAS Common Chemistry | |

| URL | https://commonchemistry.cas.org/detail?cas_rn=78260-42-1 | |

| Description | CAS Common Chemistry is an open community resource for accessing chemical information. Nearly 500,000 chemical substances from CAS REGISTRY cover areas of community interest, including common and frequently regulated chemicals, and those relevant to high school and undergraduate chemistry classes. This chemical information, curated by our expert scientists, is provided in alignment with our mission as a division of the American Chemical Society. | |

| Explanation | The data from CAS Common Chemistry is provided under a CC-BY-NC 4.0 license, unless otherwise stated. | |

DSSTOX Substance ID |

DTXSID7059648 | |

| Record name | Pentacene | |

| Source | EPA DSSTox | |

| URL | https://comptox.epa.gov/dashboard/DTXSID7059648 | |

| Description | DSSTox provides a high quality public chemistry resource for supporting improved predictive toxicology. | |

Molecular Weight |

278.3 g/mol | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Physical Description |

Deep blue solid with violet luster; [Merck Index] | |

| Record name | Pentacene | |

| Source | Haz-Map, Information on Hazardous Chemicals and Occupational Diseases | |

| URL | https://haz-map.com/Agents/8635 | |

| Description | Haz-Map® is an occupational health database designed for health and safety professionals and for consumers seeking information about the adverse effects of workplace exposures to chemical and biological agents. | |

| Explanation | Copyright (c) 2022 Haz-Map(R). All rights reserved. Unless otherwise indicated, all materials from Haz-Map are copyrighted by Haz-Map(R). No part of these materials, either text or image may be used for any purpose other than for personal use. Therefore, reproduction, modification, storage in a retrieval system or retransmission, in any form or by any means, electronic, mechanical or otherwise, for reasons other than personal use, is strictly prohibited without prior written permission. | |

CAS No. |

135-48-8 | |

| Record name | Pentacene | |

| Source | CAS Common Chemistry | |

| URL | https://commonchemistry.cas.org/detail?cas_rn=135-48-8 | |

| Description | CAS Common Chemistry is an open community resource for accessing chemical information. Nearly 500,000 chemical substances from CAS REGISTRY cover areas of community interest, including common and frequently regulated chemicals, and those relevant to high school and undergraduate chemistry classes. This chemical information, curated by our expert scientists, is provided in alignment with our mission as a division of the American Chemical Society. | |

| Explanation | The data from CAS Common Chemistry is provided under a CC-BY-NC 4.0 license, unless otherwise stated. | |

| Record name | Pentacene | |

| Source | ChemIDplus | |

| URL | https://pubchem.ncbi.nlm.nih.gov/substance/?source=chemidplus&sourceid=0000135488 | |

| Description | ChemIDplus is a free, web search system that provides access to the structure and nomenclature authority files used for the identification of chemical substances cited in National Library of Medicine (NLM) databases, including the TOXNET system. | |

| Record name | PENTACENE | |

| Source | DTP/NCI | |

| URL | https://dtp.cancer.gov/dtpstandard/servlet/dwindex?searchtype=NSC&outputformat=html&searchlist=90784 | |

| Description | The NCI Development Therapeutics Program (DTP) provides services and resources to the academic and private-sector research communities worldwide to facilitate the discovery and development of new cancer therapeutic agents. | |

| Explanation | Unless otherwise indicated, all text within NCI products is free of copyright and may be reused without our permission. Credit the National Cancer Institute as the source. | |

| Record name | Pentacene | |

| Source | EPA Chemicals under the TSCA | |

| URL | https://www.epa.gov/chemicals-under-tsca | |

| Description | EPA Chemicals under the Toxic Substances Control Act (TSCA) collection contains information on chemicals and their regulations under TSCA, including non-confidential content from the TSCA Chemical Substance Inventory and Chemical Data Reporting. | |

| Record name | Pentacene | |

| Source | EPA DSSTox | |

| URL | https://comptox.epa.gov/dashboard/DTXSID7059648 | |

| Description | DSSTox provides a high quality public chemistry resource for supporting improved predictive toxicology. | |

| Record name | Pentacene | |

| Source | European Chemicals Agency (ECHA) | |

| URL | https://echa.europa.eu/substance-information/-/substanceinfo/100.004.722 | |

| Description | The European Chemicals Agency (ECHA) is an agency of the European Union which is the driving force among regulatory authorities in implementing the EU's groundbreaking chemicals legislation for the benefit of human health and the environment as well as for innovation and competitiveness. | |

| Explanation | Use of the information, documents and data from the ECHA website is subject to the terms and conditions of this Legal Notice, and subject to other binding limitations provided for under applicable law, the information, documents and data made available on the ECHA website may be reproduced, distributed and/or used, totally or in part, for non-commercial purposes provided that ECHA is acknowledged as the source: "Source: European Chemicals Agency, http://echa.europa.eu/". Such acknowledgement must be included in each copy of the material. ECHA permits and encourages organisations and individuals to create links to the ECHA website under the following cumulative conditions: Links can only be made to webpages that provide a link to the Legal Notice page. | |

| Record name | PENTACENE | |

| Source | FDA Global Substance Registration System (GSRS) | |

| URL | https://gsrs.ncats.nih.gov/ginas/app/beta/substances/9FQU5HA0UY | |

| Description | The FDA Global Substance Registration System (GSRS) enables the efficient and accurate exchange of information on what substances are in regulated products. Instead of relying on names, which vary across regulatory domains, countries, and regions, the GSRS knowledge base makes it possible for substances to be defined by standardized, scientific descriptions. | |

| Explanation | Unless otherwise noted, the contents of the FDA website (www.fda.gov), both text and graphics, are not copyrighted. They are in the public domain and may be republished, reprinted and otherwise used freely by anyone without the need to obtain permission from FDA. Credit to the U.S. Food and Drug Administration as the source is appreciated but not required. | |

Foundational & Exploratory

Pentacene Crystal Structure and Polymorphism: An In-depth Technical Guide

For Researchers, Scientists, and Drug Development Professionals

Introduction

Pentacene, a polycyclic aromatic hydrocarbon, stands as a benchmark organic semiconductor due to its exceptional charge carrier mobility. Its performance in electronic devices is intrinsically linked to its solid-state packing, giving rise to multiple crystalline forms, or polymorphs. Understanding and controlling the formation of these polymorphs is paramount for optimizing the performance and reproducibility of this compound-based devices. This technical guide provides a comprehensive overview of the crystal structure and polymorphism of this compound, detailing the crystallographic parameters of its various forms and the experimental protocols for their preparation.

This compound Polymorphism: A Structural Overview

This compound is known to crystallize in several polymorphic forms, primarily distinguished by their interlayer spacing (d(001)). These polymorphs are broadly categorized into "thin-film" phases, which are often induced by the substrate during thin-film deposition, and "bulk" phases, typically found in single crystals. The molecules in all polymorphs adopt a herringbone packing motif within the layers. The key differentiator between the polymorphs is the tilt angle of the long molecular axis with respect to the normal of the ab plane.[1]

The two most commonly discussed bulk polymorphs are the low-temperature (LT) and high-temperature (HT) phases.[2] Thin films, especially those grown on silicon dioxide, often exhibit a distinct "thin-film" (TF) phase.[2][3] Other polymorphs with different d-spacings have also been reported, particularly in the initial layers of film growth.[2][4]

Data Presentation: Crystallographic Parameters of this compound Polymorphs

The following table summarizes the crystallographic data for the most well-characterized this compound polymorphs. It is important to note that slight variations in these parameters can be found in the literature, which may arise from different experimental conditions and measurement techniques.

| Polymorph | d(001) Spacing (Å) | Crystal System | Space Group | a (Å) | b (Å) | c (Å) | α (°) | β (°) | γ (°) | Unit Cell Volume (ų) | Reference(s) |

| Thin-Film (TF) Phase | 15.4 - 15.5 | Triclinic | P-1 | 5.9 - 7.6 | 5.9 - 7.6 | 15.4 - 15.65 | 81.5 - 98.6 | 87.2 - 93.3 | 89.8 - 90 | ~697 | [3][5] |

| Bulk Phase (High-Temp) | 14.4 - 14.5 | Triclinic | P-1 | 6.28 | 7.71 | 14.44 | 76.75 | 88.01 | 84.52 | ~683 | [1] |

| Bulk Phase (Low-Temp) | 14.1 | Triclinic | P-1 | 6.27 | 7.78 | 14.51 | 76.6 | 88.0 | 84.7 | ~684 | [2] |

| Substrate-Induced Phase | 15.0 | - | - | - | - | - | - | - | - | - | [4] |

| Substrate-Induced Phase | 15.7 | - | - | - | - | - | - | - | - | - | [2] |

Inter-Polymorph Relationships and Transformations

The formation of a specific this compound polymorph is highly dependent on the experimental conditions, such as substrate temperature, deposition rate, and the presence of solvents. The thin-film phase is often observed in the initial layers of growth, with a transition to a bulk phase as the film thickness increases.[6][7] Furthermore, thermal annealing can induce transformations between polymorphs. For instance, some substrate-induced polymorphs with larger d-spacings have been observed to transform into the more stable bulk phases upon heating.[4]

References

electronic properties of pentacene thin films

An in-depth technical guide to the , designed for researchers, scientists, and drug development professionals.

Introduction

Pentacene (C₂₂H₁₄) is a polycyclic aromatic hydrocarbon consisting of five linearly fused benzene (B151609) rings. It has emerged as a benchmark p-type organic semiconductor due to its relatively high charge carrier mobility and robust performance in organic thin-film transistors (OTFTs).[1][2] Its well-ordered molecular packing in thin films facilitates efficient charge transport, making it a material of great interest for applications in flexible displays, sensors, and RFID tags.[1][3] The are not intrinsic to the molecule itself but are critically dependent on the film's structural and morphological characteristics, which are, in turn, dictated by fabrication conditions.[4][5] Understanding the interplay between processing, structure, and electronic performance is paramount for designing high-performance organic electronic devices.

Core Electronic Properties

The performance of this compound-based devices is quantified by several key electronic parameters, primarily derived from the characterization of thin-film transistors.

Charge Carrier Mobility (μ)

Field-effect mobility is a measure of how quickly charge carriers (holes in the case of this compound) move through the semiconductor under the influence of an electric field. It is the most common figure of merit for OTFTs. This compound thin films have demonstrated some of the highest mobilities among organic semiconductors, often exceeding that of amorphous silicon.[2] However, reported values span several orders of magnitude, from less than 10⁻³ cm²/Vs to as high as 8.85 cm²/Vs, reflecting the profound impact of film quality and device architecture.[6][7][8] High mobility is generally associated with large, well-ordered crystalline grains and minimal defects.[4][9]

On/Off Current Ratio

The On/Off ratio is the ratio of the drain current when the transistor is in the "on" state (gate voltage applied) to the "off" state (zero or positive gate voltage). A high On/Off ratio is crucial for digital logic applications to ensure clear switching behavior and low standby power consumption. This compound OTFTs typically exhibit excellent On/Off ratios, often in the range of 10⁵ to 10⁸.[4][6]

Threshold Voltage (Vth)

The threshold voltage is the minimum gate voltage required to induce a conducting channel and turn the transistor "on". For p-type accumulation-mode devices like those made with this compound, Vth is typically negative. Its value is sensitive to charge traps at the semiconductor-dielectric interface and within the bulk of the semiconductor.[6][10]

Contact Resistance (Rc)

In OTFTs, the resistance at the interface between the metal source/drain electrodes and the organic semiconductor can significantly limit device performance, especially in short-channel devices.[11] This contact resistance is not a fixed value but is dependent on the gate voltage, electrode geometry (top vs. bottom contact), and the choice of metal.[12] For this compound, gold (Au) is a common electrode material. Contact resistance values have been reported in the range of 10⁶ to 10¹⁰ Ω, with width-normalized values as low as 10 Ωcm achievable under optimized conditions.[13]

Factors Influencing Electronic Properties

The electronic characteristics of this compound thin films are intricately linked to a variety of controllable factors during fabrication.

Deposition Method and Conditions

Thermal evaporation in a high vacuum is the most common method for depositing high-quality this compound films.[14][15] Key parameters include:

-

Deposition Rate: Slower deposition rates (e.g., < 1 Å/s) generally promote larger grain sizes and better molecular ordering, leading to higher mobility.[6]

-

Substrate Temperature: Deposition at elevated substrate temperatures (e.g., 60-80 °C) can enhance molecular diffusion on the surface, resulting in larger, more ordered crystalline domains and improved device performance.[9][12]

-

Vacuum Pressure: A high vacuum (e.g., 10⁻⁶ Torr or lower) is necessary to minimize impurities and contamination in the film.[16]

Solution-based methods, such as spin coating of a soluble this compound precursor, offer a lower-cost, large-area alternative, with reported mobilities reaching up to 0.38 cm²/Vs.[17][18]

Film Morphology and Structure

The morphology of the film at the microscopic level is a primary determinant of its electronic properties.

-

Grain Size and Boundaries: this compound films are typically polycrystalline. Charge transport involves movement within crystalline grains (intra-grain) and hopping between them (inter-grain).[19] Larger grains reduce the number of grain boundaries, which act as scattering centers and traps for charge carriers, thus leading to higher mobility.[9][19]

-

Crystalline Phase: this compound can exist in different polymorphic structures. The "thin-film phase," with an interlayer spacing of approximately 15.4 Å, is often observed in films grown on inert substrates and is associated with higher charge carrier mobility compared to the "bulk phase" (spacing ~14.5 Å).[14][16]

Dielectric Interface

The interface between the this compound film and the gate dielectric is where the conductive channel is formed in a TFT. Its quality is critical.

-

Surface Energy and Roughness: A smooth dielectric surface with appropriate surface energy promotes the growth of well-ordered this compound films.[5][20]

-

Surface Treatment: Modifying the dielectric surface with self-assembled monolayers (SAMs), such as octadecyltrichlorosilane (B89594) (OTS), is a common strategy to reduce surface traps, improve molecular ordering, and significantly enhance mobility.[21] Mobilities as high as 1.25 cm²/Vs have been reported on OTS-treated SiO₂.[21]

Electronic Structure

-

HOMO-LUMO Gap: The energy gap between the Highest Occupied Molecular Orbital (HOMO) and the Lowest Unoccupied Molecular Orbital (LUMO) is a fundamental electronic property. For this compound thin films, this transport gap is experimentally determined to be approximately 2.2 eV.[16][22]

-

Density of States (DOS): The DOS describes the number of available electronic states at each energy level. In disordered organic semiconductors, the DOS is not sharp but consists of band tails of localized states (traps) extending into the HOMO-LUMO gap.[23][24] A higher density of these trap states, often caused by structural disorder or impurities, degrades mobility and shifts the threshold voltage.[24][25] The DOS in this compound films is often modeled with a Gaussian distribution and an exponential tail.[23]

Quantitative Data Summary

The following tables summarize key quantitative reported in the literature.

Table 1: Reported Field-Effect Mobility (μ) in this compound OTFTs

| Mobility (cm²/Vs) | Substrate/Dielectric | Deposition Method | Key Conditions/Notes | Reference(s) |

|---|---|---|---|---|

| 8.85 | Barium Titanate | Thermal Evaporation | High-permittivity solution-processed dielectric. | [7] |

| 1.25 | OTS-treated SiO₂ | Neutral Cluster Beam Deposition | Room temperature deposition. | [21] |

| 1.10 | SiO₂ | Thermal Evaporation | Top gate, bottom contact geometry. | [10] |

| 0.7 | SiO₂ | Thermal Evaporation | Substrate held at elevated temperature. | [4] |

| 0.4 | Silicon Nitride | Thermal Evaporation | Inverted staggered transistor structure. | [5] |

| 0.38 | SiO₂ | Spin Coating (precursor) | Solution-processed from a this compound precursor. | [17] |

| 0.26 | SiO₂ | Thermal Evaporation | Studied over a temperature range of 300-450 K. | [6] |

| 0.038 | SiO₂ | Molecular Beam Deposition | Coexistence of thin-film and single-crystal phases. |[26] |

Table 2: Other Key Electrical Parameters for this compound OTFTs

| Parameter | Typical Value Range | Conditions / Notes | Reference(s) |

|---|---|---|---|

| On/Off Ratio | 10⁵ - 10⁸ | Highly dependent on gate leakage and off-current. | [4][6][10] |

| Threshold Voltage (Vth) | -2 V to -10 V | Sensitive to interface traps and processing conditions. | [6][10] |

| Contact Resistance (Rc) | 10⁶ - 10¹⁰ Ω | Gate bias dependent. |

| Width-Normalized Rc | 10 - 2000 Ω·cm | A more standardized metric for comparing contacts. |[12][13] |

Table 3: Fundamental Electronic Structure Parameters

| Parameter | Value | Measurement Technique | Reference(s) |

|---|---|---|---|

| HOMO-LUMO Gap | ~2.2 eV | STS, UPS/IPES | [16][22] |

| Ionization Energy (IE) | ~4.90 eV | UPS | [22] |

| Electron Affinity (EA) | ~2.70 eV | IPES | [22] |

| DOS Width (σ) | 0.07 ± 0.01 eV | Field-effect studies on treated substrates. |[23] |

Experimental Protocols and Characterization

A standard workflow for investigating the involves fabrication of a thin-film transistor followed by structural and electrical characterization.

Thin Film Deposition: Thermal Evaporation

-

Substrate Preparation: A heavily doped silicon wafer with a thermally grown silicon dioxide layer (e.g., 100-300 nm) is commonly used as the substrate and gate dielectric, respectively. The substrate is rigorously cleaned using a sequence of solvents (e.g., acetone, isopropanol) in an ultrasonic bath.[14]

-

SAM Treatment (Optional): To improve the dielectric interface, the cleaned SiO₂ surface can be treated with a SAM, such as OTS or hexamethyldisilazane (B44280) (HMDS).[9][21]

-

Deposition: The substrate is loaded into a high-vacuum chamber (base pressure < 5x10⁻⁶ Torr). This compound powder (purified by sublimation) is placed in a resistively heated crucible.[16] The substrate is often heated to a specific temperature (e.g., 65 °C).[9]

-

Process Control: The crucible is heated to sublimate the this compound, which deposits on the substrate. The deposition rate is monitored with a quartz crystal microbalance and typically controlled to be slow (e.g., 0.1 - 1 Å/s).[6][9] A final film thickness of 30-60 nm is common for TFT applications.[11]

Thin-Film Transistor (TFT) Fabrication

-

Device Structure: A common structure is the top-contact, bottom-gate configuration. The doped Si acts as the gate, SiO₂ as the dielectric, and the deposited this compound as the active layer.[27]

-

Electrode Deposition: Source and drain electrodes (typically 50 nm of Gold) are then thermally evaporated on top of the this compound film through a shadow mask.[9] The shadow mask defines the channel length (L) and channel width (W) of the transistor.

Structural Characterization

-

Atomic Force Microscopy (AFM): Performed in tapping mode to visualize the surface morphology of the this compound film. This provides direct information on the grain size, shape, and surface roughness.[14][16]

-

X-Ray Diffraction (XRD): Used in a Bragg-Brentano geometry to determine the crystalline structure and orientation of the molecules. The presence of sharp diffraction peaks corresponding to the (00l) planes confirms a high degree of molecular ordering with the long molecular axis oriented nearly perpendicular to the substrate.[5][14] The peak positions allow for identification of the crystalline phase (thin-film vs. bulk).[14]

Electrical Characterization

-

Measurement Setup: The completed TFT is placed in a probe station, often in an inert atmosphere or vacuum to prevent degradation. A semiconductor parameter analyzer is used to apply voltages and measure currents.

-

Output Characteristics: The drain current (ID) is measured as a function of the drain-source voltage (VDS) for several different gate voltages (VGS).

-

Transfer Characteristics: ID is measured as a function of VGS at a fixed, high VDS (saturation regime). This curve is used to extract the key device parameters.

-

Parameter Extraction:

-

Mobility (μ): In the saturation regime, mobility is calculated from the slope of the √|ID| vs. VGS plot using the standard MOSFET equation: ID = (W/2L) * μ * Ci * (VGS - Vth)² where Ci is the capacitance per unit area of the gate dielectric.

-

Threshold Voltage (Vth): Determined from the x-intercept of the linear fit to the √|ID| vs. VGS plot.

-

On/Off Ratio: The ratio of the maximum ID to the minimum ID from the transfer curve.

-

Charge Transport Mechanism

Charge transport in polycrystalline this compound films is generally described by a multiple trapping and release model or a hopping model.[5][19] Conduction is believed to be limited by the grain boundaries.

-

Intra-grain Transport: Within the well-ordered crystalline grains, charge carriers are relatively delocalized and transport is efficient, sometimes described as "band-like."[27]

-

Inter-grain Transport: To move from one grain to another, carriers must overcome an energy barrier at the grain boundary. This process, known as hopping, is thermally activated and is typically the rate-limiting step for overall conduction in the film.[5][19] The structural disorder and defects concentrated at these boundaries create localized trap states that can immobilize charge carriers, further impeding transport and reducing the effective mobility.[24] Therefore, maximizing grain size and improving the quality of the grain boundaries are key strategies for enhancing the electronic performance of this compound thin films.

Conclusion

The are a complex function of molecular-level packing, microscopic morphology, and device architecture. High charge carrier mobilities and excellent switching characteristics can be achieved through careful control of deposition conditions, particularly substrate temperature and deposition rate, and by engineering the semiconductor-dielectric interface with surface treatments. The performance is ultimately governed by the degree of crystalline order and the density of trap states, which are primarily associated with grain boundaries. A thorough understanding of these structure-property relationships, facilitated by detailed structural and electrical characterization, is essential for the continued development and application of this compound-based organic electronics.

References

- 1. Structure of this compound Monolayers on Amorphous Silicon Oxide and Relation to Charge Transport | Stanford Synchrotron Radiation Lightsource [www-ssrl.slac.stanford.edu]

- 2. This compound - Wikipedia [en.wikipedia.org]

- 3. researchgate.net [researchgate.net]

- 4. This compound organic thin-film transistors-molecular ordering and mobility | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 5. pubs.aip.org [pubs.aip.org]

- 6. cui.umn.edu [cui.umn.edu]

- 7. files01.core.ac.uk [files01.core.ac.uk]

- 8. Review of the Common Deposition Methods of Thin-Film this compound, Its Derivatives, and Their Performance - PMC [pmc.ncbi.nlm.nih.gov]

- 9. pubs.aip.org [pubs.aip.org]

- 10. Characteristics of this compound organic thin film transistor with top gate and bottom contact [cpsjournals.cn]

- 11. Contact resistance in this compound thin film transistors | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 12. pubs.aip.org [pubs.aip.org]

- 13. Contact resistance of organic TFTs [fkf.mpg.de]

- 14. beei.org [beei.org]

- 15. mdpi.com [mdpi.com]

- 16. aquila.infn.it [aquila.infn.it]

- 17. Solution processed high performance this compound thin-film transistors - Chemical Communications (RSC Publishing) [pubs.rsc.org]

- 18. Review of the Common Deposition Methods of Thin-Film this compound, Its Derivatives, and Their Performance - UCL Discovery [discovery.ucl.ac.uk]

- 19. researchgate.net [researchgate.net]

- 20. Effect of this compound–dielectric affinity on this compound thin film growth morphology in organic field-effect transistors - Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- 21. individual.utoronto.ca [individual.utoronto.ca]

- 22. pubs.aip.org [pubs.aip.org]

- 23. researchgate.net [researchgate.net]

- 24. spiedigitallibrary.org [spiedigitallibrary.org]

- 25. researchgate.net [researchgate.net]

- 26. pubs.acs.org [pubs.acs.org]

- 27. scispace.com [scispace.com]

An In-depth Technical Guide to the HOMO and LUMO Energy Levels of Pentacene

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides a comprehensive overview of the Highest Occupied Molecular Orbital (HOMO) and Lowest Unoccupied Molecular Orbital (LUMO) energy levels of pentacene, a key organic semiconductor. Understanding these fundamental electronic properties is crucial for the design and optimization of organic electronic devices and for assessing potential applications in drug development and bioelectronics. This document summarizes key quantitative data, details the experimental protocols for their determination, and visualizes the underlying processes.

Quantitative Data Summary

The HOMO and LUMO energy levels of this compound have been extensively studied through a variety of experimental and theoretical methods. The values can vary depending on the physical state of the this compound (gas phase, thin film, or single crystal), the substrate used, and the measurement technique. Below is a compilation of reported values.

| Measurement Technique | HOMO (eV) | LUMO (eV) | Energy Gap (eV) | Phase/Substrate | Reference |

| Experimental | |||||

| UPS / IPES | -4.90 ± 0.05 | -2.70 ± 0.03 | 2.20 ± 0.06 | Thin Film | [1][2] |

| UPS / STS | - | - | 2.35 | Thin Film on Cu(119) | [3] |

| PESA / UV-Vis | -5.49 | -3.74 | 1.75 | Thin Film on ITO | [4] |

| Cyclic Voltammetry (CV) | -5.4 | -3.53 | 1.87 | Solution (TIPS-Pentacene) | [5][6] |

| Photoelectron Yield Spectroscopy | -4.91 | - | - | 2D Thin Film | [7] |

| Anion Photoelectron Spectroscopy | - | -1.43 ± 0.03 (EA) | - | Gas Phase | [8][9] |

| Scanning Tunneling Spectroscopy (STS) | - | - | ~2.8 | On insulating layers | [10] |

| Theoretical | |||||

| DFT (B3LYP/6-311+G**) | - | - | 2.21 | - | [11] |

| DFT (B3LYP/6-31G(d)) | -5.11 | -2.65 | 2.46 | - | [12] |

| Semi-empirical (MNDO-PM3) | -7.88 | -2.17 | 5.71 | - | [13] |

Note: Ionization Potential (IP) is often used interchangeably with the negative of the HOMO energy, and Electron Affinity (EA) with the negative of the LUMO energy. The energy gap can be the fundamental gap (IP - EA) or the optical gap, which is typically smaller due to exciton (B1674681) binding energy.

Detailed Experimental Protocols

The accurate determination of this compound's HOMO and LUMO levels relies on sophisticated experimental techniques. Below are detailed methodologies for the key experiments cited.

Ultraviolet Photoelectron Spectroscopy (UPS)

UPS is a powerful technique for directly measuring the kinetic energy of photoelectrons emitted from a sample upon irradiation with ultraviolet light, allowing for the determination of the HOMO level.

Methodology:

-

Sample Preparation: this compound thin films are typically prepared by thermal evaporation in an ultra-high vacuum (UHV) chamber onto a conductive substrate, such as indium tin oxide (ITO) coated glass or a metal foil (e.g., Ag, Au).[4] The substrate is often cleaned by sputtering and annealing cycles to ensure a pristine surface. Film thickness is monitored using a quartz crystal microbalance. For single-crystal measurements, the crystal is cleaved in-situ to expose a clean surface.

-

Photon Source: A gas discharge lamp is commonly used, with the He I emission line (21.22 eV) being a standard choice for providing the UV photons.[14]

-

Energy Analyzer: A hemispherical electron energy analyzer is used to measure the kinetic energy distribution of the emitted photoelectrons. The overall energy resolution is typically better than 100 meV.[14]

-

Measurement Conditions: The experiment is conducted in UHV (base pressure < 1 x 10⁻⁹ mbar) to prevent contamination of the sample surface. A negative bias is often applied to the sample to overcome the work function of the analyzer and allow for the detection of the secondary electron cutoff, from which the vacuum level can be determined.

-

Data Analysis: The HOMO energy level is determined from the onset of the highest energy peak in the UPS spectrum, corresponding to the lowest binding energy. The ionization potential (IP) is calculated as the difference between the photon energy and the width of the energy distribution curve (from the Fermi edge to the secondary electron cutoff).

Inverse Photoemission Spectroscopy (IPES)

IPES is a technique complementary to UPS, used to probe the unoccupied electronic states, including the LUMO level.

Methodology:

-

Electron Source: A low-energy electron gun is used to direct a monochromatic beam of electrons onto the sample surface. To minimize radiation damage to the organic film, near-ultraviolet IPES (NUV-IPES) employs very low electron kinetic energies (e.g., 0-5 eV).[1]

-

Photon Detector: As electrons transition from the vacuum level into unoccupied states of the sample, they emit photons. These photons are detected by a photon detector, which can be a Geiger-Müller tube with a band-pass filter (isochromat mode) or a spectrometer. NUV-IPES often uses a series of band-pass filters to achieve better energy resolution (around 0.2-0.3 eV).[1]

-

Measurement Conditions: Similar to UPS, IPES is performed in a UHV environment.

-

Data Analysis: The LUMO energy level is determined from the onset of photon emission at the lowest electron kinetic energy. The electron affinity (EA) is the energy difference between the vacuum level and the LUMO level.

Cyclic Voltammetry (CV)

CV is an electrochemical technique that measures the current response of a solution containing the analyte to a linearly swept potential, providing information about its redox potentials, which can be used to estimate the HOMO and LUMO energy levels.

Methodology:

-

Electrochemical Cell: A standard three-electrode system is employed.[10] This consists of a working electrode (e.g., glassy carbon or platinum), a reference electrode (e.g., Ag/AgCl or a saturated calomel (B162337) electrode - SCE), and a counter electrode (e.g., a platinum wire).

-

Sample Preparation: The this compound derivative (often a more soluble form like TIPS-pentacene) is dissolved in a suitable organic solvent (e.g., dichloromethane (B109758) or acetonitrile) containing a supporting electrolyte (e.g., tetrabutylammonium (B224687) hexafluorophosphate (B91526) - TBAPF₆) to ensure conductivity.[5][6] The solution is deoxygenated by bubbling with an inert gas like nitrogen or argon.

-

Measurement Procedure: The potential of the working electrode is swept linearly from a starting potential to a vertex potential and then back. The resulting current between the working and counter electrodes is measured as a function of the applied potential.

-

Data Analysis: The onset potentials of the first oxidation (E_ox) and reduction (E_red) peaks in the cyclic voltammogram are determined. These are then used to calculate the HOMO and LUMO energy levels using empirical formulas that relate the potentials to the vacuum level, often by referencing to an internal standard like the ferrocene/ferrocenium (Fc/Fc⁺) redox couple.[5][6] The equations are typically of the form:

-

E_HOMO = -[E_ox (vs Fc/Fc⁺) + E_ref] eV

-

E_LUMO = -[E_red (vs Fc/Fc⁺) + E_ref] eV where E_ref is the absolute energy level of the Fc/Fc⁺ redox couple relative to the vacuum level (often taken as 4.8 eV or 5.1 eV).

-

Scanning Tunneling Spectroscopy (STS)

STS is a powerful technique that provides information about the local density of states (LDOS) of a surface with atomic resolution, allowing for the direct measurement of the HOMO-LUMO gap.

Methodology:

-

Sample Preparation: A sub-monolayer or monolayer of this compound is deposited on a conductive substrate, often a single crystal metal surface like Cu(119) or Ag(111), in a UHV chamber.[3] Sometimes, a thin insulating layer (e.g., NaCl) is grown on the metal substrate to electronically decouple the this compound molecules.

-

STM Setup: A sharp metallic tip (e.g., tungsten or Pt-Ir) is brought into close proximity (a few angstroms) to the sample surface. A bias voltage is applied between the tip and the sample, inducing a quantum mechanical tunneling current.

-

Spectroscopy Mode: The STM tip is positioned over a single this compound molecule. The feedback loop that maintains a constant current is temporarily disabled, and the bias voltage is swept while the tunneling current is recorded, generating an I-V curve. The differential conductance (dI/dV) is then calculated, which is proportional to the LDOS of the sample.

-

Data Analysis: The dI/dV spectrum shows peaks corresponding to the energies of the molecular orbitals. The onset of the first peak at negative sample bias corresponds to the HOMO level, and the onset of the first peak at positive sample bias corresponds to the LUMO level. The energy difference between these two onsets provides a direct measure of the HOMO-LUMO gap.[3]

Mandatory Visualizations

Energy Level Diagram

Caption: A generalized energy level diagram for this compound.

Experimental Workflow: UPS & IPES

Caption: Workflow for HOMO and LUMO determination using UPS and IPES.

Experimental Workflow: Cyclic Voltammetry (CV)

Caption: Workflow for HOMO and LUMO estimation using Cyclic Voltammetry.

Experimental Workflow: Scanning Tunneling Spectroscopy (STS)

Caption: Workflow for measuring the HOMO-LUMO gap using STS.

References

- 1. pubs.aip.org [pubs.aip.org]

- 2. researchgate.net [researchgate.net]

- 3. pubs.aip.org [pubs.aip.org]

- 4. This compound Thin Film by Compact Thermal Evaporation System | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 5. researchgate.net [researchgate.net]

- 6. pubs.rsc.org [pubs.rsc.org]

- 7. pubs.acs.org [pubs.acs.org]

- 8. pubs.aip.org [pubs.aip.org]

- 9. researchgate.net [researchgate.net]

- 10. benchchem.com [benchchem.com]

- 11. This compound [chm.bris.ac.uk]

- 12. researchgate.net [researchgate.net]

- 13. researchgate.net [researchgate.net]

- 14. researchgate.net [researchgate.net]

The Key to Unlocking High-Performance Organic Electronics: A Technical Guide to the Solubility and Processing of Pentacene Derivatives

For Researchers, Scientists, and Drug Development Professionals

Pentacene, a polycyclic aromatic hydrocarbon, has long been a benchmark material in organic electronics due to its exceptional charge transport properties. However, its practical application has been historically hindered by poor solubility in common organic solvents, making large-area, solution-based fabrication challenging. The advent of functionalized this compound derivatives has revolutionized the field, offering enhanced solubility and processability without compromising electronic performance. This technical guide provides an in-depth exploration of the solubility and processing of these advanced materials, offering a comprehensive resource for researchers and professionals in the field.

Enhancing Solubility: The Role of Functionalization

The core strategy for improving the solubility of this compound involves the introduction of various side chains to the this compound backbone. These functional groups disrupt the strong intermolecular π-π stacking that leads to high lattice energy and low solubility in the parent molecule.[1][2]

Trialkylsilylethynyl Functionalization

One of the most successful approaches has been the substitution with trialkylsilylethynyl groups, most notably the triisopropylsilylethynyl (TIPS) group.[2][3] The bulky TIPS moieties, held away from the aromatic core by a rigid ethynyl (B1212043) spacer, effectively prevent the herringbone packing characteristic of unsubstituted this compound and promote a face-to-face π-stacking arrangement, which is beneficial for charge transport.[1][2][3] This functionalization dramatically increases solubility in common organic solvents like toluene, chlorobenzene, and tetrahydrofuran (B95107) (THF).[1][4]

Other Functionalization Strategies

Beyond TIPS, various other functional groups have been explored to modulate solubility and electronic properties:

-

Dioxolane Groups: Functionalization with dioxolane units perpendicular to the this compound plane yields derivatives that are both stable and soluble. For instance, a butyl-substituted dioxolane this compound derivative exhibits a remarkable solubility of up to 100 mg/mL in toluene.[5]

-

Alkyl Chains: The length of alkyl side chains systematically influences the thermal behavior, crystal packing, and macroscopic properties of functionalized pentacenes.[1]

-

Electron-Withdrawing Groups: The addition of electron-withdrawing groups, such as nitrile (CN) groups, can convert p-type TIPS-pentacene into an n-type material, suitable for use as an acceptor in organic solar cells.[6]

The following diagram illustrates the impact of functionalization on this compound's properties.

Caption: Functionalization transforms this compound's properties.

Quantitative Solubility Data

The solubility of this compound derivatives is highly dependent on the nature of the functional group and the choice of solvent. The following table summarizes available quantitative solubility data for select derivatives.

| This compound Derivative | Solvent | Solubility | Reference |

| Butyl-substituted dioxolane this compound | Toluene | up to 100 mg/mL | [5] |

| Cyclopentylidine-substituted dioxolane this compound | Chlorobenzene | Sparingly soluble (hot) | [5] |

| 6,13-Bis(triisopropylsilylethynyl)this compound (TIPS-pentacene) | Most organic solvents | Very soluble | [2][3] |

Solution-Processing Techniques for this compound Derivatives

The enhanced solubility of this compound derivatives enables a variety of solution-based deposition techniques, which are crucial for the low-cost, large-area fabrication of electronic devices.[7] The choice of deposition method significantly influences the morphology and crystallinity of the resulting thin film, and consequently, the device performance.[7][8]

Common solution-processing techniques include:

-

Spin-Coating: A widely used method for achieving uniform thin films over large areas.[7]

-

Drop-Casting: A simple technique that can produce highly crystalline films when the solvent evaporation rate is carefully controlled.[3][7]

-

Blade-Coating/Solution-Shearing: These techniques involve shearing a solution of the material across a substrate, which can lead to highly aligned, single-crystalline films with excellent and consistent device performance.[7][9]

The general workflow for fabricating an Organic Thin-Film Transistor (OTFT) using a solution-processed this compound derivative is depicted below.

Caption: OTFT fabrication workflow.

Experimental Protocols

Detailed and reproducible experimental protocols are critical for achieving high-performance devices. The following sections provide methodologies for key experimental procedures.

Synthesis of a Soluble this compound Derivative (A General Example)

The synthesis of functionalized pentacenes often involves the reaction of a pentacenequinone precursor with an appropriate organometallic reagent. For example, bis(triisopropylsilylethynyl)this compound can be prepared in a one-pot reaction from 6,13-pentacenequinone.[2] A general, simplified synthesis route is as follows:

-

Reaction Setup: In a flame-dried, multi-neck round-bottom flask under an inert atmosphere (e.g., argon or nitrogen), dissolve the pentacenequinone precursor in an appropriate anhydrous solvent (e.g., THF).

-

Reagent Addition: Slowly add the organometallic reagent (e.g., a lithium acetylide solution) to the reaction mixture at a controlled temperature (e.g., -78 °C using a dry ice/acetone bath).

-

Reaction: Allow the reaction to stir at the controlled temperature for a specified time, then slowly warm to room temperature and stir for several hours or overnight.

-

Quenching and Extraction: Quench the reaction with a suitable reagent (e.g., saturated ammonium (B1175870) chloride solution). Extract the organic product into an appropriate solvent (e.g., ethyl acetate). Wash the organic layer with water and brine.

-

Drying and Purification: Dry the organic layer over an anhydrous salt (e.g., MgSO₄), filter, and concentrate the solvent under reduced pressure. Purify the crude product by column chromatography on silica (B1680970) gel using a suitable eluent system (e.g., a mixture of hexanes and ethyl acetate).

-

Characterization: Characterize the final product using techniques such as NMR spectroscopy, mass spectrometry, and UV-Vis spectroscopy.

Thin-Film Deposition via Spin-Coating

-

Solution Preparation: Prepare a solution of the this compound derivative in a suitable solvent (e.g., toluene, chloroform) at a specific concentration (e.g., 10 mg/mL). The solution may be heated to ensure complete dissolution.[3]

-

Substrate Preparation: Clean the substrates (e.g., Si/SiO₂) by sonicating in a series of solvents (e.g., acetone, isopropanol) and then treat with an oxygen plasma or UV-Ozone to remove organic residues. For improved film morphology, the substrate surface can be treated with a self-assembled monolayer (SAM) such as hexamethyldisilazane (B44280) (HMDS) or octadecyltrichlorosilane (B89594) (OTS).[8]

-

Spin-Coating: Dispense the solution onto the center of the substrate. Spin the substrate at a specific speed (e.g., 1500 rpm) for a set duration (e.g., 60 seconds) to create a thin film. The thickness of the film can be controlled by varying the solution concentration and spin speed.

-

Thermal Annealing (Optional): To improve the crystallinity and morphology of the film, the substrate can be annealed on a hot plate at a specific temperature (e.g., 120-150 °C) for a certain time in an inert atmosphere (e.g., a nitrogen-filled glovebox).[10]

Thin-Film Characterization

The performance of this compound-based devices is critically dependent on the morphology of the thin film.[8] Key characterization techniques include:

-

Atomic Force Microscopy (AFM): Used to investigate the surface morphology, grain size, and roughness of the thin film.[8]

-

X-ray Diffraction (XRD): Provides information on the crystal structure, molecular packing, and orientation of the molecules in the film.[1]

-

UV-Vis Spectroscopy: Used to study the electronic absorption properties and can also be used to monitor the stability of the this compound derivative in solution.[1][11]

The logical relationship between molecular design, processing, and final device performance is summarized in the diagram below.

Caption: From molecule to device.

Conclusion

The development of soluble this compound derivatives has been a pivotal advancement in the field of organic electronics. By strategically functionalizing the this compound core, researchers have overcome the long-standing challenge of processability, paving the way for the fabrication of high-performance, large-area, and flexible electronic devices through solution-based techniques. This guide has provided a comprehensive overview of the key aspects of solubility and processing, from the molecular design principles to detailed experimental considerations. A thorough understanding and control of these factors are essential for unlocking the full potential of this compound-based materials in next-generation electronic applications.

References

- 1. The influence of side chains on the structures and properties of functionalized pentacenes - Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- 2. pubs.acs.org [pubs.acs.org]

- 3. ossila.com [ossila.com]

- 4. scholars.uky.edu [scholars.uky.edu]

- 5. A new functionalization strategy for this compound - Chemical Communications (RSC Publishing) [pubs.rsc.org]

- 6. researchgate.net [researchgate.net]

- 7. benchchem.com [benchchem.com]

- 8. benchchem.com [benchchem.com]

- 9. researchgate.net [researchgate.net]

- 10. researchgate.net [researchgate.net]

- 11. Synthesis, stability and electrical properties of new soluble pentacenes with unsaturated side groups - RSC Advances (RSC Publishing) [pubs.rsc.org]

The Advent of a Molecular Semiconductor: A Technical History of Pentacene

An In-depth Guide for Researchers, Scientists, and Drug Development Professionals

From its initial synthesis in the early 20th century to its establishment as a benchmark organic semiconductor, pentacene has traversed a remarkable journey, captivating the attention of chemists, physicists, and materials scientists alike. This technical guide delves into the history and discovery of this compound's semiconducting properties, providing a comprehensive overview of the key milestones, experimental methodologies, and the evolution of its performance as a cornerstone material in organic electronics.

A Century of Discovery: From Synthesis to Semiconductor

This compound (C₂₂H₁₄), a polycyclic aromatic hydrocarbon composed of five linearly fused benzene (B151609) rings, was first synthesized in 1912.[1] However, its potential as a semiconductor remained largely unexplored for several decades. The mid-20th century saw a burgeoning interest in the electronic properties of organic materials, with researchers like H. Akamatu and H. Inokuchi investigating the conductivity of various polycyclic aromatic hydrocarbons.[2]

It was not until the 1990s that this compound's exceptional semiconducting properties were fully realized and harnessed in electronic devices. The development of the organic field-effect transistor (OFET) provided a platform to rigorously characterize its performance. Researchers such as G. Horowitz and C. D. Dimitrakopoulos were instrumental in demonstrating the high charge carrier mobility of this compound thin films, catapulting it to the forefront of organic electronics research.[3][4]

Key Milestones in this compound Semiconductor Research

The journey of this compound from a laboratory curiosity to a benchmark organic semiconductor is marked by several crucial discoveries and technological advancements. The following diagram illustrates the logical and historical progression of this research.

Quantitative Performance Evolution of this compound-Based OFETs

The performance of this compound-based OFETs has seen a dramatic improvement since their inception. The following tables summarize key performance metrics from seminal and representative studies, showcasing the progress in achieving higher mobility and better device characteristics.

| Early this compound OFET Performance (1990s) | |||

| Reference | Mobility (cm²/Vs) | On/Off Ratio | Substrate/Dielectric |

| G. Horowitz et al. (1998)[3] | ~0.03 | >10⁵ | Si/SiO₂ |

| C. D. Dimitrakopoulos et al. (1996)[4] | ~0.1 | ~10⁶ | Si/SiO₂ |

| High-Performance this compound OFETs (2000s - Present) | |||

| Reference | Mobility (cm²/Vs) | On/Off Ratio | Substrate/Dielectric |

| Lin et al. (1997)[5] | 1.5 | 10⁸ | Doped Si/SiO₂ |

| Kymissis et al. (2001)[6] | 2.7 (single crystal) | >10⁶ | Doped Si/SiO₂ |

| Kelley et al. (2003) | 3.0 | 10⁶ | Plastic/PVP |

| Yasuda et al. (2005) | 5.5 | 10⁶ | Glass/Ta₂O₅ |

Experimental Protocols: From Crystal Growth to Device Characterization

The characterization of this compound as a semiconductor involves a series of sophisticated experimental techniques. This section details the methodologies for key experiments cited in the literature.

This compound Purification and Crystal Growth

Early studies and high-performance devices rely on high-purity this compound. A common purification method is temperature-gradient sublimation .

Experimental Workflow for Temperature-Gradient Sublimation:

Fabrication of this compound Thin-Film Transistors

The fabrication of a typical bottom-gate, top-contact this compound OFET involves the following steps:

Experimental Protocol for OFET Fabrication:

-

Substrate Preparation: A heavily doped silicon wafer (serving as the gate electrode) with a thermally grown silicon dioxide (SiO₂) layer (gate dielectric) is cleaned using a standard RCA cleaning procedure.

-

Surface Treatment (Optional but Recommended): The SiO₂ surface is often treated with a self-assembled monolayer (SAM) such as octadecyltrichlorosilane (B89594) (OTS) to improve the this compound film growth and device performance. This is typically done by immersing the substrate in a dilute solution of OTS in an anhydrous solvent (e.g., toluene (B28343) or hexane) for a specified time, followed by rinsing and annealing.

-

This compound Deposition: A thin film of purified this compound (typically 30-60 nm) is deposited onto the substrate via thermal evaporation in a high-vacuum chamber (pressure < 10⁻⁶ Torr). The substrate is often held at an elevated temperature (e.g., 60-70°C) during deposition to promote the growth of larger crystalline grains. The deposition rate is carefully controlled, typically around 0.1-0.5 Å/s.

-

Source and Drain Electrode Deposition: Gold (Au) is commonly used for the source and drain electrodes due to its high work function, which facilitates hole injection into the highest occupied molecular orbital (HOMO) of this compound. The electrodes are deposited through a shadow mask by thermal evaporation to define the channel length (L) and width (W) of the transistor.

Electrical Characterization of this compound OFETs

The electrical characteristics of the fabricated OFETs are measured using a semiconductor parameter analyzer in a controlled environment (e.g., in a vacuum or an inert atmosphere) to minimize degradation due to oxygen and moisture.

Key Measurements and Parameter Extraction:

-

Output Characteristics (IDS vs. VDS): The drain current (IDS) is measured as a function of the drain-source voltage (VDS) for various gate-source voltages (VGS). These curves show the typical linear and saturation regimes of a field-effect transistor.

-

Transfer Characteristics (IDS vs. VGS): The drain current is measured as a function of the gate-source voltage at a constant (and typically high) drain-source voltage.

From the transfer characteristics in the saturation regime, the field-effect mobility (µ) can be calculated using the following equation:

IDS = (W / 2L) * Ci * µ * (VGS - Vth)²

where:

-

W is the channel width

-

L is the channel length

-

Ci is the capacitance per unit area of the gate dielectric

-

Vth is the threshold voltage

The on/off ratio is determined by taking the ratio of the maximum drain current (on-state) to the minimum drain current (off-state) from the transfer curve.

Conclusion

The history of this compound as a semiconductor is a testament to the continuous exploration and understanding of organic materials for electronic applications. From its initial synthesis to its current status as a benchmark material, the journey of this compound has been driven by advancements in material purification, thin-film deposition techniques, and device engineering. The detailed experimental protocols and the evolution of its performance metrics provide a valuable resource for researchers and scientists working at the forefront of organic electronics and related fields. The ongoing development of soluble this compound derivatives and their integration into flexible and large-area electronics promises to continue the legacy of this remarkable molecule.

References

Unveiling the Engine of Organic Electronics: A Technical Guide to Charge Transport in Pentacene

For Researchers, Scientists, and Drug Development Professionals

Pentacene, a polycyclic aromatic hydrocarbon, stands as a benchmark material in the field of organic electronics. Its remarkable charge-carrying capabilities have fueled the development of a wide array of novel technologies, from flexible displays to advanced biosensors. A profound understanding of the fundamental mechanisms governing charge transport within this material is paramount for the continued innovation and optimization of these technologies. This technical guide provides an in-depth exploration of the core principles of charge transport in this compound, offering a comprehensive resource for researchers and professionals working at the forefront of organic electronics and related disciplines.

The Dichotomy of Charge Transport: Band-like vs. Hopping Mechanisms

Charge transport in organic molecular crystals like this compound is a complex phenomenon that cannot be described by a single, universal model. Instead, it is understood as a balance, or often a transition, between two primary mechanisms: band-like transport and hopping transport.

Band-like transport , prevalent in highly ordered single crystals at low temperatures, is analogous to charge movement in traditional inorganic semiconductors. In this regime, the strong intermolecular coupling between this compound molecules leads to the formation of delocalized electronic bands. Charge carriers (holes, in the case of p-type this compound) are delocalized over several molecular units and move coherently through the crystal lattice. A key characteristic of band-like transport is a decrease in charge carrier mobility with increasing temperature, following a power-law dependence (μ ∝ T-n). This is attributed to increased scattering of the charge carriers by lattice vibrations (phonons).

Hopping transport , on the other hand, dominates in disordered systems such as polycrystalline thin films and at higher temperatures. In this scenario, charge carriers are localized on individual this compound molecules due to structural and energetic disorder. Transport occurs through a series of incoherent "hops" between adjacent localized states. This process is thermally activated, meaning that the charge carrier requires thermal energy to overcome the potential barrier between molecules. Consequently, a hallmark of hopping transport is an increase in mobility with temperature.

An unusual increase in the Seebeck coefficient with increasing charge carrier density has been observed in this compound thin-film transistors, which is interpreted as a transition from hopping transport to band-like transport at temperatures below approximately 250 K.[1] In some cases, a transition from thermally activated to temperature-independent conduction is observed.[2]

The Critical Role of Molecular Vibrations: Electron-Phonon Coupling

The interaction between charge carriers and the vibrational modes of the this compound lattice, known as electron-phonon coupling, is a decisive factor in determining the dominant transport mechanism and the overall charge carrier mobility. These vibrations can be broadly categorized as intramolecular (vibrations within a single this compound molecule) and intermolecular (vibrations between adjacent molecules).

Low-frequency intermolecular phonons, in particular, play a pivotal role.[3] These vibrations dynamically modulate the intermolecular transfer integrals, which are a measure of the electronic coupling strength between neighboring molecules.[2][4] Large fluctuations in these integrals, often of the same order of magnitude as their average values, can lead to a phenomenon known as transient localization .[2][4] Here, the charge carrier becomes momentarily localized on a timescale shorter than the characteristic period of the molecular motions, effectively blurring the lines between pure band-like and hopping transport. Terahertz transient conductivity measurements have directly demonstrated a strong coupling of charge carriers to low-frequency molecular motions centered around 1.1 THz in this compound single crystals.[5][6]

Theoretical Frameworks: Holstein Polaron and Transient Localization Theory

Two prominent theoretical models provide a framework for understanding the interplay of charge carriers and phonons in this compound:

-

The Holstein Polaron Model: This model describes a charge carrier that is "dressed" by a cloud of surrounding lattice distortions (phonons). This composite quasiparticle, known as a polaron, has a higher effective mass than a bare charge carrier. In the context of this compound, the interaction is primarily with high-frequency intramolecular vibrations. The strength of the electron-phonon coupling determines the size and nature of the polaron. In the strong coupling limit, small polarons are formed, and transport occurs via thermally activated hopping. In the weak coupling limit, large polarons can move more coherently in a band-like fashion. The formation of polarons is a key concept in understanding charge transport in many organic semiconductors.[7][8][9][10]

-

Transient Localization Theory (TLT): This theory provides a more nuanced picture that is particularly relevant for high-mobility organic crystals like this compound. TLT posits that the dynamic disorder caused by low-frequency intermolecular vibrations leads to a transient localization of the electronic wavefunction.[11] The mobility in this model is related to the time-averaged squared localization length of the charge carrier.[12] This framework successfully explains the observation of band-like temperature dependence of mobility even when the calculated mean free path of the carriers is on the order of the intermolecular distance, a situation where traditional band theory breaks down.[5]

The Influence of Material Structure: Single Crystals vs. Polycrystalline Thin Films

The physical structure of the this compound material has a profound impact on its charge transport properties.

-

Single Crystals: High-purity single crystals of this compound represent the ideal system for achieving high charge carrier mobility. The long-range molecular order minimizes defects and maximizes intermolecular electronic coupling, facilitating efficient band-like transport. Room temperature hole mobilities in single-crystal this compound can be as high as 35 cm²/Vs, increasing to 58 cm²/Vs at 225 K.[4][7][13][14][15]

-

Polycrystalline Thin Films: In contrast, thin films, which are more relevant for practical device applications, are typically polycrystalline. These films consist of small crystalline grains separated by disordered regions known as grain boundaries . These grain boundaries act as significant impediments to charge transport.[16][17] They introduce structural and energetic disorder, creating trapping sites and potential barriers that hinder the movement of charge carriers between grains.[16][17] Consequently, the mobility in polycrystalline this compound films is generally one to two orders of magnitude lower than in single crystals.[16] The mobility in these films is often limited by trap-limited transport, with a clear dependence on the grain size.[14][16] Transistors based on single-crystal this compound have exhibited hole mobilities up to 2 cm²/Vs, which is approximately an order of magnitude higher than devices using polycrystalline this compound.[16]

Quantitative Data on Charge Transport Parameters

The following tables summarize key quantitative data for charge transport in this compound, compiled from various studies.

| Parameter | Single Crystal | Polycrystalline Thin Film | Units | References |

| Hole Mobility (Room Temp.) | 1 - 35 | 0.1 - 1.5 | cm²/Vs | [4],[16],[3],[13],[14],[15],[7] |

| Temperature Dependence | μ ∝ T-n (band-like) | Thermally Activated (hopping) | - | [4],[3],[13],[14],[15],[7] |

Table 1: Comparison of Hole Mobility in Single Crystal and Polycrystalline this compound.

| Temperature (K) | Hole Mobility (cm²/Vs) | Material Form |

| 300 | 0.26 | Thin Film |

| 350 | ~0.35 (peak) | Thin Film |

| 450 | ~0.1 | Thin Film |

| 300 | 35 | Single Crystal |

| 225 | 58 | Single Crystal |

Table 2: Temperature Dependence of Hole Mobility in this compound. [3][4][7][13][14][15]

| Parameter | Value | Units | Notes | References |

| Activation Energy (Hopping) | 26 - 100 | meV | Varies with gate voltage and material purity. | [18],[17],[19] |

| Intermolecular Transfer Integral | 50 - 150 | meV | Fluctuations can be of the same order of magnitude as the average value. | [4],[2],[20],[21] |

| Electron-Phonon Coupling Strength (λ) | ~0.4 | dimensionless | Indicates significant coupling. |

Table 3: Key Charge Transport Parameters in this compound.

Experimental Protocols for Characterizing Charge Transport

A variety of experimental techniques are employed to measure the charge carrier mobility and elucidate the transport mechanisms in this compound.

Time-of-Flight (TOF) Photocurrent Measurements

The Time-of-Flight (TOF) technique is a direct method for measuring the drift mobility of charge carriers perpendicular to the sample surface.

Methodology:

-

Sample Preparation: A thick film (typically > 1 µm) of this compound is sandwiched between two electrodes, with at least one being semi-transparent.

-

Carrier Generation: A short laser pulse with a photon energy greater than the bandgap of this compound is directed through the semi-transparent electrode, creating a sheet of electron-hole pairs near this electrode.

-

Carrier Drift: An external electric field is applied across the sample, causing either electrons or holes (depending on the polarity of the field) to drift towards the opposite electrode.

-

Current Measurement: The transient photocurrent generated by the moving charge carriers is measured as a function of time using an oscilloscope.

-

Data Analysis: The transit time (tT) of the charge carriers across the film of thickness (d) is determined from the photocurrent transient. The mobility (μ) is then calculated using the formula: μ = d² / (V * tT), where V is the applied voltage.

Space-Charge-Limited Current (SCLC) Spectroscopy

The Space-Charge-Limited Current (SCLC) method is used to determine the charge carrier mobility from the current-voltage (I-V) characteristics of a device when the injected charge density exceeds the intrinsic charge density.

Methodology:

-

Device Fabrication: A this compound film is sandwiched between two electrodes, forming a diode-like structure. It is crucial to have an ohmic contact at the injecting electrode to ensure that the current is not injection-limited.

-

I-V Measurement: The current density (J) is measured as a function of the applied voltage (V).

-

Data Analysis: In the SCLC regime, the current is dominated by the injected space charge and follows the Mott-Gurney law: J = (9/8) * εr * ε0 * μ * (V²/d³), where εr is the dielectric constant of this compound, ε0 is the permittivity of free space, μ is the mobility, and d is the film thickness. The mobility can be extracted from the slope of a plot of J vs. V².

Kelvin Probe Force Microscopy (KPFM)

Kelvin Probe Force Microscopy (KPFM) is a powerful scanning probe technique that maps the surface potential of a material with high spatial resolution. In the context of this compound transistors, it can be used to visualize potential drops at grain boundaries and contacts, providing insights into local transport properties.

Methodology:

-

Device Operation: The this compound-based device, typically a field-effect transistor, is operated under the desired bias conditions.

-

AFM Topography: An Atomic Force Microscope (AFM) is used to obtain a topographical image of the this compound surface in tapping or non-contact mode.

-

Surface Potential Mapping: In lift mode, the AFM tip is scanned at a constant height above the surface. An AC voltage is applied to the tip, and a DC bias is adjusted to nullify the electrostatic force between the tip and the sample. This DC bias is equal to the local surface potential.

-

Data Correlation: The obtained surface potential map is correlated with the topography to identify potential variations across grains and at grain boundaries. This allows for the direct visualization of potential barriers that impede charge transport.

Visualizing Charge Transport Concepts

The following diagrams, generated using the DOT language, illustrate key concepts in this compound charge transport.

Caption: Coherent movement of a delocalized charge carrier through an ordered molecular lattice.

Caption: Incoherent hopping of a localized charge carrier between discrete states.

Caption: Dynamic disorder leads to transient localization of charge carriers.

Caption: Workflow for Time-of-Flight mobility measurement.

Conclusion

The charge transport properties of this compound are a rich and multifaceted area of study, governed by a delicate interplay between molecular packing, dynamic lattice vibrations, and the degree of structural order. While band-like transport in single crystals gives rise to exceptionally high mobilities, the hopping mechanism, often limited by grain boundaries, is more representative of practical thin-film devices. A comprehensive understanding of these fundamental mechanisms, supported by robust theoretical models and precise experimental characterization, is essential for the rational design of next-generation organic electronic materials and devices with enhanced performance and reliability. This guide serves as a foundational resource for professionals dedicated to advancing this exciting field.

References

- 1. Electron-phonon coupling spectrum in photodoped this compound crystals - PubMed [pubmed.ncbi.nlm.nih.gov]

- 2. pubs.acs.org [pubs.acs.org]

- 3. cui.umn.edu [cui.umn.edu]

- 4. pubs.acs.org [pubs.acs.org]

- 5. dr.ntu.edu.sg [dr.ntu.edu.sg]

- 6. [1010.2893] Transient localization in crystalline organic semiconductors [arxiv.org]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- 9. researchgate.net [researchgate.net]

- 10. arxiv.org [arxiv.org]

- 11. Quantum localization and delocalization of charge carriers in organic semiconducting crystals - PMC [pmc.ncbi.nlm.nih.gov]

- 12. discovery.ucl.ac.uk [discovery.ucl.ac.uk]

- 13. researchgate.net [researchgate.net]

- 14. files01.core.ac.uk [files01.core.ac.uk]

- 15. mdpi.com [mdpi.com]

- 16. researchgate.net [researchgate.net]

- 17. pubs.aip.org [pubs.aip.org]

- 18. researchgate.net [researchgate.net]

- 19. researchgate.net [researchgate.net]

- 20. Revisiting the Charge-Transfer States at this compound/C60 Interfaces with the GW/Bethe–Salpeter Equation Approach - PMC [pmc.ncbi.nlm.nih.gov]

- 21. [PDF] Electron-phonon coupling in crystalline this compound films. | Semantic Scholar [semanticscholar.org]

An In-depth Technical Guide to the Molecular Structure and Bonding of Pentacene

For Researchers, Scientists, and Drug Development Professionals

Abstract

Pentacene (C₂₂H₁₄) is a polycyclic aromatic hydrocarbon composed of five linearly-fused benzene (B151609) rings.[1] This highly conjugated system is a p-type organic semiconductor, making it a subject of intense research for applications in organic electronics.[2] Its planar molecular structure and crystalline packing significantly influence its electronic properties. This guide provides a comprehensive overview of the molecular structure, chemical bonding, and key characterization methodologies for this compound, tailored for professionals in research and development.

Molecular Structure and Bonding

This compound consists of five ortho-fused benzene rings in a rectilinear arrangement, forming a planar, rigid molecule.[3][4] The molecule is composed of 22 carbon atoms and 14 hydrogen atoms.[1] In the gas phase, an isolated this compound molecule exhibits a flat, two-dimensional geometry.[3] The overall length of the molecule is approximately 14 Å.[2]

The bonding within this compound is characterized by a delocalized π-electron system, with each carbon atom contributing one p-electron.[2] This extensive conjugation is responsible for its semiconductor properties. The carbon-carbon (C-C) bond lengths in this compound are not uniform and have been determined to range from 1.381 Å to 1.464 Å.[2] In the crystalline state, this compound molecules exhibit a herringbone packing motif.[5] This arrangement is influenced by π-stacking interactions, where the offset orientation of the this compound cores is attributed to increased overlap of monomer molecular orbitals and a reduction in two-orbital-four-electron repulsions.[6]

Visualization of Molecular Structure

The logical relationship of the fused aromatic rings in this compound can be visualized as follows:

Caption: Logical relationship of the five fused benzene rings in the this compound molecule.

Quantitative Molecular Data

The following tables summarize key quantitative data regarding the molecular and electronic structure of this compound.

Table 1: Molecular Properties of this compound

| Property | Value |

| Chemical Formula | C₂₂H₁₄[1] |

| Molar Mass | 278.354 g·mol⁻¹[1] |

| Molecular Length | ~14 Å[2] |

| C-C Bond Length Range | 1.381 - 1.464 Å[2] |

Table 2: Electronic Properties of this compound

| Parameter | Method | Value (eV) |

| HOMO-LUMO Gap | ||

| UV-visible Spectroscopy | 1.75[7] | |

| Theoretical (DFT) | 2.21[2] | |

| Scanning Tunneling Spectroscopy (on insulating layers) | ~2.8[8] | |

| Theoretical (DFT - B3LYP) | 2.17[8] | |

| Theoretical (DFT - Self-consistent field) | 1.64[8][9] | |

| Theoretical (DFT - Kohn-Sham eigenvalue differences) | ~1.1[8][9] | |

| HOMO Energy Level | Photoelectron Spectroscopy in Atmosphere (PESA) | -5.49[7] |

| LUMO Energy Level | Photoelectron Spectroscopy in Atmosphere (PESA) | -3.74[7] |

Experimental Protocols

Detailed methodologies for the synthesis and characterization of this compound are crucial for reproducible research.

Synthesis of this compound

A common and improved synthesis method for this compound proceeds via the formation of this compound-6,13-dione.[10]

Step 1: Synthesis of this compound-6,13-dione [10]

-

Dissolve o-phthalaldehyde (B127526) (10 g, 74.6 mmol) and 1,4-cyclohexanedione (B43130) (4.18 g, 37.3 mmol) in ethanol (B145695) (460 mL) under a nitrogen atmosphere.

-

Slowly add aqueous NaOH (10%, 5.96 g, 149 mmol) to the solution. The solution will change color from yellow to golden brown, then to dark brown, before a yellow solid precipitates.

-

Stir the reaction mixture for four hours.

-

Filter the crude reaction mixture and wash the solid with ethanol, water, and methanol (B129727) until the washings are colorless.

-

Dry the solid residue under vacuum to obtain bright yellow this compound-6,13-dione. The typical yield is around 96%.

Step 2: Reduction to 6,13-Dihydro-6,13-dihydroxythis compound and subsequent conversion to this compound [10]

-

This compound-6,13-dione can be reduced to 6,13-dihydro-6,13-dihydroxythis compound.

-

The subsequent reduction of 6,13-dihydro-6,13-dihydroxythis compound to this compound can be achieved using SnCl₂/HCl in a suitable solvent like DMF. This reaction is typically fast (1-2 minutes) and results in high yields (≥90%).

Characterization of this compound Thin Films

The structural and optical properties of this compound thin films are commonly investigated using various analytical techniques.

-

Substrate Preparation: Use substrates such as Si/SiO₂ or glass. Clean the substrates sequentially with acetone (B3395972) and isopropanol. Further treat with a UV-Ozone cleaner to remove organic residues.

-

Deposition: Place the purified this compound powder in a low-temperature evaporation source (e.g., a Knudsen cell) within a high-vacuum chamber (pressure < 5 x 10⁻⁶ mbar).

-

Heat the source to sublime the this compound. The deposition rate is typically controlled to be around 0.2–0.3 Å s⁻¹.

-

The substrate can be held at room temperature or heated (e.g., to 70 °C) to influence film morphology.

-

Deposit the film to the desired thickness (e.g., 50 nm).

-

Cool the substrate and source to room temperature before venting the chamber.

Caption: Experimental workflow for the characterization of this compound thin films.

X-Ray Diffraction (XRD): XRD is used to examine the structural properties of the this compound thin film, such as the orientation of the crystalline domains.[7] For instance, XRD analysis can reveal if the thin films are oriented along a specific plane direction, like the (001) plane.[7]

Atomic Force Microscopy (AFM): AFM is employed to visualize the surface morphology and topology of the this compound thin films.[11]

-

Imaging: Use a suitable cantilever in tapping mode to avoid damaging the soft organic film.

-

Data Analysis: Analyze the AFM images to determine parameters like root-mean-square (RMS) roughness and the size and distribution of crystalline grains.[12]

UV-visible (UV-Vis) Spectroscopy: This technique is used to evaluate the optical properties of the this compound thin film.[7]

-

A solution of the this compound sample is prepared in a suitable solvent.

-

The absorption spectrum is recorded using a spectrophotometer.

-

The optical bandgap can be determined from the onset of the lowest energy absorption band.[8]

Photoelectron Spectroscopy in Atmosphere (PESA): PESA is utilized to determine the ionization potential, which corresponds to the Highest Occupied Molecular Orbital (HOMO) energy level.[7] The Lowest Unoccupied Molecular Orbital (LUMO) can then be inferred from the HOMO level and the optical bandgap.

References

- 1. This compound - Wikipedia [en.wikipedia.org]

- 2. This compound [chm.bris.ac.uk]

- 3. researchgate.net [researchgate.net]

- 4. This compound | C22H14 | CID 8671 - PubChem [pubchem.ncbi.nlm.nih.gov]

- 5. pubs.acs.org [pubs.acs.org]