# Technical Support Center: Pentacene/Dielectric Interfaces

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |

|----------------------|-----------|-----------|

| Compound Name:       | Pentacene |           |

| Cat. No.:            | B032325   | Get Quote |

This technical support center provides troubleshooting guidance and answers to frequently asked questions for researchers and scientists working to minimize interface traps in **pentacene**-based organic thin-film transistors (OTFTs).

## Frequently Asked Questions (FAQs)

Q1: What are interface traps and why are they detrimental to pentacene OFET performance?

A1: Interface traps are electronically active defects located at the interface between the **pentacene** semiconductor and the gate dielectric layer. These traps can capture and immobilize charge carriers (holes in the case of **pentacene**), preventing them from contributing to the channel current. The presence of a high density of interface traps leads to several undesirable effects in OFETs, including a reduction in charge carrier mobility, an increase in the threshold voltage, significant hysteresis in the electrical characteristics, and a decrease in the device's switching speed and overall stability.[1][2][3]

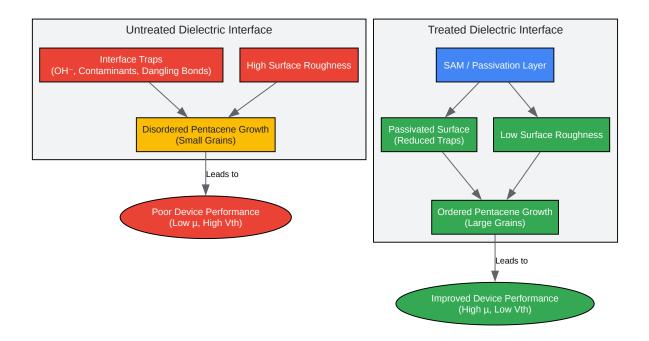

Q2: What are the primary causes of interface traps at the **pentacene**/dielectric junction?

A2: Interface traps originate from several sources:

• Surface Roughness: A rough dielectric surface can lead to poor ordering of **pentacene** molecules and create physical "valleys" that trap charges, hindering their movement.[4][5]

#### Troubleshooting & Optimization

- Surface Chemistry and Contamination: The chemical nature of the dielectric surface is critical.[6] Hydrophilic surfaces with -OH groups (silanol groups on SiO<sub>2</sub>) can act as electron traps.[7] Organic residues or moisture on the surface can also create significant trapping states.

- Structural and Electrostatic Disorder: Mismatches in the crystal structure and electrostatic potential in the first few layers of the **pentacene** film adjacent to the dielectric can create localized states that trap carriers.[2][3]

- **Pentacene** Growth Mode: The way **pentacene** grows on the dielectric surface (e.g., layer-by-layer vs. 3D island growth) influences the grain size and the number of grain boundaries, which can act as trapping sites.[6][8]

Q3: How can Self-Assembled Monolayers (SAMs) help in reducing interface traps?

A3: Applying a Self-Assembled Monolayer (SAM) to the dielectric surface before **pentacene** deposition is a highly effective strategy.[1] SAMs can:

- Passivate Surface Traps: The anchoring groups of the SAM molecules can react with and neutralize trap states, such as dangling bonds or hydroxyl groups, on the dielectric surface.

[1]

- Control Surface Energy: SAMs can modify the surface energy of the dielectric, making it more hydrophobic.[8] This promotes better molecular ordering and larger grain growth in the **pentacene** film, which reduces trap-inducing grain boundaries.[7]

- Improve Molecular Packing: By providing a more ordered and homogeneous surface, certain SAMs can facilitate a more favorable packing structure for the **pentacene** molecules, leading to higher charge carrier mobilities.[9][10]

Q4: What is the role of annealing in minimizing interface traps?

A4: Thermal annealing is a crucial post-deposition step that can significantly improve device performance. When performed in an inert atmosphere (like nitrogen or argon), annealing can:

Reduce Trap Density: It helps to remove adsorbed gases like water and oxygen from the interface and the pentacene bulk, which are known to create trap states.[11][12]

- Improve Film Morphology: Annealing can lead to the coarsening of **pentacene** grains and a reduction in surface roughness, which decreases the concentration of traps.[13]

- Enhance Electrical Properties: As a result of reduced trap density, annealed devices typically show increased hole mobility and a lower threshold voltage.[11][12][13] Annealing in specific gas atmospheres, such as NH<sub>3</sub>, has been shown to passivate dangling bonds on the dielectric surface, further reducing interface traps.[14][15]

Q5: Which dielectric materials are commonly used, and how does the choice of dielectric impact interface traps?

A5: The choice of dielectric material is fundamental to device performance.

- Silicon Dioxide (SiO<sub>2</sub>): While widely used due to its excellent insulating properties, untreated SiO<sub>2</sub> surfaces often have a high density of trap states.[2][3] Surface treatments are almost always necessary.

- Polymeric Dielectrics: Materials like PMMA, PVP, and polyimide are common.[16][17] They can provide smoother surfaces than inorganic dielectrics and can be solution-processed.[3] However, they can also introduce their own trap states if not processed correctly.

- High-k Dielectrics: Materials like HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and HfLaO are used to enable low-voltage operation.[14][15][18][19] A significant challenge with high-k dielectrics is the potential for increased charge trapping at the interface, which often necessitates the use of a passivation or buffer layer, such as a SAM or a thin polymer film.[19]

## **Troubleshooting Guide**

## Troubleshooting & Optimization

Check Availability & Pricing

| Problem                                    | Possible Causes                                                                              | Recommended Solutions & Troubleshooting Steps                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| High / Unstable Threshold<br>Voltage (Vth) | High density of fixed charges<br>or deep trap states at the<br>interface.[2][6]              | 1. Improve Dielectric Surface Cleaning: Use oxygen plasma cleaning instead of just solvent cleaning to more effectively remove organic residues. 2. Apply a SAM: Use an octadecyltrichlorosilane (OTS) or phosphonic acid (PA) SAM to passivate surface traps and reduce surface energy.[9][20] 3. Perform Annealing: Anneal the device in an inert atmosphere (e.g., N <sub>2</sub> or Ar) after fabrication to remove adsorbed species like water. [11][12][13] |  |

| Large Hysteresis in Transfer<br>Curve      | Mobile ions in the dielectric; slow charge trapping/detrapping at the interface.[3]          | 1. Use a Passivation Layer: Spin-coat a thin layer of a polymer like PMMA on the dielectric to minimize hysteresis caused by charge trapping.[3] 2. Optimize Annealing: Annealing can reduce hysteresis by removing mobile species like water.[21] 3. Check for Contamination: Ensure the purity of the pentacene source material and maintain a high vacuum during deposition to prevent impurity- related traps.[22][23]                                        |  |

| Low Field-Effect Mobility (μ)              | Poor pentacene crystallinity<br>and small grain size; high<br>density of shallow traps; high | Optimize Pentacene     Deposition: Maintain the     substrate at an elevated                                                                                                                                                                                                                                                                                                                                                                                      |  |

| surface roughness of the |  |

|--------------------------|--|

| dielectric.[4][5]        |  |

temperature (e.g., 70°C)

during deposition to promote

larger grain growth.[24] 2.

Reduce Dielectric Roughness:

Use smoother dielectrics like

polymers or employ techniques

like sol-gel silica films to create

a smoother interface, which

promotes larger pentacene

grains.[4][25] 3. Modify

Surface Energy: Use a SAM

treatment to create a

hydrophobic surface, which is

known to enhance pentacene

grain size and mobility.[7][20]

High OFF Current / Low ON/OFF Ratio

Impurities in the pentacene layer; defects or pinholes in the dielectric layer; irregular pentacene growth leading to voids at the interface.[7][8]

1. Purify Pentacene: Use vacuum train sublimation to purify the pentacene source material before deposition.[20]

2. Improve Dielectric Integrity: For polymer dielectrics, ensure the solution concentration and spin-coating parameters are optimized to avoid pinholes.[7]

[17] Using a bilayer dielectric can also help.[17] 3. Pattern the Active Layer: Use a stencil mask during pentacene deposition to minimize leakage currents between devices.[24]

## **Quantitative Data Summary**

Table 1: Effect of Dielectric Surface Treatment on **Pentacene** OFET Performance

| Treatment<br>on SiO <sub>2</sub> | Mobility<br>(cm²/Vs) | Threshold<br>Voltage (V) | Hysteresis<br>(ΔVth) | Key Finding                                                                  | Reference |

|----------------------------------|----------------------|--------------------------|----------------------|------------------------------------------------------------------------------|-----------|

| Solvent<br>Cleaning<br>Only      | Not Specified        | Not Specified            | 13.2 ± 0.6 V         | High hysteresis due to organic contaminatio n.                               | [24]      |

| Oxygen<br>Plasma<br>Cleaning     | Not Specified        | Not Specified            | 4.4 ± 0.2 V          | Plasma cleaning significantly reduces interfacial trapping states.           | [24]      |

| Untreated<br>SiO <sub>2</sub>    | 0.12 ± 0.02          | -10.5 ± 0.5 V            | Not Specified        | Baseline<br>performance<br>on standard<br>SiO <sub>2</sub> .                 | [20]      |

| OTS-treated<br>SiO <sub>2</sub>  | 0.6 ± 0.1            | -7.5 ± 0.5 V             | Not Specified        | OTS treatment improves mobility and on/off ratio despite smaller grain size. | [20]      |

| Sol-gel Silica<br>Film           | > 1.0                | Lower than<br>SiO2       | Not Specified        | Smoother interface leads to larger grains and reduced trap densities.        | [25]      |

Table 2: Effect of Annealing on **Pentacene** OFET Performance

| Device <i>l</i> Annealin g Condition                                          | Pre-<br>Anneal<br>Mobility<br>(cm²/Vs) | Post-<br>Anneal<br>Mobility<br>(cm²/Vs) | Pre-<br>Anneal<br>Vth (V) | Post-<br>Anneal<br>Vth (V) | Key<br>Finding                                                                  | Referenc<br>e |

|-------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|---------------------------|----------------------------|---------------------------------------------------------------------------------|---------------|

| Pentacene/<br>SiO <sub>2</sub> -<br>PMMA,<br>150°C,<br>15h, Ar+H <sub>2</sub> | 2.1 x 10 <sup>-3</sup><br>(avg)        | 2.9 x 10 <sup>-3</sup><br>(avg)         | -13.4 (avg)               | -9.9 (avg)                 | Annealing reduces traps, enlarges grains, and improves mobility by ~30%.        | [13]          |

| Pentacene/<br>Polyimide,<br>140°C                                             | 0.07                                   | 0.12                                    | Not<br>Specified          | Not<br>Specified           | Annealing reduces H <sub>2</sub> O concentrati on and charge traps.             | [11][12]      |

| HfLaO<br>Dielectric,<br>400°C,<br>NH <sub>3</sub>                             | Not<br>Specified                       | 0.59                                    | Not<br>Specified          | Not<br>Specified           | NH <sub>3</sub> annealing effectively passivates dielectric surface traps.      | [14][15]      |

| HfLaO<br>Dielectric,<br>400°C, N2                                             | Not<br>Specified                       | < 0.59                                  | Not<br>Specified          | Not<br>Specified           | N <sub>2</sub> annealing is less effective than NH <sub>3</sub> for passivation | [14][15]      |

## **Experimental Protocols**

Protocol 1: Dielectric Surface Preparation (SiO<sub>2</sub>)

- Objective: To clean the SiO<sub>2</sub> surface and remove organic contaminants and hydroxyl groups that act as traps.

- Materials: Substrates with thermally grown SiO<sub>2</sub>, acetone, isopropyl alcohol (IPA), deionized

(DI) water, oxygen plasma cleaner.

- Procedure (Solvent Cleaning): a. Sonicate substrates sequentially in acetone, IPA, and DI water for 15 minutes each. b. Dry the substrates with a stream of high-purity nitrogen gas.

- Procedure (Oxygen Plasma Cleaning): a. Perform the solvent cleaning procedure as

described above. b. Place the dried substrates into the chamber of an oxygen plasma

cleaner. c. Expose the substrates to oxygen plasma (e.g., at 50-100 W for 1-5 minutes). This

creates a fresh, reactive oxide surface.[24] d. Proceed immediately to the next step (e.g.,

SAM deposition or pentacene deposition) to minimize re-contamination.

Protocol 2: Self-Assembled Monolayer (SAM) Deposition (Dipping Method)

- Objective: To form a uniform monolayer on the dielectric to passivate traps and control surface energy.

- Materials: Plasma-cleaned substrates, trichlorosilane SAM (e.g., DTS or DCTS), anhydrous solvent (e.g., hexadecane or toluene), IPA.

- Procedure: a. Prepare a 5 mM solution of the SAM in the chosen anhydrous solvent inside a nitrogen-filled glovebox to avoid moisture-induced polymerization. b. Immerse the freshly plasma-cleaned SiO<sub>2</sub> substrates in the SAM solution. c. Leave the substrates immersed for an extended period (e.g., 12-16 hours) to allow for complete monolayer formation.[1] d. After immersion, remove the substrates and rinse them thoroughly with fresh solvent (e.g., IPA) to wash away any unreacted or physisorbed molecules.[1] e. Dry the substrates with a stream of high-purity nitrogen.

Protocol 3: **Pentacene** Deposition (Thermal Evaporation)

- Objective: To deposit a thin film of **pentacene** with good crystallinity.

- Materials: Purified **pentacene**, substrates with prepared dielectric, high-vacuum thermal evaporation system.

- Procedure: a. Load the substrates and the purified **pentacene** source material into the thermal evaporation chamber. b. Evacuate the chamber to a base pressure of at least 10<sup>-6</sup> Torr.[24] c. Heat the substrate holder to a specific temperature (e.g., 70°C) to control **pentacene** grain growth.[24] d. Heat the **pentacene** source (e.g., in a molybdenum boat) until it begins to sublime. e. Deposit the **pentacene** film at a controlled, slow rate (e.g., 0.1–0.2 nm/s) to a desired thickness (typically 50 nm).[24] f. After deposition, allow the substrates to cool to room temperature before venting the chamber.

#### **Visualizations**

Click to download full resolution via product page

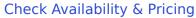

Caption: A workflow diagram for troubleshooting common performance issues in **pentacene** OFETs.

Click to download full resolution via product page

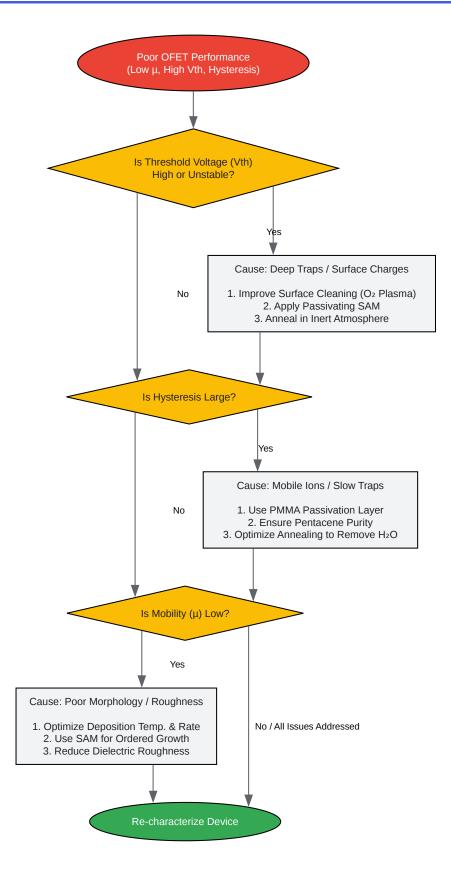

Caption: The impact of dielectric surface modification on **pentacene** growth and device performance.

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. Effect of Variations in the Alkyl Chain Lengths of Self-Assembled Monolayers on the Crystalline-Phase-Mediated Electrical Performance of Organic Field-Effect Transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 2. pubs.aip.org [pubs.aip.org]

- 3. pubs.aip.org [pubs.aip.org]

- 4. pubs.aip.org [pubs.aip.org]

- 5. lirias.kuleuven.be [lirias.kuleuven.be]

- 6. Effect of pentacene—dielectric affinity on pentacene thin film growth morphology in organic field-effect transistors Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

#### Troubleshooting & Optimization

- 7. mdpi.com [mdpi.com]

- 8. sol-gel.net [sol-gel.net]

- 9. Effects of self-assembled monolayer structural order, surface homogeneity and surface energy on pentacene morphology and thin film transistor device performance - PubMed [pubmed.ncbi.nlm.nih.gov]

- 10. researchgate.net [researchgate.net]

- 11. pubs.aip.org [pubs.aip.org]

- 12. pubs.aip.org [pubs.aip.org]

- 13. journals.ioffe.ru [journals.ioffe.ru]

- 14. hub.hku.hk [hub.hku.hk]

- 15. ieeexplore.ieee.org [ieeexplore.ieee.org]

- 16. ijera.com [ijera.com]

- 17. Performance Enhancement of Pentacene-Based Organic Thin-Film Transistors Using a High-K PVA/Low-K PVP Bilayer as the Gate Insulator PMC [pmc.ncbi.nlm.nih.gov]

- 18. oam-rc.inoe.ro [oam-rc.inoe.ro]

- 19. eipbn.org [eipbn.org]

- 20. pubs.aip.org [pubs.aip.org]

- 21. researchgate.net [researchgate.net]

- 22. Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance PMC [pmc.ncbi.nlm.nih.gov]

- 23. encyclopedia.pub [encyclopedia.pub]

- 24. pubs.aip.org [pubs.aip.org]

- 25. pubs.aip.org [pubs.aip.org]

- To cite this document: BenchChem. [Technical Support Center: Pentacene/Dielectric Interfaces]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b032325#minimizing-interface-traps-in-pentacene-dielectric-layers]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com