# Technical Support Center: Pentacene Film Deposition

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |

|----------------------|-----------|-----------|

| Compound Name:       | Pentacene |           |

| Cat. No.:            | B032325   | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with **pentacene** thin films. Our goal is to help you overcome common experimental challenges and improve the quality and performance of your **pentacene**-based devices.

## **Troubleshooting Guides**

This section addresses specific issues that may arise during the fabrication of **pentacene** thin films and offers potential causes and solutions.

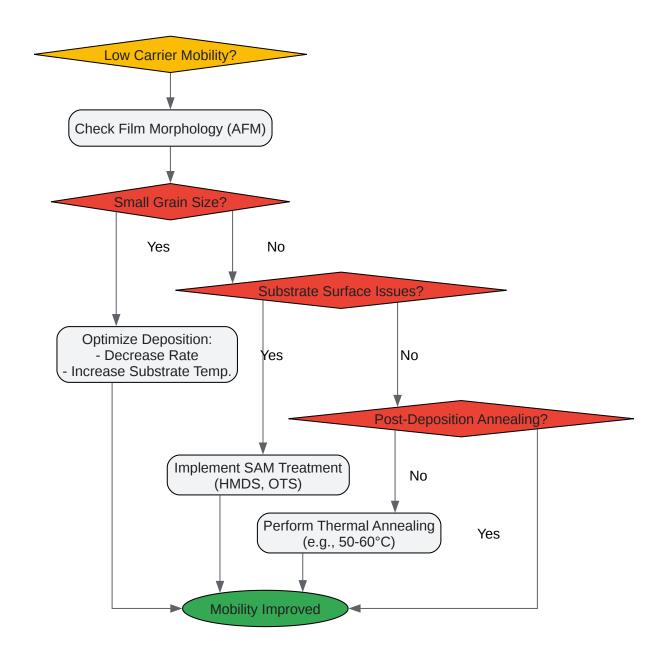

Issue 1: Low Carrier Mobility in Fabricated OTFTs

- Potential Causes:

- Poor crystallinity and small grain size of the pentacene film.

- Presence of impurities or defects acting as charge traps.[1]

- Unfavorable morphology of the dielectric surface.

- High contact resistance between the electrodes and the pentacene layer.

- Troubleshooting Steps:

- Optimize Deposition Parameters:

- Deposition Rate: A slower deposition rate is often optimal for better crystallization.[3]

However, the ideal rate can be system-dependent and may require empirical optimization.[4]

- Substrate Temperature: Increasing the substrate temperature during deposition can enhance the surface mobility of pentacene molecules, leading to larger grain sizes.[5]

[6] Be aware that excessively high temperatures can sometimes lead to a transition from 2D to 3D growth, which may be detrimental.[7]

- Substrate Surface Treatment:

- Apply a self-assembled monolayer (SAM) such as hexamethyldisilazane (HMDS) or octadecyltrichlorosilane (OTS) to the dielectric surface prior to pentacene deposition.[3]

[8] This can improve molecular ordering and film morphology.[9]

- Post-Deposition Annealing:

- Perform thermal annealing after film deposition. Annealing at moderate temperatures (e.g., 50-60°C) can improve molecular ordering and increase grain size.[10] However, annealing at excessively high temperatures (e.g., above 70°C) can degrade the film's crystallinity and performance.[10][11]

- Source Material Purity:

- Ensure the purity of the pentacene source material, as impurities like

pentacenequinone can act as charge traps and disrupt crystal growth.[12]

Issue 2: High Off-State Current (Low On/Off Ratio)

- Potential Causes:

- Leakage current through the gate dielectric.

- Presence of conductive pathways or defects in the pentacene film.

- Damage to the pentacene layer during top electrode deposition.[3]

- Troubleshooting Steps:

- Inspect Dielectric Integrity: Verify the quality and integrity of the gate dielectric layer to minimize leakage currents.

- Optimize Pentacene Thickness: An excessively thick pentacene film can sometimes contribute to higher off-currents. A thickness of around 50 nm is a common starting point.

[3]

- Gentle Top Electrode Deposition: If using a top-contact architecture, employ a low-energy deposition technique for the source/drain electrodes to avoid damaging the underlying pentacene layer.

#### Issue 3: Poor Film Adhesion and Delamination

- Potential Causes:

- Inadequate substrate cleaning.

- High internal stress in the pentacene film.

- Troubleshooting Steps:

- Thorough Substrate Cleaning: Implement a rigorous substrate cleaning protocol to remove organic residues and particulate matter.[13][14]

- Optimize Deposition Conditions: High deposition rates can sometimes lead to increased film stress. Consider reducing the deposition rate.

- Surface Energy Modification: Using a SAM treatment can improve the adhesion of the pentacene film to the substrate.

#### Issue 4: Inconsistent Device-to-Device Performance

- Potential Causes:

- Non-uniformity in substrate temperature during deposition.

- Inhomogeneous deposition rate across the substrate.

- Variations in substrate surface preparation.

- Troubleshooting Steps:

- Ensure Uniform Heating: Verify that your substrate heater provides uniform temperature distribution across the entire sample area.

- Calibrate Deposition Source: Ensure that the evaporation source provides a consistent and uniform flux of **pentacene** molecules.

- Standardize Procedures: Maintain strict consistency in all substrate preparation and deposition steps.

## **Frequently Asked Questions (FAQs)**

Q1: What is the optimal deposition rate for **pentacene**?

A slower deposition rate, typically in the range of 0.1-0.5 Å/s, is generally favored to promote the formation of large, well-ordered crystalline grains, which is crucial for high carrier mobility.

[3] However, the ideal rate can vary depending on other parameters like substrate temperature and the specific deposition system.

[4]

Q2: How does substrate temperature affect **pentacene** film growth?

Substrate temperature is a critical parameter. Increasing the temperature (e.g., to 60-90°C) enhances the mobility of **pentacene** molecules on the surface, which can lead to larger grain sizes and improved film crystallinity.[5][6] However, at very high temperatures, there can be a transition from a layer-by-layer growth to a 3D island growth, and desorption of molecules from the first monolayer can occur, which may negatively impact device performance.[7]

Q3: Why is substrate surface treatment important?

Treating the dielectric surface with a self-assembled monolayer (SAM) like HMDS or OTS is a common technique to improve the quality of the **pentacene** film.[8] These treatments modify the surface energy of the dielectric, which can promote better molecular ordering, lead to larger grain sizes, and ultimately enhance the carrier mobility of the resulting transistor.[9]

Q4: What is the purpose of post-deposition annealing?

Post-deposition thermal annealing can improve the molecular ordering and crystallinity of the **pentacene** film.[10] Annealing at temperatures around 50-60°C has been shown to increase grain size and improve device performance.[10] It is important to avoid excessive annealing temperatures (e.g., above 70°C), as this can lead to a loss of crystallinity and a decrease in performance.[10][11]

Q5: What are common characterization techniques for **pentacene** films?

Atomic Force Microscopy (AFM) is widely used to investigate the surface morphology, grain size, and roughness of **pentacene** films.[15][16] X-ray Diffraction (XRD) is employed to determine the crystal structure, molecular orientation, and phase of the **pentacene** film.[3][16]

## **Quantitative Data Summary**

The following tables summarize key quantitative data from various studies on improving **pentacene** film quality.

Table 1: Effect of Deposition Rate on OTFT Performance

| Deposition<br>Rate (Å/s) | Substrate<br>Temperature<br>(°C) | Carrier<br>Mobility<br>(cm²/Vs) | On/Off Ratio | Reference |

|--------------------------|----------------------------------|---------------------------------|--------------|-----------|

| 0.05                     | 70                               | 0.19                            | -            | [4]       |

| 0.4                      | 70                               | 0.52                            | -            | [4]       |

| 1.14                     | 70                               | 0.065                           | -            | [4]       |

| 0.2 - 0.3                | 70                               | -                               | -            | [3]       |

| 0.5                      | 70                               | Varies by orders of magnitude   | -            | [17]      |

Table 2: Effect of Substrate Temperature on OTFT Performance

| Substrate<br>Temperature<br>(°C) | Deposition<br>Rate (Å/s) | Carrier<br>Mobility<br>(cm²/Vs)              | Grain Size | Reference |

|----------------------------------|--------------------------|----------------------------------------------|------------|-----------|

| Room<br>Temperature              | 1                        | -                                            | Smaller    | [5]       |

| 60                               | 1                        | -                                            | Larger     | [5]       |

| 90                               | 1                        | ~0.21                                        | Largest    | [5]       |

| 30                               | -                        | 10 <sup>-5</sup> (for TMS-<br>pentacene)     | -          | [3]       |

| 60                               | -                        | 10 <sup>-4</sup> (for t-butyl-<br>pentacene) | -          | [3]       |

| 90                               | -                        | 10 <sup>-4</sup> (for TIPS-<br>pentacene)    | -          | [3]       |

Table 3: Effect of Post-Deposition Annealing on OTFT Performance

| Annealing<br>Temperature<br>(°C) | Carrier<br>Mobility<br>(cm²/Vs) | On/Off Ratio     | Grain Size               | Reference |

|----------------------------------|---------------------------------|------------------|--------------------------|-----------|

| No Annealing                     | 0.19                            | -                | -                        | [10]      |

| 50                               | 0.36                            | Increased by ~2x | Increased                | [10]      |

| 60                               | -                               | -                | Slightly<br>Increased    | [10]      |

| ≥ 70                             | Decreased                       | -                | Loss of<br>Crystallinity | [10]      |

| up to 50                         | Increased by ~2x                | -                | Increased                | [11]      |

| > 50                             | Decreased                       | -                | -                        | [11]      |

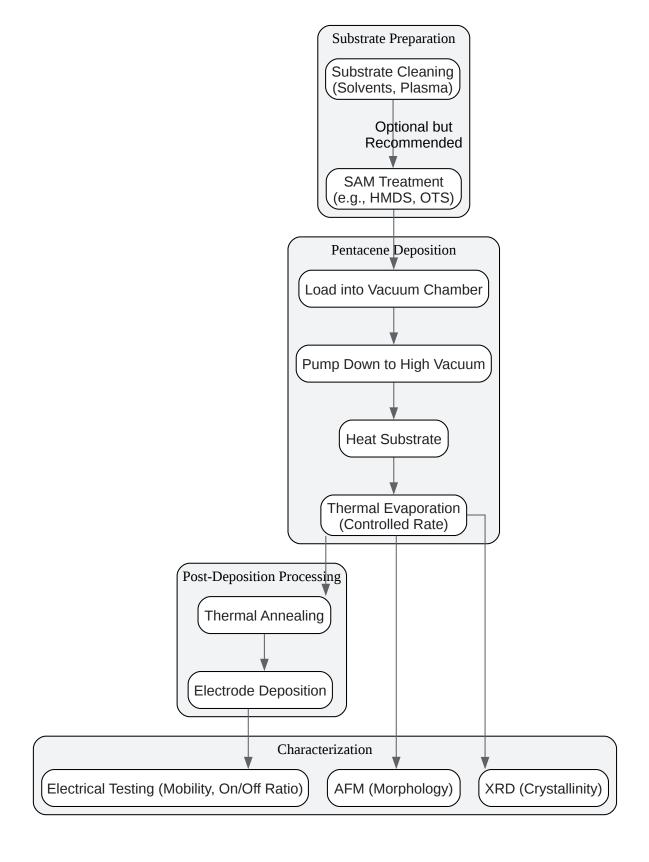

# **Experimental Protocols**

#### Protocol 1: Substrate Cleaning for Pentacene Deposition

- Solvent Cleaning:

- Sequentially sonicate the substrates in acetone, and isopropyl alcohol (IPA) for 10-15 minutes each.[14]

- Rinse thoroughly with deionized (DI) water between each solvent step.

- Dry the substrates with a stream of dry nitrogen.

- Piranha/UV-Ozone Cleaning (for Si/SiO<sub>2</sub> substrates):

- For a more aggressive clean to remove organic residues, use a piranha solution (a mixture of sulfuric acid and hydrogen peroxide) or a UV-ozone treatment. (Caution: Piranha solution is extremely corrosive and should be handled with appropriate safety precautions).[18]

- After piranha cleaning, rinse extensively with DI water.

- o Dry the substrates with a stream of dry nitrogen.

- Plasma Cleaning:

- Immediately before loading into the deposition chamber, an in-situ plasma clean using argon or oxygen can be performed to remove any remaining surface contaminants.[14]

#### Protocol 2: Thermal Evaporation of Pentacene

- System Preparation:

- Achieve a high vacuum in the deposition chamber, typically in the range of 10<sup>-6</sup> to 10<sup>-7</sup>

Torr, to minimize contamination.[3]

- Substrate Preparation:

- Mount the cleaned substrates onto the substrate holder.

- If applicable, perform an in-situ surface treatment (e.g., HMDS vapor deposition).

- Heat the substrate to the desired deposition temperature (e.g., 70°C).[3]

- Deposition:

- Heat the crucible containing the **pentacene** source material until sublimation begins.

- Slowly open the shutter to begin deposition onto the substrates.

- Monitor the deposition rate using a quartz crystal microbalance and maintain it at the desired value (e.g., 0.2-0.5 Å/s).[3]

- Deposit a film of the desired thickness, typically around 50 nm.[3]

- Cool Down:

- After deposition, allow the substrates to cool down to room temperature under vacuum before venting the chamber.

### **Visualizations**

Click to download full resolution via product page

Caption: Experimental workflow for fabricating and characterizing high-quality **pentacene** thin-film transistors.

#### Click to download full resolution via product page

Caption: Troubleshooting flowchart for addressing low carrier mobility in pentacene OTFTs.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. rug.nl [rug.nl]

- 2. pubs.aip.org [pubs.aip.org]

- 3. Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance PMC [pmc.ncbi.nlm.nih.gov]

- 4. researchgate.net [researchgate.net]

- 5. pubs.aip.org [pubs.aip.org]

- 6. pubs.acs.org [pubs.acs.org]

- 7. Modified bimodal growth mechanism of pentacene thin films at elevated substrate temperatures - PubMed [pubmed.ncbi.nlm.nih.gov]

- 8. mdpi.com [mdpi.com]

- 9. pubs.aip.org [pubs.aip.org]

- 10. researchgate.net [researchgate.net]

- 11. journals.ioffe.ru [journals.ioffe.ru]

- 12. [0810.0428] Effect of Impurities on Pentacene Thin Film Growth for Field-Effect Transistors [arxiv.org]

- 13. Substrate Cleaning [utep.edu]

- 14. How Do You Clean Substrate For Thin Film Deposition? Achieve Pristine Surfaces For Superior Film Quality - Kintek Solution [kindle-tech.com]

- 15. researchgate.net [researchgate.net]

- 16. aquila.infn.it [aquila.infn.it]

- 17. Effect of pentacene deposition rate on device characteristics of top contact organic thin film transistors | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 18. Substrate Cleaning [cleanroom.byu.edu]

- To cite this document: BenchChem. [Technical Support Center: Pentacene Film Deposition]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b032325#pentacene-film-quality-improvement-techniques]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com