# Technical Support Center: Pentacene-Based OTFTs

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |  |  |  |

|----------------------|-----------|-----------|--|--|--|

| Compound Name:       | Pentacene |           |  |  |  |

| Cat. No.:            | B032325   | Get Quote |  |  |  |

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in improving the performance of **pentacene**-based Organic Thin-Film Transistors (OTFTs).

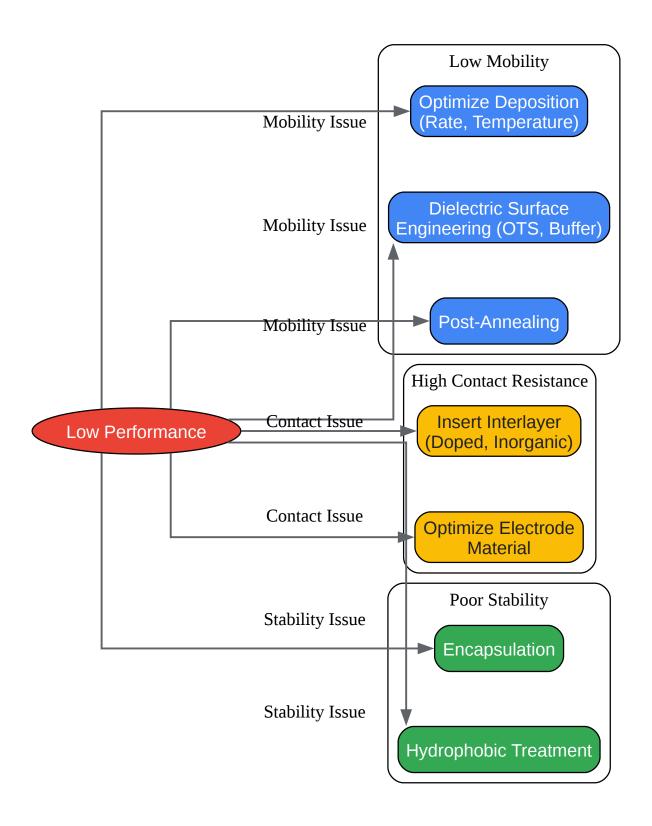

## **Troubleshooting Guides**

This section addresses common issues encountered during the fabrication and characterization of **pentacene**-based OTFTs.

Issue 1: Low Carrier Mobility

Q: My **pentacene** OTFT exhibits low hole mobility. What are the potential causes and how can I improve it?

A: Low carrier mobility in **pentacene** OTFTs is a frequent challenge that can stem from several factors related to the quality of the **pentacene** film, the dielectric interface, and device fabrication processes.

Potential Causes and Solutions:

- Poor Crystalline Quality of Pentacene Film: The degree of molecular ordering in the pentacene film is critical for efficient charge transport.

- Optimize Deposition Rate: The deposition rate of **pentacene** significantly influences film morphology and mobility. A study showed that for deposition at 70°C on silicon oxide,

## Troubleshooting & Optimization

mobility can change by four orders of magnitude as the deposition rate varies from 0.5 to 1.5 nm/min.[1][2] An optimal deposition rate, for instance, of 0.4 Å/s has been shown to yield higher mobility compared to lower or higher rates.[1]

- Substrate Temperature Control: The temperature of the substrate during pentacene

deposition affects grain size and molecular ordering. Increasing the substrate temperature

generally leads to larger grain sizes, which can improve mobility.[3] However, there is an

optimal temperature range, as excessively high temperatures can be detrimental.

- Post-Deposition Annealing: Thermal annealing after **pentacene** deposition can improve crystallinity and molecular ordering, leading to increased mobility.[4] For instance, annealing at 50°C was found to increase mobility from 0.19 to 0.36 cm²/Vs.[4] However, annealing at temperatures of 70°C or higher can degrade performance by causing the film to lose its crystallinity.[4][5] Annealing in an inert atmosphere, such as a mix of Argon and Hydrogen, at 150°C has been shown to increase hole mobility by an average of 30% and decrease surface roughness.[6]

- Unfavorable Dielectric Surface: The interface between the gate dielectric and the **pentacene** active layer plays a crucial role in charge carrier accumulation and transport.

- Surface Treatment: Treatment of the dielectric surface with self-assembled monolayers

(SAMs) like octadecyltrichlorosilane (OTS) can significantly improve device performance.

[7][8][9] OTS treatment can reduce interface traps and promote better **pentacene** growth, leading to higher mobility.[7][8][9][10]

- Dielectric Buffer Layers: Applying a dielectric buffer layer, such as poly(α-methylstyrene)

(PαMS) on top of the primary gate dielectric, can enhance the interfacial affinity with

pentacene, leading to larger grain sizes and improved mobility.[11]

- Surface Energy Matching: The surface energy of the dielectric can influence pentacene growth. A good match between the surface energy of the dielectric and pentacene can lead to the growth of larger grains and higher mobility.[12][13][14]

- Presence of Traps: Charge traps at the dielectric-semiconductor interface or within the

pentacene bulk can immobilize charge carriers and reduce mobility.

- Dielectric Choice: Using high-quality gate dielectrics with a low density of surface traps is essential. Amorphous barium titanate (BTO) has been shown to be an effective high-k gate dielectric, resulting in high mobility and low trap density.[14]

- Annealing: As mentioned earlier, post-deposition annealing can reduce the number of interfacial trap states.[4]

#### Issue 2: High Contact Resistance

Q: I am observing high contact resistance between the source/drain electrodes and the **pentacene** layer. What are the causes and how can I reduce it?

A: High contact resistance is a significant performance-limiting factor in OTFTs, especially as channel lengths are reduced.[15] It arises from the energy barrier for charge injection from the metal electrode to the organic semiconductor.

#### Potential Causes and Solutions:

- Energy Level Mismatch: A large mismatch between the work function of the electrode metal and the highest occupied molecular orbital (HOMO) of **pentacene** creates a high injection barrier for holes.

- Choice of Electrode Material: While gold (Au) is commonly used, its direct deposition on pentacene can lead to diffusion and the formation of a mixed layer, resulting in a large energy barrier.

[16] Palladium (Pd) has also been investigated.

- Insertion of an Interlayer: Introducing a thin interlayer between the electrode and the pentacene can reduce the injection barrier.

- Doped Interlayers: A tetrafluorotetracyanoquinodimethane (F4TCNQ)-doped pentacene interlayer can significantly reduce contact resistance and improve device performance.

[18][19] A 1:1 ratio of F4TCNQ to pentacene has shown considerable improvement in electrical characteristics.[19]

- Inorganic Interlayers: A thin layer of germanium oxide (GeO) between the Au electrode and pentacene has been shown to reduce the barrier height and improve mobility to as high as 0.96 cm²/Vs.[16]

- Device Architecture: The geometry of the device can influence contact resistance.

- Top-Contact vs. Bottom-Contact: Top-contact (TC) and bottom-contact (BC) device structures can exhibit different contact resistances due to differences in the metal-organic interface formation.[20] The choice between TC and BC geometries can impact charge injection and overall device performance.[20]

Issue 3: Device Degradation and Instability

Q: My **pentacene** OTFTs degrade quickly when exposed to ambient conditions. How can I improve their stability?

A: **Pentacene** OTFTs are known to be sensitive to environmental factors, leading to performance degradation over time.

Potential Causes and Solutions:

- Environmental Factors:

- Oxygen and Moisture: Exposure to air (oxygen) and humidity are major causes of degradation.[21] Water molecules can act as traps for charge carriers.

- Encapsulation: Encapsulating the device with a protective layer can shield it from ambient air and moisture, significantly improving stability.

- Hydrophobic Treatments: Surface treatments that create a hydrophobic surface on the dielectric can reduce the impact of humidity.[21]

- Intrinsic Instability (Bias Stress Effect): Applying a prolonged gate bias can lead to a shift in the threshold voltage, known as the bias stress effect. This is often attributed to charge trapping in the dielectric or at the interface.

- Dielectric Quality: Using high-quality gate dielectrics with low trap densities can mitigate the bias stress effect.

- Interface Passivation: Surface treatments can passivate trap states at the semiconductordielectric interface, improving stability.

## Frequently Asked Questions (FAQs)

Q1: What is a typical mobility value for a well-performing pentacene OTFT?

A1: A good mobility value for a **pentacene** OTFT is generally considered to be greater than 0.1 cm<sup>2</sup>/Vs.[4] High-performance devices can exhibit mobilities exceeding 1 cm<sup>2</sup>/Vs, with some reports of mobility as high as 2.91 cm<sup>2</sup>/Vs.[14]

Q2: What is the difference between top-contact and bottom-contact OTFT architectures?

A2: The main difference lies in the fabrication sequence of the source/drain electrodes relative to the organic semiconductor layer.

- Bottom-Contact (BC): The source and drain electrodes are patterned on the gate dielectric before the deposition of the **pentacene** layer.

- Top-Contact (TC): The **pentacene** layer is deposited first, followed by the deposition of the source and drain electrodes on top of it. The choice of architecture can affect contact resistance and overall device performance.[20]

Q3: How does the thickness of the **pentacene** film affect device performance?

A3: The thickness of the **pentacene** film is a critical parameter. An optimal thickness is required for good performance. For instance, a mobility of 0.0151 cm<sup>2</sup>/V·s was achieved with a 15 nm thick **pentacene** film treated at a post-annealing temperature of 70 °C, which was the highest value for the post-annealing process.[22][23]

Q4: Can I use a solution-based deposition method for **pentacene**?

A4: Yes, while thermal evaporation is common for **pentacene**, soluble derivatives like 6,13-bis(triisopropylsilylethynyl) **pentacene** (TIPS-**pentacene**) can be deposited from solution using techniques like spin coating or dip coating.[24][25][26] Solution processing offers potential for lower-cost and large-area fabrication.[26] The performance of solution-processed devices is highly dependent on the choice of solvent, solution concentration, and deposition method.[24]

#### **Quantitative Data Summary**

Table 1: Effect of Post-Deposition Annealing on Pentacene OTFT Performance

| Annealing<br>Temperature (°C) | Mobility (cm²/Vs) | On/Off Ratio          | Reference |

|-------------------------------|-------------------|-----------------------|-----------|

| No Annealing                  | 0.19              | -                     | [4]       |

| 50                            | 0.36              | Increased             | [4]       |

| 70                            | Decreased         | -                     | [4][5]    |

| 100 (DPP-DTT based)           | 0.816             | 1.4 x 10 <sup>3</sup> | [4]       |

| 150 (in inert atm)            | ~30% Increase     | -                     | [6]       |

Table 2: Effect of Surface Treatment and Interlayers on **Pentacene** OTFT Performance

| Dielectric/Inter<br>face<br>Modification  | Mobility<br>(cm²/Vs) | Threshold<br>Voltage (V) | On/Off Ratio           | Reference |

|-------------------------------------------|----------------------|--------------------------|------------------------|-----------|

| Bare PTFMA                                | -                    | -                        | -                      | [11]      |

| PαMS on<br>PTFMA                          | 0.70                 | -10.5                    | 5.4 x 10 <sup>5</sup>  | [11]      |

| Au electrode only                         | -                    | -                        | -                      | [16]      |

| GeO interlayer (5<br>nm) on Au            | 0.96                 | -                        | -                      | [16]      |

| No F4TCNQ<br>interlayer                   | -                    | -                        | -                      | [19]      |

| F4TCNQ:pentac<br>ene (1:1)<br>interlayer  | 1.6x<br>enhancement  | -                        | 1.5x<br>enhancement    | [19]      |

| OTS treated                               | 1.25                 | -                        | -                      | [10]      |

| BTO dielectric<br>(sputtered at<br>200°C) | 2.91                 | -1.09                    | 1.16 x 10 <sup>6</sup> | [14]      |

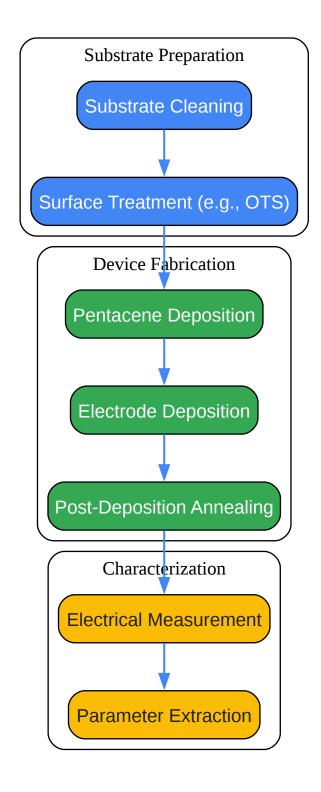

## **Experimental Protocols**

Protocol 1: Fabrication of a Bottom-Gate, Top-Contact (BGTC) Pentacene OTFT

- Substrate Cleaning: Start with a heavily doped n-type silicon wafer (acting as the gate electrode) with a thermally grown silicon dioxide (SiO<sub>2</sub>) layer (gate dielectric). Clean the substrate sequentially in ultrasonic baths of acetone, and isopropyl alcohol, followed by rinsing with deionized water and drying with nitrogen.

- Dielectric Surface Treatment (Optional but Recommended):

- Immerse the substrate in a piranha solution (a mixture of sulfuric acid and hydrogen peroxide) to hydroxylate the SiO<sub>2</sub> surface. (Caution: Piranha solution is extremely corrosive and should be handled with extreme care in a fume hood).

- Alternatively, treat the substrate with UV-ozone for 10-15 minutes.

- For OTS treatment, immerse the cleaned substrate in a freshly prepared solution of octadecyltrichlorosilane in an anhydrous solvent like toluene or hexane for a specified duration, followed by rinsing with the solvent and baking to form a self-assembled monolayer.

- **Pentacene** Deposition: Deposit a thin film of **pentacene** (typically 30-50 nm) by thermal evaporation in a high-vacuum chamber (pressure < 10<sup>-6</sup> Torr). Maintain the substrate at a constant temperature (e.g., 60-70°C) during deposition. The deposition rate should be carefully controlled (e.g., 0.1-0.5 Å/s).

- Source and Drain Electrode Deposition: Deposit the source and drain electrodes (e.g., 50 nm of gold) on top of the **pentacene** layer through a shadow mask to define the channel length and width.

- Post-Deposition Annealing (Optional): Anneal the fabricated device in a vacuum or an inert atmosphere at a moderate temperature (e.g., 50-70°C) for a specific duration to improve performance.

Protocol 2: Electrical Characterization of OTFTs

- Equipment: Use a semiconductor parameter analyzer or a source-measure unit connected to a probe station.

- Measurement Environment: Perform measurements in a dark, shielded box to avoid photogenerated currents and electrical noise. For stability studies, measurements can be done in a controlled atmosphere (e.g., nitrogen or vacuum).

- Output Characteristics (I\_DS vs. V\_DS):

- Apply a constant gate-source voltage (V\_GS).

- Sweep the drain-source voltage (V\_DS) from 0 V to a negative voltage (for p-type pentacene) and measure the drain current (I\_DS).

- Repeat for several V GS values.

- Transfer Characteristics (I\_DS vs. V\_GS):

- Apply a constant V\_DS in the linear region (low V\_DS) and the saturation region (high V\_DS).

- Sweep V\_GS from a positive to a negative voltage and measure I\_DS.

- Parameter Extraction:

- Field-Effect Mobility ( $\mu$ ): Calculate from the slope of the (I\_DS)<sup>1/2</sup> vs. V\_GS plot in the saturation region.

- Threshold Voltage (V\_th): Determine from the x-intercept of the linear fit to the (I\_DS)<sup>1/2</sup> vs. V GS plot.

- On/Off Ratio: Calculate as the ratio of the maximum on-current to the minimum off-current from the transfer curve.

## **Visualizations**

Click to download full resolution via product page

Caption: Experimental workflow for **pentacene** OTFT fabrication and characterization.

Click to download full resolution via product page

Caption: Troubleshooting logic for common **pentacene** OTFT performance issues.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. researchgate.net [researchgate.net]

- 2. Effect of pentacene deposition rate on device characteristics of top contact organic thin film transistors | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 3. yonsei.elsevierpure.com [yonsei.elsevierpure.com]

- 4. mdpi.com [mdpi.com]

- 5. pubs.aip.org [pubs.aip.org]

- 6. journals.ioffe.ru [journals.ioffe.ru]

- 7. Investigation of the Device Degradation Mechanism in Pentacene-Based Thin-Film Transistors Using Low-Frequency-Noise Spectroscopy | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 8. researchgate.net [researchgate.net]

- 9. Investigation of the Device Degradation Mechanism in Pentacene-Based Thin-Film Transistors Using Low-Frequency-Noise Spectroscopy | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 10. individual.utoronto.ca [individual.utoronto.ca]

- 11. pubs.aip.org [pubs.aip.org]

- 12. researchgate.net [researchgate.net]

- 13. pure.kaist.ac.kr [pure.kaist.ac.kr]

- 14. Hysteresis-Free High-Performance Pentacene Organic Thin-Film Transistor by Sputtering Amorphous Barium Titanate as Ultrathin High-k Gate Dielectric | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 15. Contact resistance of organic TFTs [fkf.mpg.de]

- 16. pubs.aip.org [pubs.aip.org]

- 17. pubs.aip.org [pubs.aip.org]

- 18. researchgate.net [researchgate.net]

- 19. Effects of the F4TCNQ-Doped Pentacene Interlayers on Performance Improvement of Top-Contact Pentacene-Based Organic Thin-Film Transistors [mdpi.com]

- 20. pubs.aip.org [pubs.aip.org]

- 21. researchgate.net [researchgate.net]

- 22. researchgate.net [researchgate.net]

- 23. Pentacene Organic Thin-film Transistors with Post-annealing Treatments [npsm-kps.org]

- 24. encyclopedia.pub [encyclopedia.pub]

- 25. Improved Tips-Pentacene-Based Organic Thin Film Transistors and Their Applications;

Memory Transistor and Gas Sensing ProQuest [proquest.com]

- 26. pubs.aip.org [pubs.aip.org]

- To cite this document: BenchChem. [Technical Support Center: Pentacene-Based OTFTs]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b032325#improving-performance-of-pentacene-based-otfts]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com