# Technical Support Center: Pentacene Transistor Fabrication & Troubleshooting

Author: BenchChem Technical Support Team. Date: December 2025

This technical support center provides researchers, scientists, and drug development professionals with troubleshooting guides and frequently asked questions (FAQs) to address common challenges encountered during the fabrication and characterization of **pentacene**-based organic thin-film transistors (OTFTs), with a specific focus on minimizing leakage current.

## Frequently Asked Questions (FAQs) & Troubleshooting Guides

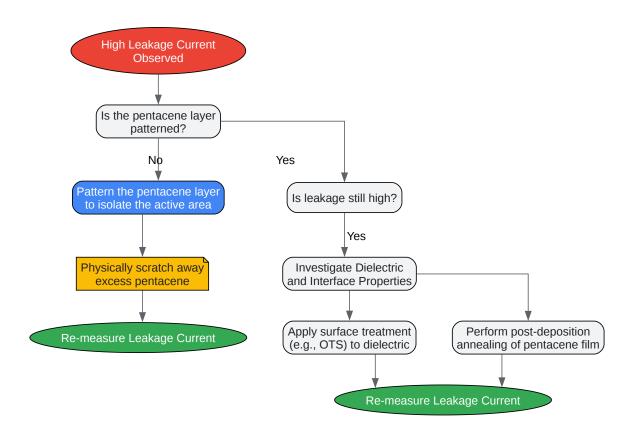

Q1: I am observing a very high off-state current (leakage current) in my bottom-gate **pentacene** transistor. What are the likely causes and how can I reduce it?

High off-state current, often referred to as leakage current, is a common issue in **pentacene** transistors, particularly those fabricated on common gate substrates like Si/SiO<sub>2</sub>. The primary cause is often current leakage through the entire substrate, not just the channel of the transistor.

#### Troubleshooting Steps:

Pattern the Semiconductor Layer: The most effective method to reduce this leakage is to

pattern the pentacene film. If the semiconductor is deposited over the entire substrate,

applying a gate voltage will cause charge accumulation across the whole film, leading to

significant leakage.[1][2] By isolating the pentacene to the active area between the source

and drain electrodes, you confine the current path and dramatically reduce leakage. A simple

## Troubleshooting & Optimization

way to do this is by carefully scratching away the excess **pentacene** around the device electrodes with a sharp tip.[1][2]

- Pattern the Gate Electrode: While patterning the semiconductor is crucial, patterning the gate electrode can also help in minimizing leakage.[1]

- Check Dielectric Integrity: Perform a metal-insulator-metal (MIM) measurement on your substrate to check the quality of your gate dielectric. A high-quality, pinhole-free dielectric is essential for low leakage. Thermally grown SiO<sub>2</sub> is generally reliable, but defects can occur.

Q2: My device performance is poor, and the leakage current is still high even after patterning the semiconductor. What other factors should I investigate?

If patterning the active layer does not sufficiently reduce the leakage current, the issue may lie with the gate dielectric or the interface between the dielectric and the **pentacene** film.

### **Troubleshooting Steps:**

- Optimize the Gate Dielectric:

- Material Choice: The choice of gate dielectric material significantly impacts device

performance and leakage. High-quality dielectrics with good insulating properties are

essential.[3] Using high-k polymer dielectrics can enable low-voltage operation and reduce

power consumption.[4] Bilayer gate insulators, such as a high-k/low-k combination (e.g.,

PVA/PVP), can also enhance performance by increasing gate capacitance while

maintaining good insulation.[5]

- Surface Roughness: A smooth dielectric surface is critical for good pentacene growth and low leakage.[6][7] Increased roughness can lead to a higher density of trap states at the interface, which can contribute to leakage.[6]

- Surface Treatment of the Dielectric: The interface between the gate dielectric and the pentacene semiconductor is crucial. Treating the dielectric surface with a self-assembled monolayer (SAM), such as octadecyltrichlorosilane (OTS), can improve the ordering of the pentacene molecules, leading to better device performance and potentially lower leakage.[8]

[9][10] However, the choice of SAM is important, as some treatments can negatively impact stability.[8]

Post-Deposition Annealing: Annealing the pentacene film after deposition can improve its

crystallinity and reduce defects, which in turn can lead to lower leakage current and a higher

on/off ratio.[11][12][13] The optimal annealing temperature needs to be determined

experimentally, as excessive heat can damage the film.[14]

Q3: I'm using a polymer gate dielectric and observing significant hysteresis in my transistor characteristics. What could be the cause and how can I mitigate it?

Hysteresis in OTFTs with polymer dielectrics is often attributed to charge trapping within the dielectric or at the semiconductor-dielectric interface.

#### **Troubleshooting Steps:**

- Cross-linking the Dielectric: For some polymer dielectrics, a thermal cross-linking step can improve their insulating properties and reduce the presence of mobile ions and water molecules, which are common sources of hysteresis.[3]

- Dielectric Composition: The chemical structure of the polymer dielectric plays a role. For example, hydroxyl groups in polymers like poly(vinyl alcohol) (PVA) can act as electron traps and attract water, leading to hysteresis.[3]

- Encapsulation: Protecting the device from ambient moisture and oxygen by encapsulation can improve stability and reduce hysteresis over time.[15]

## **Quantitative Data Summary**

The following table summarizes the impact of different optimization techniques on the on/off current ratio of **pentacene** transistors, a key metric for assessing leakage current.

| Optimization<br>Technique                        | Initial On/Off Ratio    | On/Off Ratio After<br>Treatment | Reference |

|--------------------------------------------------|-------------------------|---------------------------------|-----------|

| Post-Annealing (90°C for 12h in N <sub>2</sub> ) | 10 <sup>3</sup>         | 107                             | [11]      |

| Post-Annealing (60°C)                            | -                       | 1.87 x 10 <sup>4</sup>          | [12]      |

| Post-Annealing (120°C)                           | 4.0 x 10 <sup>3</sup>   | 8.7 x 10 <sup>3</sup>           | [13]      |

| Bilayer Gate Dielectric (PVA/PVP)                | ~10³ (for single layer) | ~104                            | [16]      |

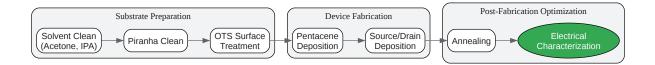

## **Key Experimental Protocols**

1. Protocol for Post-Deposition Annealing of **Pentacene** Films

This protocol describes a general procedure for annealing **pentacene** thin films to improve device performance and reduce leakage current.

- Objective: To improve the crystallinity and reduce defects in the **pentacene** film, leading to a lower off-state current and a higher on/off ratio.

- Materials:

- Fabricated pentacene transistor device.

- Tube furnace or hot plate in a controlled environment (e.g., glovebox).

- Inert gas supply (e.g., Nitrogen or Argon).

#### Procedure:

- Place the fabricated device into the annealing chamber (tube furnace or onto the hot plate within a glovebox).

- Purge the chamber with a high-purity inert gas for at least 30 minutes to remove oxygen and moisture.

## Troubleshooting & Optimization

- Ramp up the temperature to the desired setpoint (e.g., 60°C, 90°C, or 120°C). The optimal temperature should be determined experimentally.[11][12][13]

- Maintain the device at the set temperature for the desired duration (e.g., 1 to 12 hours).

[11]

- After the annealing period, turn off the heater and allow the device to cool down slowly to room temperature under the inert atmosphere.

- Once at room temperature, the device can be removed for electrical characterization.

- 2. Protocol for Surface Treatment of SiO<sub>2</sub> with Octadecyltrichlorosilane (OTS)

This protocol outlines the steps for treating a silicon dioxide gate dielectric with an OTS self-assembled monolayer to improve the **pentacene**-dielectric interface.

- Objective: To create a hydrophobic and smooth dielectric surface that promotes better ordering of pentacene molecules, leading to improved device performance.

- Materials:

- Si/SiO<sub>2</sub> substrate.

- Piranha solution (H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> = 3:1) EXTREME CAUTION IS ADVISED.

- o Deionized (DI) water.

- Anhydrous toluene.

- Octadecyltrichlorosilane (OTS).

- Nitrogen gas for drying.

- Sonicator bath.

- o Oven.

- Procedure:

### Substrate Cleaning:

- Clean the Si/SiO<sub>2</sub> substrate by sonicating in acetone and then isopropanol for 15 minutes each.

- Rinse thoroughly with DI water and dry with nitrogen gas.

- Perform a piranha clean by immersing the substrate in the solution for 15 minutes to create a hydrophilic surface with -OH groups. (Warning: Piranha solution is extremely corrosive and reactive. Handle with extreme care in a fume hood with appropriate personal protective equipment).

- Rinse the substrate extensively with DI water and dry with nitrogen.

- Bake the substrate in an oven at 120°C for 30 minutes to remove any residual water.

- OTS Monolayer Formation:

- Prepare a dilute solution of OTS in anhydrous toluene (e.g., 1-10 mM) inside a glovebox to avoid moisture.

- Immerse the cleaned and dried substrate in the OTS solution for a specified time (e.g.,

1-2 hours) to allow for the formation of the self-assembled monolayer.

- After immersion, rinse the substrate with fresh anhydrous toluene to remove any excess, unreacted OTS.

- Dry the substrate with nitrogen gas.

- Curing:

- Bake the OTS-treated substrate at 120°C for 1 hour to cure the monolayer.

- The substrate is now ready for **pentacene** deposition.

## **Visual Guides**

Click to download full resolution via product page

Caption: Troubleshooting workflow for high leakage current in **pentacene** transistors.

### Click to download full resolution via product page

Caption: Experimental workflow for fabricating low-leakage **pentacene** transistors.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. researchgate.net [researchgate.net]

- 2. researchgate.net [researchgate.net]

- 3. pubs.aip.org [pubs.aip.org]

- 4. oam-rc.inoe.ro [oam-rc.inoe.ro]

- 5. mdpi.com [mdpi.com]

- 6. researchgate.net [researchgate.net]

- 7. lirias.kuleuven.be [lirias.kuleuven.be]

- 8. Effect of dielectric layers on device stability of pentacene-based field-effect transistors -Physical Chemistry Chemical Physics (RSC Publishing) [pubs.rsc.org]

- 9. Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance PMC [pmc.ncbi.nlm.nih.gov]

- 10. individual.utoronto.ca [individual.utoronto.ca]

- 11. researchgate.net [researchgate.net]

- 12. Post annealing effects on the electrical characteristics of pentacene thin film transistors on flexible substrates PubMed [pubmed.ncbi.nlm.nih.gov]

- 13. researchgate.net [researchgate.net]

- 14. Piezoelectric Ultrasonic Transducer with High Performance OTFT for Flow Rate,

Occlusion and Bubble Detection Portable Peritoneal Dialysis System | MDPI [mdpi.com]

- 15. researchgate.net [researchgate.net]

- 16. sol-gel.net [sol-gel.net]

- To cite this document: BenchChem. [Technical Support Center: Pentacene Transistor Fabrication & Troubleshooting]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b032325#reducing-leakage-current-in-pentacene-transistors]

### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com