# The Bedrock of Plastic Electronics: A Technical Guide to Pentacene-Based Device Physics

Author: BenchChem Technical Support Team. Date: December 2025

For Researchers, Scientists, and Drug Development Professionals

**Pentacene**, a polycyclic aromatic hydrocarbon, has established itself as a benchmark organic semiconductor, paving the way for advancements in flexible, low-cost electronics. Its favorable charge transport properties and amenability to thin-film deposition make it a cornerstone material for Organic Field-Effect Transistors (OFETs), sensors, and other optoelectronic devices. This guide delves into the fundamental principles governing the physics of **pentacene**-based devices, offering an in-depth exploration of charge transport mechanisms, device architecture, the critical role of interfaces, and the experimental protocols for their fabrication and characterization.

## **Core Principles of Device Operation**

The workhorse of **pentacene**-based electronics is the OFET, a device analogous to the silicon-based MOSFET. An OFET consists of a semiconductor layer, a gate dielectric, and three electrodes: the gate, the source, and the drain. The application of a voltage to the gate electrode creates an electric field across the dielectric, which in turn induces an accumulation of charge carriers (holes in the case of p-type **pentacene**) at the semiconductor-dielectric interface. This accumulation forms a conductive channel, allowing current to flow from the source to the drain when a voltage is applied between them. The performance of an OFET is primarily evaluated by its charge carrier mobility ( $\mu$ ), on/off current ratio (lon/loff), and threshold voltage (Vth).

## Charge Transport in Pentacene: A Tale of Two Mechanisms

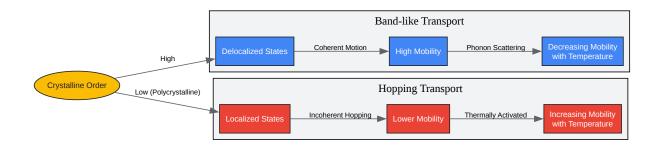

The movement of charge carriers through the **pentacene** crystalline structure is a complex process that is still a subject of intense research. Two primary models are used to describe this phenomenon: band-like transport and hopping transport.[1][2]

- Band-like Transport: In highly ordered single crystals of pentacene, the molecular orbitals of

adjacent molecules can overlap significantly, leading to the formation of delocalized

electronic bands.[2] In this regime, charge carriers can move freely through these bands,

and their mobility typically decreases with increasing temperature due to scattering events

with lattice vibrations (phonons).[2]

- Hopping Transport: In polycrystalline thin films, which are more common in practical devices, the presence of grain boundaries and structural defects disrupts the formation of continuous energy bands.[1] Charge transport in this scenario is dominated by a hopping mechanism, where charge carriers are localized on individual pentacene molecules and "hop" to adjacent molecules. This process is thermally activated, meaning that mobility generally increases with temperature as carriers gain enough energy to overcome the potential barriers between molecules.[1]

In reality, the charge transport in most **pentacene** thin films is a combination of these two mechanisms, with one dominating over the other depending on the degree of molecular ordering and the operating temperature.[1]

Click to download full resolution via product page

Caption: Conceptual diagram of charge transport mechanisms in pentacene.

## **Device Architecture: Top vs. Bottom Contact**

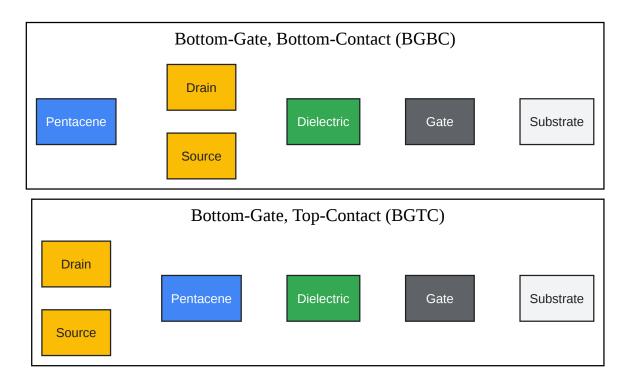

**Pentacene**-based OFETs are typically fabricated in one of two primary architectures: bottom-gate, top-contact (BGTC) or bottom-gate, bottom-contact (BGBC).[3]

- Bottom-Gate, Top-Contact (BGTC): In this configuration, the gate electrode and dielectric

layer are deposited first, followed by the pentacene semiconductor layer. The source and

drain electrodes are then deposited on top of the pentacene. This architecture generally

leads to lower contact resistance and better device performance because the metal is

deposited onto the organic film, often resulting in a more intimate contact.[4]

- Bottom-Gate, Bottom-Contact (BGBC): Here, the source and drain electrodes are patterned

on the dielectric layer before the deposition of the **pentacene** semiconductor. While this

method can be simpler for fabrication, it often results in higher contact resistance due to the

less ideal interface formed between the **pentacene** and the pre-deposited electrodes.[4]

Click to download full resolution via product page

**Caption:** Common device architectures for **pentacene**-based OFETs.

### The Critical Role of Interfaces

The performance of **pentacene**-based devices is exquisitely sensitive to the properties of the interfaces, particularly the semiconductor-dielectric and semiconductor-electrode interfaces.

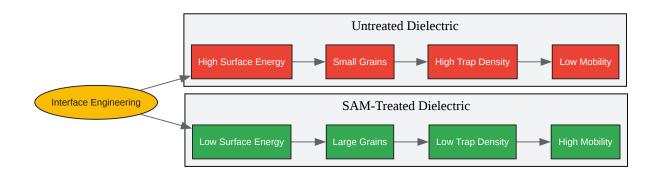

### Semiconductor-Dielectric Interface

The first few molecular layers of **pentacene** at the dielectric interface are where the conductive channel is formed. Therefore, the properties of this interface are paramount to achieving high device performance. A smooth dielectric surface with low surface energy can promote the growth of larger **pentacene** grains with better molecular ordering, leading to higher charge carrier mobility.[5] Surface treatments of the dielectric layer, often with self-assembled monolayers (SAMs) like octadecyltrichlorosilane (OTS), are commonly employed to modify the surface energy and reduce charge trapping sites.[5][6]

Click to download full resolution via product page

**Caption:** Impact of dielectric interface engineering on **pentacene** film and performance.

### Semiconductor-Electrode Interface

The efficiency of charge injection from the source electrode into the **pentacene** layer is governed by the energy barrier at this interface. A large injection barrier leads to high contact

resistance, which can significantly limit the overall device performance, especially in short-channel devices.[7] The choice of electrode material and the cleanliness of the interface are crucial factors in minimizing contact resistance. Gold (Au) is a commonly used electrode material due to its high work function, which generally results in a smaller hole injection barrier with **pentacene**.

## **Quantitative Performance Data**

The performance of **pentacene**-based OFETs can vary significantly depending on the fabrication conditions. The following tables summarize key performance parameters reported in the literature for different dielectric materials and device architectures.

Table 1: Performance of **Pentacene** OFETs with Different Dielectric Materials

| Dielectric<br>Material         | Mobility<br>(cm²/Vs) | On/Off Ratio          | Threshold<br>Voltage (V) | Reference |

|--------------------------------|----------------------|-----------------------|--------------------------|-----------|

| SiO <sub>2</sub>               | ~0.2                 | 10 <sup>5</sup>       | -                        | [8]       |

| SiO <sub>2</sub> (OTS treated) | 1.25                 | -                     | -                        | [9]       |

| Al <sub>2</sub> O <sub>3</sub> | -                    | 10 <sup>6</sup>       | -0.99                    | [10]      |

| HfO <sub>2</sub>               | -                    | 2 x 10 <sup>7</sup>   | -0.75                    | [10][11]  |

| HfON                           | 0.39                 | 1.1 x 10 <sup>4</sup> | -                        | [12]      |

| PMMA                           | 0.14                 | 197                   | -                        | [13]      |

| Polystyrene (PS)               | -                    | >103                  | -                        | [14]      |

| Mica (OTMS<br>treated)         | 0.31                 | -                     | -                        | [13]      |

Table 2: Contact Resistance in Pentacene OFETs

| Device<br>Architecture | Electrode<br>Material | Contact<br>Resistance<br>(Ω·cm) | Measurement<br>Conditions                                | Reference |

|------------------------|-----------------------|---------------------------------|----------------------------------------------------------|-----------|

| Top-Contact            | Au                    | ~1 k                            | High gate<br>voltage                                     | [7]       |

| Bottom-Contact         | Au                    | ~40 k                           | -                                                        | [15]      |

| Top-Contact            | Au                    | ~3 k                            | -                                                        | [15]      |

| Top-Contact            | Pd                    | -                               | Gate bias dependent ( $10^6$ - $10^{10}$ $\Omega$ total) |           |

| Top-Contact            | Au/Pd                 | ~1.3 k                          | High gate<br>voltage                                     | [15]      |

## **Experimental Protocols**

The fabrication and characterization of **pentacene**-based devices require careful control over deposition conditions and measurement procedures.

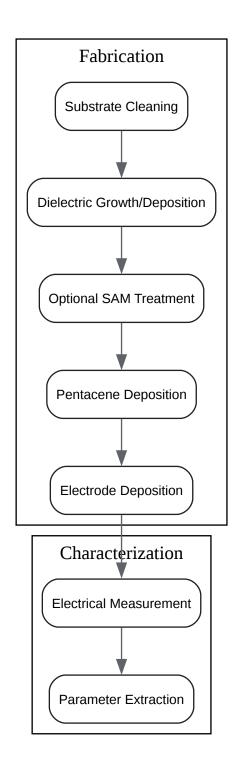

## Fabrication of a Bottom-Gate, Top-Contact Pentacene OFET

The following is a generalized protocol for the fabrication of a BGTC **pentacene** OFET on a silicon substrate.

Click to download full resolution via product page

Caption: Generalized workflow for pentacene OFET fabrication and characterization.

- 1. Substrate Preparation:

- A heavily doped silicon wafer, which serves as the gate electrode, is used as the substrate.

### Foundational & Exploratory

- The substrate is cleaned sequentially in ultrasonic baths of acetone and isopropyl alcohol,

each for 15 minutes.[16]

- After each solvent cleaning, the substrate is rinsed with deionized water and dried with nitrogen gas.[16]

- An optional ozone treatment for 15 minutes can be performed to make the surface more hydrophilic and remove organic residues.[16]

- 2. Gate Dielectric Formation:

- A layer of silicon dioxide (SiO<sub>2</sub>), typically 100-300 nm thick, is grown on the silicon substrate via thermal oxidation. This layer acts as the gate dielectric.[17]

- 3. (Optional) Surface Treatment with Self-Assembled Monolayer (SAM):

- To improve the **pentacene** film quality, the SiO<sub>2</sub> surface can be treated with a SAM.

- For an octadecyltrichlorosilane (OTS) treatment, the substrate is immersed in a dilute solution of OTS in a nonpolar solvent like n-hexane or toluene for a specified time, followed by rinsing and annealing.[9]

- 4. Pentacene Deposition:

- A thin film of **pentacene** (typically 30-50 nm) is deposited onto the dielectric surface.

- Thermal evaporation under high vacuum (e.g., 10<sup>-6</sup> torr) is a common deposition method.

The substrate can be held at an elevated temperature (e.g., 60-80 °C) during deposition to promote better film crystallinity.[18]

- 5. Source and Drain Electrode Deposition:

- Gold (Au) is commonly used for the source and drain electrodes.

- The electrodes are deposited on top of the **pentacene** layer through a shadow mask via thermal evaporation to a thickness of 30-50 nm. The shadow mask defines the channel length and width of the transistor.[19]

### **Electrical Characterization**

The electrical performance of the fabricated OFETs is characterized using a semiconductor parameter analyzer.

- 1. Output Characteristics:

- The drain current (ID) is measured as a function of the drain-source voltage (VDS) for various constant gate-source voltages (VGS).

- These curves show the linear and saturation regimes of transistor operation.

- 2. Transfer Characteristics:

- The drain current (ID) is measured as a function of the gate-source voltage (VGS) at a constant, high drain-source voltage (VDS) (to ensure operation in the saturation regime).

- From the transfer curve, key performance metrics are extracted:

- $\circ$  Field-Effect Mobility ( $\mu$ ): Calculated from the slope of the (ID)1/2 vs. VGS plot in the saturation regime.

- On/Off Ratio (Ion/Ioff): The ratio of the maximum drain current (Ion) to the minimum drain current (Ioff).

- Threshold Voltage (Vth): The gate voltage at which the conductive channel begins to form, determined from the x-intercept of the linear region of the (ID)1/2 vs. VGS plot.

### Conclusion

**Pentacene** remains a vital material in the field of organic electronics, providing a platform for both fundamental research and the development of novel applications. A thorough understanding of its charge transport properties, the nuances of device architecture, and the critical influence of interfaces is essential for designing and fabricating high-performance **pentacene**-based devices. The continued optimization of fabrication processes and the exploration of new interface engineering techniques will undoubtedly lead to further improvements in the performance and stability of these devices, expanding their potential for use in a wide array of future technologies.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. researchgate.net [researchgate.net]

- 2. pubs.aip.org [pubs.aip.org]

- 3. journal.jjss.co.in [journal.jjss.co.in]

- 4. pubs.aip.org [pubs.aip.org]

- 5. crg.postech.ac.kr [crg.postech.ac.kr]

- 6. researchgate.net [researchgate.net]

- 7. pubs.aip.org [pubs.aip.org]

- 8. researchgate.net [researchgate.net]

- 9. individual.utoronto.ca [individual.utoronto.ca]

- 10. oam-rc.inoe.ro [oam-rc.inoe.ro]

- 11. OAM-RC :: Articles [oam-rc.inoe.ro]

- 12. researchgate.net [researchgate.net]

- 13. researchgate.net [researchgate.net]

- 14. researchgate.net [researchgate.net]

- 15. pubs.aip.org [pubs.aip.org]

- 16. scribd.com [scribd.com]

- 17. pubs.aip.org [pubs.aip.org]

- 18. pubs.aip.org [pubs.aip.org]

- 19. Fabrication, TCAD and compact model verification of TIPS-pentacene organic thin film transistor [jos.ac.cn]

- To cite this document: BenchChem. [The Bedrock of Plastic Electronics: A Technical Guide to Pentacene-Based Device Physics]. BenchChem, [2025]. [Online PDF]. Available at:

[https://www.benchchem.com/product/b032325#basic-principles-of-pentacene-based-device-physics]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com