# Navigating the Nuances of Pentacene: A Guide to Reproducible Device Fabrication

Author: BenchChem Technical Support Team. Date: December 2025

For researchers, scientists, and professionals in drug development, the promise of flexible, low-cost organic electronics hinges on the ability to reliably fabricate high-performance devices. **Pentacene** has long been a benchmark p-type organic semiconductor, yet achieving consistent device performance remains a significant challenge. This guide provides an objective comparison of fabrication methodologies, supported by experimental data, to illuminate the path toward reproducible **pentacene**-based devices.

The performance of **pentacene** thin-film transistors (TFTs) is critically dependent on a multitude of factors, including the deposition method, substrate preparation, and the choice of dielectric materials. Variations in these parameters can lead to significant differences in key performance metrics such as charge carrier mobility ( $\mu$ ), the on/off current ratio (lon/loff), and threshold voltage (Vth). Understanding these variables is paramount for researchers aiming to produce reliable and comparable results.

## **Comparative Performance Metrics**

The following table summarizes key performance metrics for **pentacene** TFTs fabricated under different conditions, offering a glimpse into the variability and potential of various techniques. This data, compiled from multiple studies, highlights the importance of process optimization for achieving high-performance, reproducible devices.

| Depositio<br>n Method                 | Dielectric         | Substrate<br>Treatmen<br>t | Mobility<br>(μ)<br>(cm²/Vs) | On/Off<br>Ratio<br>(lon/loff) | Threshol<br>d Voltage<br>(Vth) (V) | Referenc<br>e |

|---------------------------------------|--------------------|----------------------------|-----------------------------|-------------------------------|------------------------------------|---------------|

| Thermal<br>Evaporatio<br>n            | SiO <sub>2</sub>   | OTS-18                     | 0.37 ± 0.01                 | > 105                         | -                                  | [1]           |

| Thermal<br>Evaporatio<br>n            | SiO2               | OTS-8                      | 0.84 ± 0.02                 | > 105                         | -                                  | [1]           |

| Thermal<br>Evaporatio<br>n            | SiO <sub>2</sub>   | -                          | 1.10                        | 0.48 x 10 <sup>5</sup>        | -2.71                              | [2]           |

| Organic Vapor Phase Deposition (OVPD) | -                  | -                          | 0.94 ± 0.11                 | -                             | -3.2 ± 0.4                         | [3]           |

| Solution Processing (TIPS- Pentacene) | -                  | OTS                        | 0.4                         | -                             | -                                  | [4]           |

| Thermal<br>Evaporatio<br>n            | PVP                | -                          | 0.16                        | -                             | -                                  | [5]           |

| Thermal<br>Evaporatio<br>n            | PVA/PVP<br>Bilayer | -                          | 1.12                        | -                             | -                                  | [5]           |

## The Critical Role of Fabrication Protocols

Reproducibility in **pentacene** device fabrication is intrinsically linked to meticulous control over the experimental process. Below are detailed methodologies for key steps in the fabrication of a common top-contact, bottom-gate **pentacene** TFT architecture.

## **Experimental Workflow**

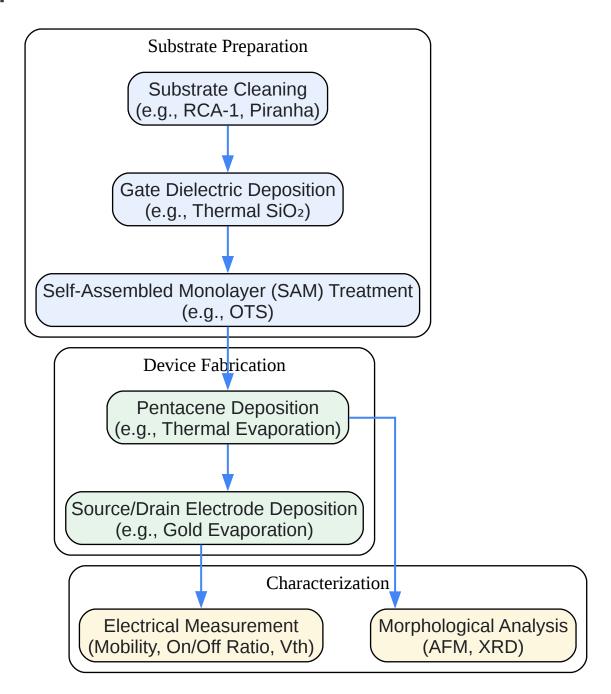

Click to download full resolution via product page

Caption: A typical workflow for the fabrication and characterization of **pentacene** TFTs.

# **Detailed Methodologies**

1. Substrate Preparation:

- Cleaning: The process typically begins with a highly doped silicon wafer that serves as the

gate electrode. A common cleaning procedure involves sequential ultrasonication in

deionized water, acetone, and isopropanol. More rigorous cleaning methods like RCA-1 or

Piranha etching can also be employed to remove organic and inorganic contaminants.

- Gate Dielectric Formation: A layer of silicon dioxide (SiO<sub>2</sub>), typically 200-300 nm thick, is grown thermally on the silicon wafer to act as the gate dielectric.[6]

- Surface Treatment: To improve the interface quality and promote better **pentacene** film growth, the SiO<sub>2</sub> surface is often treated with a self-assembled monolayer (SAM), such as octadecyltrichlorosilane (OTS).[7] This treatment modifies the surface energy, influencing the morphology and crystallinity of the subsequently deposited **pentacene** film.[7]

### 2. **Pentacene** Deposition:

- Thermal Evaporation: This is a widely used technique for depositing high-purity **pentacene** thin films.[4] The substrate is placed in a high-vacuum chamber (pressure < 10<sup>-6</sup> Torr), and **pentacene** is heated in a crucible.[6] The deposition rate is a critical parameter, typically maintained at 0.1-0.5 Å/s, to achieve a final film thickness of 40-60 nm.[6] The substrate temperature during deposition can also be controlled (e.g., held at 60°C) to influence film crystallinity.[6]

- Organic Vapor Phase Deposition (OVPD): In OVPD, an inert carrier gas transports the evaporated organic material into a deposition chamber.[8] This method offers advantages in terms of deposition rate control and scalability.[3][8]

### 3. Electrode Deposition:

• Top-Contact Configuration: For top-contact devices, the source and drain electrodes are deposited onto the **pentacene** layer. Gold (Au) is a common choice due to its high work function, which facilitates efficient hole injection into the **pentacene**.[6] The electrodes are typically deposited through a shadow mask via thermal evaporation.

#### 4. Device Characterization:

• Electrical Measurements: The fabricated TFTs are characterized using a semiconductor parameter analyzer in a controlled environment (e.g., in a vacuum or inert atmosphere) to

extract key performance metrics.

Morphological and Structural Analysis: Techniques such as Atomic Force Microscopy (AFM)

and X-ray Diffraction (XRD) are used to investigate the morphology and crystal structure of

the pentacene film, which are strongly correlated with device performance.

# Alternatives to Pentacene for Enhanced Reproducibility

While **pentacene** remains a valuable research tool, its inherent instability in air and low solubility in common solvents pose challenges for large-scale, reproducible manufacturing.[9] [10][11] This has spurred the development of **pentacene** derivatives and other organic semiconductors.

TIPS-**Pentacene** (6,13-bis(triisopropylsilylethynyl)**pentacene**): This derivative incorporates bulky side groups that significantly improve its solubility, allowing for solution-based processing techniques like spin-coating and inkjet printing.[12] While solution processing can introduce its own set of variability, it offers the potential for low-cost, large-area fabrication. The mobility of TIPS-**pentacene** devices is highly dependent on processing conditions but can reach values comparable to thermally evaporated **pentacene**.[4][10]

# **Factors Influencing Reproducibility**

Several critical factors have been identified as major contributors to the variability in **pentacene** device performance:

- Purity of Pentacene: The presence of impurities can introduce traps and degrade device performance.

- Deposition Rate and Substrate Temperature: These parameters significantly influence the morphology and crystallinity of the **pentacene** film.[13]

- Dielectric Surface: The chemical and physical properties of the gate dielectric surface play a

crucial role in the ordering of the first few **pentacene** monolayers, which dominate charge

transport.[7]

• Environmental Factors: **Pentacene** is sensitive to oxygen and moisture, which can lead to device degradation over time.[9][14] Encapsulation is often necessary to ensure long-term stability.

By carefully controlling these factors and adhering to well-documented experimental protocols, researchers can significantly improve the reproducibility of **pentacene** device fabrication, paving the way for more reliable and impactful research in the field of organic electronics.

## **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. researchgate.net [researchgate.net]

- 2. Characteristics of pentacene organic thin film transistor with top gate and bottom contact [cpsjournals.cn]

- 3. pubs.aip.org [pubs.aip.org]

- 4. Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance - PMC [pmc.ncbi.nlm.nih.gov]

- 5. Performance Enhancement of Pentacene-Based Organic Thin-Film Transistors Using a High-K PVA/Low-K PVP Bilayer as the Gate Insulator PMC [pmc.ncbi.nlm.nih.gov]

- 6. benchchem.com [benchchem.com]

- 7. Effect of dielectric layers on device stability of pentacene-based field-effect transistors Physical Chemistry Chemical Physics (RSC Publishing) [pubs.rsc.org]

- 8. researchgate.net [researchgate.net]

- 9. Pentacene Wikipedia [en.wikipedia.org]

- 10. encyclopedia.pub [encyclopedia.pub]

- 11. mdpi.com [mdpi.com]

- 12. Fabrication, TCAD and compact model verification of TIPS-pentacene organic thin film transistor [jos.ac.cn]

- 13. researchgate.net [researchgate.net]

- 14. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Navigating the Nuances of Pentacene: A Guide to Reproducible Device Fabrication]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b032325#assessing-the-reproducibility-of-pentacene-device-fabrication]

### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com