# Technical Support Center: Large-Scale Pentacene Device Fabrication

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |

|----------------------|-----------|-----------|

| Compound Name:       | Pentacene |           |

| Cat. No.:            | B032325   | Get Quote |

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to address common challenges encountered during the large-scale fabrication of **pentacene**-based electronic devices.

### **Frequently Asked Questions (FAQs)**

Q1: What are the most common challenges in large-scale pentacene device fabrication?

A1: Researchers frequently encounter challenges related to:

- Contact Resistance: High contact resistance between the source/drain electrodes and the pentacene layer can dominate device performance, particularly in short-channel transistors.

[1] This resistance is influenced by the electrode geometry and the metal-pentacene interface.

- Film Morphology and Polymorphism: Pentacene can crystallize in different structures, primarily a "thin-film phase" and a "bulk phase".[2][3] Controlling the growth to achieve large, well-ordered crystalline grains with minimal defects is crucial for high charge carrier mobility.

[4][5] The presence of multiple phases can lead to charge trapping at grain boundaries.[6]

- Device Stability: **Pentacene** is sensitive to oxygen, moisture, and light, which can lead to performance degradation over time.[7][8][9] This instability is a major hurdle for commercialization.[8]

#### Troubleshooting & Optimization

- Solution Processing: While offering a route to low-cost, large-area fabrication, the low solubility of pentacene in common solvents presents a significant challenge.[7][10] This has led to the development of soluble pentacene precursors and derivatives like TIPS-pentacene.[7][11]

- Dielectric Interface Quality: The interface between the **pentacene** active layer and the gate dielectric is critical. A poor interface can lead to charge trapping and reduced mobility.[12][13]

Q2: Why is the choice between top-contact and bottom-contact geometries important?

A2: The device geometry significantly impacts performance. In bottom-contact (BC) devices, the **pentacene** is deposited onto the pre-patterned source and drain electrodes. The growth of **pentacene** on the metal contacts can be different from its growth on the dielectric, potentially leading to altered morphology and higher contact resistance.[1] In top-contact (TC) devices, the electrodes are deposited on top of the **pentacene** film. This can sometimes result in lower contact resistance but may introduce the risk of damaging the organic layer during metal deposition.[1]

Q3: What is polymorphism in **pentacene** thin films and how does it affect device performance?

A3: Polymorphism refers to the ability of **pentacene** to exist in multiple crystalline structures. The two most common polymorphs in vapor-deposited thin films are the "thin-film phase" and the "bulk phase".[2] These phases have different intermolecular spacings.[3][14] The thin-film phase often forms first, especially on substrates like SiO2.[2] The presence of both phases in a film can create grain boundaries that act as traps for charge carriers, thereby reducing the overall device mobility.[6] The ratio of these phases is influenced by factors like film thickness and substrate temperature during deposition.[2]

Q4: What are the main causes of device degradation in **pentacene** transistors?

A4: The primary causes of degradation in **pentacene** devices are exposure to ambient conditions, specifically oxygen and moisture, as well as light.[7][9] **Pentacene** can be oxidized, forming **pentacene**quinone, which acts as a charge trap and degrades device performance.[7] [8] Moisture in the **pentacene** film can also lead to an increase in threshold voltage and subthreshold swing.[9] These degradation mechanisms can lead to a significant decrease in mobility and on-current over time.[9]

Q5: What are TIPS-pentacene and pentacene precursors, and why are they used?

A5: TIPS-pentacene (6,13-bis(triisopropylsilylethynyl) pentacene) is a derivative of pentacene where bulky triisopropylsilyl-ethynyl groups are attached to the pentacene core.[15][16] This modification significantly improves its solubility in organic solvents, making it suitable for solution-based deposition techniques like spin-coating and inkjet printing.[15][16] Pentacene precursors are molecules that can be dissolved and deposited from solution and then converted into pentacene through a subsequent process, typically heating.[11][17] Both approaches aim to overcome the poor solubility of pristine pentacene to enable large-scale, low-cost fabrication via solution processing.[7][11]

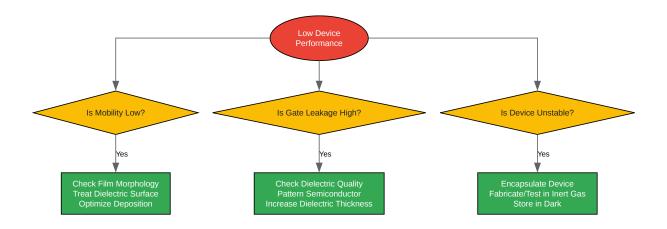

# **Troubleshooting Guides Issue 1: Low Carrier Mobility**

Symptoms: The calculated field-effect mobility of your **pentacene** thin-film transistor (TFT) is significantly lower than expected values (typically < 0.1 cm<sup>2</sup>/Vs).

| Cause                                | Recommended Action                                                                                                                                                                                                                                                                                                |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Poor Film Crystallinity/Small Grains | Optimize deposition parameters. Increasing the substrate temperature during deposition can decrease nucleation density and lead to larger grain sizes.[18][19] For solution-processed films, the choice of solvent and deposition technique (e.g., spin coating speed) can greatly influence film morphology.[16] |  |

| Presence of Polymorphs               | Control the film thickness and substrate temperature to favor the growth of a single, desired polymorph. Characterize the film structure using techniques like X-ray diffraction (XRD).[2][7]                                                                                                                     |  |

| Sub-optimal Dielectric Interface     | Treat the dielectric surface with a self-assembled monolayer (SAM) such as hexamethyldisilazane (HMDS) or octadecyltrichlorosilane (OTS) prior to pentacene deposition.[7][13] This can improve molecular ordering and device performance.                                                                        |  |

| Impurities in Pentacene Source       | Use high-purity pentacene. Impurities like pentacenequinone can act as charge traps and also disrupt crystal growth, leading to smaller grains and lower mobility.[20]                                                                                                                                            |  |

| High Contact Resistance              | See Troubleshooting Issue 2.                                                                                                                                                                                                                                                                                      |  |

### **Issue 2: High Contact Resistance**

Symptoms: The total device resistance is high even at strong gate bias. The output characteristics (Id-Vd) are non-linear at low drain voltages.

| Cause                                                | Recommended Action                                                                                                                                                                                   |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Energy Barrier at Metal-Pentacene Interface          | The choice of electrode metal is crucial. Gold (Au) is commonly used for its work function, which generally provides a good energetic alignment with the HOMO level of pentacene for hole injection. |

| Poor Pentacene Growth on Electrodes (Bottom-Contact) | In bottom-contact devices, pentacene growth on the metal electrodes can be disordered.[1]  Consider using a top-contact geometry where the electrodes are deposited on top of the pentacene film.    |

| Device Geometry                                      | Contact resistance becomes more dominant in short-channel devices.[1] Fabricate devices with varying channel lengths to extract the contact resistance and assess its impact.                        |

| Gate Bias Dependence                                 | Contact resistance in pentacene TFTs is often dependent on the gate voltage.[12] Characterize this dependence to understand its contribution to the overall device performance.                      |

### **Issue 3: Device Instability and Rapid Degradation**

Symptoms: Device performance (mobility, on/off ratio, threshold voltage) degrades quickly when measured or stored in ambient air.

| Cause                  | Recommended Action                                                                                                                                                 |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Oxidation of Pentacene | Fabricate and test devices in an inert atmosphere (e.g., a nitrogen-filled glovebox) to minimize exposure to oxygen and moisture.[7]                               |  |

| Moisture Trapping      | Ensure all substrates and materials are thoroughly dried before fabrication. Annealing the device after fabrication can sometimes help to remove trapped moisture. |  |

| Encapsulation          | For long-term stability, encapsulate the finished devices with a suitable barrier layer to protect the pentacene from the ambient environment.                     |  |

| Light Exposure         | Store devices in the dark when not in use, as pentacene is sensitive to light.[8]                                                                                  |  |

### **Issue 4: High Gate Leakage Current**

Symptoms: A significant current flows through the gate dielectric when a gate voltage is applied, leading to a low on/off ratio.

| Cause                           | Recommended Action                                                                                                                                                                                                    |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Poor Dielectric Quality         | Ensure the gate dielectric is free of pinholes and defects. For solution-processed dielectrics, optimize the coating and curing/annealing process.[21] For thermally grown SiO <sub>2</sub> , verify its quality.[22] |

| Rough Dielectric Surface        | A rough dielectric surface can lead to a non-<br>uniform pentacene film and potential shorts.<br>Characterize the surface roughness with Atomic<br>Force Microscopy (AFM).                                            |

| Unpatterned Semiconductor Layer | If the pentacene layer covers the entire substrate, it can lead to leakage paths. Pattern the pentacene to isolate individual devices.[22]                                                                            |

| Thin Dielectric Layer           | While a thin dielectric can improve gate coupling, it also increases the risk of leakage.  Consider using a slightly thicker dielectric layer if leakage is a persistent issue.[21]                                   |

# **Quantitative Data Summary**

Table 1: Typical Performance Parameters of **Pentacene** TFTs

| Parameter                    | Typical Value<br>Range                 | Key Influencing<br>Factors                                                    | Citation |

|------------------------------|----------------------------------------|-------------------------------------------------------------------------------|----------|

| Field-Effect Mobility<br>(μ) | 0.1 - 1.0 cm²/Vs (can exceed 1 cm²/Vs) | Film crystallinity, grain size, interface quality, purity                     | [7][14]  |

| On/Off Current Ratio         | 10 <sup>4</sup> - 10 <sup>8</sup>      | Gate leakage, off-<br>state current, trap<br>states                           | [23][24] |

| Threshold Voltage<br>(Vth)   | 0 V to -20 V                           | Interface traps, fixed charges in the dielectric, work function of electrodes | [12][24] |

| Contact Resistance<br>(Rc)   | $10^3$ - $10^{10}$ Ω                   | Electrode metal,<br>device geometry (TC<br>vs. BC), gate voltage              | [1]      |

Table 2: Influence of Deposition Parameters on Pentacene TFT Performance

| Deposition<br>Parameter  | Effect on<br>Film/Device                                                                              | Typical<br>Values/Conditions | Citation |

|--------------------------|-------------------------------------------------------------------------------------------------------|------------------------------|----------|

| Substrate<br>Temperature | Higher temperature<br>generally leads to<br>larger grain size and<br>higher mobility.                 | 25°C - 90°C                  | [2][7]   |

| Deposition Rate          | Slower rates can result in more ordered film growth.                                                  | 0.1 - 1.0 Å/s                | [7][24]  |

| Film Thickness           | Influences the ratio of thin-film to bulk phase polymorphs.                                           | 10 - 100 nm                  | [2][7]   |

| Annealing<br>Temperature | Post-deposition annealing can improve crystallinity, but excessive temperatures can degrade the film. | 50°C - 70°C                  | [25]     |

## **Experimental Protocols**

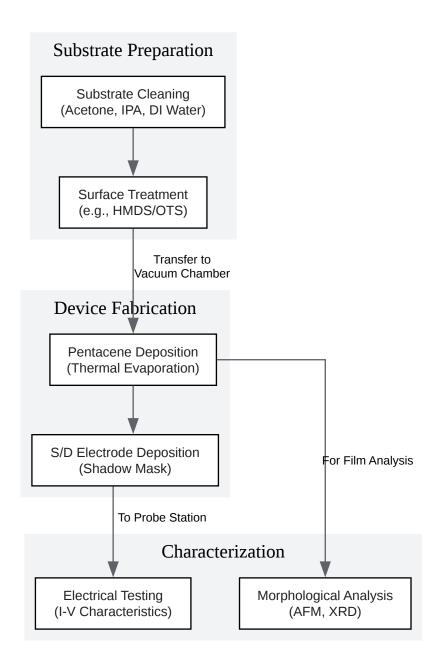

#### **Protocol 1: Fabrication of a Top-Contact Pentacene TFT**

- Substrate Cleaning: Begin with a heavily doped p-type silicon wafer (acting as the gate electrode) with a thermally grown SiO<sub>2</sub> layer (gate dielectric). Clean the substrate sequentially in ultrasonic baths of acetone and isopropyl alcohol, followed by rinsing with deionized water and drying with nitrogen.

- Dielectric Surface Treatment (Optional but Recommended): Apply a self-assembled monolayer (SAM) like HMDS or OTS to the SiO<sub>2</sub> surface to improve **pentacene** adhesion and ordering. This is often done by spin-coating the SAM solution or through vapor deposition.

- **Pentacene** Deposition: Deposit a **pentacene** thin film (typically 30-60 nm) onto the substrate using thermal evaporation in a high-vacuum chamber (base pressure  $< 10^{-6}$  Torr). Maintain

the substrate at a constant temperature (e.g., 70°C) during deposition at a controlled rate (e.g., 0.5 Å/s).[7]

- Source/Drain Electrode Deposition: Through a shadow mask, thermally evaporate the source and drain electrodes (e.g., 50 nm of gold) on top of the **pentacene** layer. This defines the channel length and width of the transistor.

- Annealing (Optional): Post-fabrication annealing can be performed in an inert atmosphere to improve device performance.

- Characterization: Electrically characterize the device in an inert atmosphere or vacuum using a semiconductor parameter analyzer to obtain the output and transfer characteristics.

# Protocol 2: Characterization of Pentacene Film Polymorphism using XRD

- Sample Preparation: Deposit **pentacene** films of varying thicknesses (e.g., 10 nm, 50 nm, 100 nm) on the desired substrate (e.g., SiO<sub>2</sub>/Si) under controlled deposition conditions (substrate temperature, deposition rate).

- XRD Measurement: Perform X-ray diffraction measurements in a conventional  $\theta/2\theta$  mode.

- Data Analysis: Analyze the resulting diffraction patterns. The presence of peaks corresponding to different (00l) reflections will indicate the crystalline phases present. The thin-film phase of **pentacene** typically has a larger d-spacing (around 15.4 Å) compared to the bulk phase (around 14.4 Å).[2][5] The relative intensity of these peaks can be used to estimate the proportion of each phase in the film.

#### **Visualizations**

Click to download full resolution via product page

Caption: Workflow for top-contact **pentacene** TFT fabrication.

Click to download full resolution via product page

Caption: Troubleshooting logic for common **pentacene** device issues.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. pubs.aip.org [pubs.aip.org]

- 2. pubs.aip.org [pubs.aip.org]

- 3. pubs.acs.org [pubs.acs.org]

- 4. rug.nl [rug.nl]

- 5. aquila.infn.it [aquila.infn.it]

- 6. Self-Limited Growth in Pentacene Thin Films PMC [pmc.ncbi.nlm.nih.gov]

- 7. Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance PMC [pmc.ncbi.nlm.nih.gov]

#### Troubleshooting & Optimization

- 8. Pentacene Wikipedia [en.wikipedia.org]

- 9. researchgate.net [researchgate.net]

- 10. pubs.acs.org [pubs.acs.org]

- 11. pubs.acs.org [pubs.acs.org]

- 12. rogersgroup.northwestern.edu [rogersgroup.northwestern.edu]

- 13. researchgate.net [researchgate.net]

- 14. mdpi.com [mdpi.com]

- 15. repositorium.uminho.pt [repositorium.uminho.pt]

- 16. pubs.aip.org [pubs.aip.org]

- 17. Kyoto University Research Information Repository [repository.kulib.kyoto-u.ac.jp]

- 18. researchgate.net [researchgate.net]

- 19. Role of Graphene Topography in the Initial Stages of Pentacene Layer Growth PMC [pmc.ncbi.nlm.nih.gov]

- 20. pubs.acs.org [pubs.acs.org]

- 21. researchgate.net [researchgate.net]

- 22. researchgate.net [researchgate.net]

- 23. rogersgroup.northwestern.edu [rogersgroup.northwestern.edu]

- 24. cui.umn.edu [cui.umn.edu]

- 25. mdpi.com [mdpi.com]

- To cite this document: BenchChem. [Technical Support Center: Large-Scale Pentacene Device Fabrication]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b032325#challenges-in-large-scale-pentacene-device-fabrication]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com