# electronic properties of pentacene thin films

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |

|----------------------|-----------|-----------|

| Compound Name:       | Pentacene |           |

| Cat. No.:            | B032325   | Get Quote |

An in-depth technical guide to the electronic properties of **pentacene** thin films, designed for researchers, scientists, and drug development professionals.

#### Introduction

**Pentacene** (C<sub>22</sub>H<sub>14</sub>) is a polycyclic aromatic hydrocarbon consisting of five linearly fused benzene rings. It has emerged as a benchmark p-type organic semiconductor due to its relatively high charge carrier mobility and robust performance in organic thin-film transistors (OTFTs).[1][2] Its well-ordered molecular packing in thin films facilitates efficient charge transport, making it a material of great interest for applications in flexible displays, sensors, and RFID tags.[1][3] The electronic properties of **pentacene** thin films are not intrinsic to the molecule itself but are critically dependent on the film's structural and morphological characteristics, which are, in turn, dictated by fabrication conditions.[4][5] Understanding the interplay between processing, structure, and electronic performance is paramount for designing high-performance organic electronic devices.

## **Core Electronic Properties**

The performance of **pentacene**-based devices is quantified by several key electronic parameters, primarily derived from the characterization of thin-film transistors.

## Charge Carrier Mobility (µ)

Field-effect mobility is a measure of how quickly charge carriers (holes in the case of **pentacene**) move through the semiconductor under the influence of an electric field. It is the most common figure of merit for OTFTs. **Pentacene** thin films have demonstrated some of the

highest mobilities among organic semiconductors, often exceeding that of amorphous silicon. [2] However, reported values span several orders of magnitude, from less than 10<sup>-3</sup> cm<sup>2</sup>/Vs to as high as 8.85 cm<sup>2</sup>/Vs, reflecting the profound impact of film quality and device architecture.[6] [7][8] High mobility is generally associated with large, well-ordered crystalline grains and minimal defects.[4][9]

#### **On/Off Current Ratio**

The On/Off ratio is the ratio of the drain current when the transistor is in the "on" state (gate voltage applied) to the "off" state (zero or positive gate voltage). A high On/Off ratio is crucial for digital logic applications to ensure clear switching behavior and low standby power consumption. **Pentacene** OTFTs typically exhibit excellent On/Off ratios, often in the range of 10<sup>5</sup> to 10<sup>8</sup>.[4][6]

## **Threshold Voltage (Vth)**

The threshold voltage is the minimum gate voltage required to induce a conducting channel and turn the transistor "on". For p-type accumulation-mode devices like those made with **pentacene**, Vth is typically negative. Its value is sensitive to charge traps at the semiconductor-dielectric interface and within the bulk of the semiconductor.[6][10]

## **Contact Resistance (Rc)**

In OTFTs, the resistance at the interface between the metal source/drain electrodes and the organic semiconductor can significantly limit device performance, especially in short-channel devices.[11] This contact resistance is not a fixed value but is dependent on the gate voltage, electrode geometry (top vs. bottom contact), and the choice of metal.[12] For **pentacene**, gold (Au) is a common electrode material. Contact resistance values have been reported in the range of  $10^6$  to  $10^{10}$   $\Omega$ , with width-normalized values as low as 10  $\Omega$ cm achievable under optimized conditions.[13]

# **Factors Influencing Electronic Properties**

The electronic characteristics of **pentacene** thin films are intricately linked to a variety of controllable factors during fabrication.

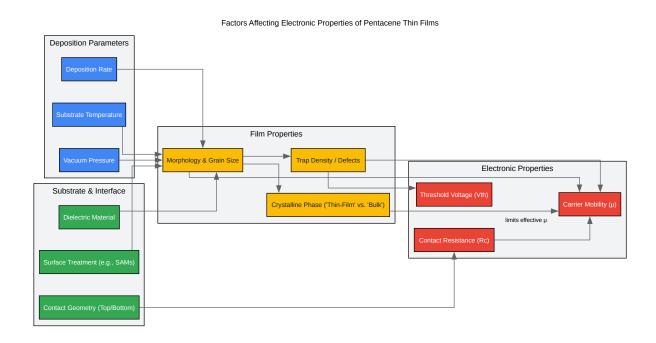

Click to download full resolution via product page

Factors influencing **pentacene** thin film electronic properties.

# **Deposition Method and Conditions**

Thermal evaporation in a high vacuum is the most common method for depositing high-quality **pentacene** films.[14][15] Key parameters include:

- Deposition Rate: Slower deposition rates (e.g., < 1 Å/s) generally promote larger grain sizes and better molecular ordering, leading to higher mobility.[6]

- Substrate Temperature: Deposition at elevated substrate temperatures (e.g., 60-80 °C) can enhance molecular diffusion on the surface, resulting in larger, more ordered crystalline domains and improved device performance.[9][12]

- Vacuum Pressure: A high vacuum (e.g., 10<sup>-6</sup> Torr or lower) is necessary to minimize impurities and contamination in the film.[16]

Solution-based methods, such as spin coating of a soluble **pentacene** precursor, offer a lower-cost, large-area alternative, with reported mobilities reaching up to 0.38 cm<sup>2</sup>/Vs.[17][18]

## Film Morphology and Structure

The morphology of the film at the microscopic level is a primary determinant of its electronic properties.

- Grain Size and Boundaries: Pentacene films are typically polycrystalline. Charge transport involves movement within crystalline grains (intra-grain) and hopping between them (intergrain).[19] Larger grains reduce the number of grain boundaries, which act as scattering centers and traps for charge carriers, thus leading to higher mobility.[9][19]

- Crystalline Phase: **Pentacene** can exist in different polymorphic structures. The "thin-film phase," with an interlayer spacing of approximately 15.4 Å, is often observed in films grown on inert substrates and is associated with higher charge carrier mobility compared to the "bulk phase" (spacing ~14.5 Å).[14][16]

#### **Dielectric Interface**

The interface between the **pentacene** film and the gate dielectric is where the conductive channel is formed in a TFT. Its quality is critical.

- Surface Energy and Roughness: A smooth dielectric surface with appropriate surface energy promotes the growth of well-ordered **pentacene** films.[5][20]

- Surface Treatment: Modifying the dielectric surface with self-assembled monolayers (SAMs), such as octadecyltrichlorosilane (OTS), is a common strategy to reduce surface traps,

improve molecular ordering, and significantly enhance mobility.[21] Mobilities as high as 1.25 cm²/Vs have been reported on OTS-treated SiO<sub>2</sub>.[21]

#### **Electronic Structure**

- HOMO-LUMO Gap: The energy gap between the Highest Occupied Molecular Orbital

(HOMO) and the Lowest Unoccupied Molecular Orbital (LUMO) is a fundamental electronic

property. For pentacene thin films, this transport gap is experimentally determined to be

approximately 2.2 eV.[16][22]

- Density of States (DOS): The DOS describes the number of available electronic states at each energy level. In disordered organic semiconductors, the DOS is not sharp but consists of band tails of localized states (traps) extending into the HOMO-LUMO gap.[23][24] A higher density of these trap states, often caused by structural disorder or impurities, degrades mobility and shifts the threshold voltage.[24][25] The DOS in pentacene films is often modeled with a Gaussian distribution and an exponential tail.[23]

## **Quantitative Data Summary**

The following tables summarize key quantitative electronic properties of **pentacene** thin films reported in the literature.

Table 1: Reported Field-Effect Mobility (µ) in **Pentacene** OTFTs

| Mobility<br>(cm²/Vs) | Substrate/Diel<br>ectric        | Deposition<br>Method               | Key<br>Conditions/Not<br>es                                    | Reference(s) |

|----------------------|---------------------------------|------------------------------------|----------------------------------------------------------------|--------------|

| 8.85                 | Barium<br>Titanate              | Thermal<br>Evaporation             | High-<br>permittivity<br>solution-<br>processed<br>dielectric. | [7]          |

| 1.25                 | OTS-treated<br>SiO <sub>2</sub> | Neutral Cluster<br>Beam Deposition | Room<br>temperature<br>deposition.                             | [21]         |

| 1.10                 | SiO <sub>2</sub>                | Thermal<br>Evaporation             | Top gate, bottom contact geometry.                             | [10]         |

| 0.7                  | SiO <sub>2</sub>                | Thermal<br>Evaporation             | Substrate held at elevated temperature.                        | [4]          |

| 0.4                  | Silicon Nitride                 | Thermal<br>Evaporation             | Inverted<br>staggered<br>transistor<br>structure.              | [5]          |

| 0.38                 | SiO2                            | Spin Coating<br>(precursor)        | Solution-<br>processed from a<br>pentacene<br>precursor.       | [17]         |

| 0.26                 | SiO2                            | Thermal<br>Evaporation             | Studied over a<br>temperature<br>range of 300-450<br>K.        | [6]          |

$\mid$  0.038  $\mid$  SiO $_2\mid$  Molecular Beam Deposition  $\mid$  Coexistence of thin-film and single-crystal phases.  $\mid$  [26]  $\mid$

Table 2: Other Key Electrical Parameters for **Pentacene** OTFTs

| Parameter                  | Typical Value<br>Range            | Conditions / Notes                                      | Reference(s) |

|----------------------------|-----------------------------------|---------------------------------------------------------|--------------|

| On/Off Ratio               | 10 <sup>5</sup> - 10 <sup>8</sup> | Highly dependent on gate leakage and off-current.       | [4][6][10]   |

| Threshold Voltage<br>(Vth) | -2 V to -10 V                     | Sensitive to interface traps and processing conditions. | [6][10]      |

| Contact Resistance (Rc)    | $10^6$ - $10^{10}$ Ω              | Gate bias dependent.                                    |              |

| Width-Normalized Rc | 10 - 2000  $\Omega$ ·cm | A more standardized metric for comparing contacts. | [12][13] |

Table 3: Fundamental Electronic Structure Parameters

| Parameter              | Value    | Measurement<br>Technique | Reference(s) |

|------------------------|----------|--------------------------|--------------|

| HOMO-LUMO Gap          | ~2.2 eV  | STS, UPS/IPES            | [16][22]     |

| Ionization Energy (IE) | ~4.90 eV | UPS                      | [22]         |

| Electron Affinity (EA) | ~2.70 eV | IPES                     | [22]         |

| DOS Width ( $\sigma$ ) | 0.07  $\pm$  0.01 eV | Field-effect studies on treated substrates. |[23] |

# **Experimental Protocols and Characterization**

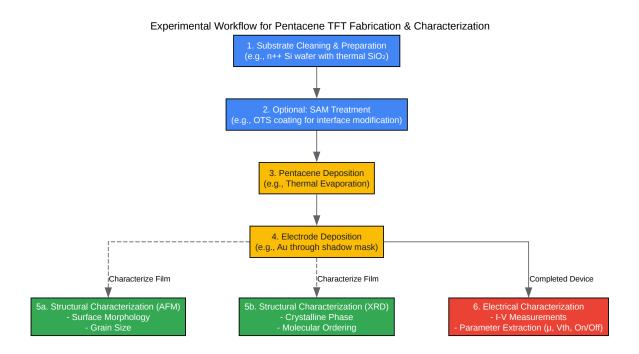

A standard workflow for investigating the electronic properties of **pentacene** thin films involves fabrication of a thin-film transistor followed by structural and electrical characterization.

Click to download full resolution via product page

Workflow for **Pentacene** TFT Fabrication and Characterization.

#### Thin Film Deposition: Thermal Evaporation

- Substrate Preparation: A heavily doped silicon wafer with a thermally grown silicon dioxide layer (e.g., 100-300 nm) is commonly used as the substrate and gate dielectric, respectively. The substrate is rigorously cleaned using a sequence of solvents (e.g., acetone, isopropanol) in an ultrasonic bath.[14]

- SAM Treatment (Optional): To improve the dielectric interface, the cleaned SiO<sub>2</sub> surface can be treated with a SAM, such as OTS or hexamethyldisilazane (HMDS).[9][21]

- Deposition: The substrate is loaded into a high-vacuum chamber (base pressure  $< 5x10^{-6}$  Torr). **Pentacene** powder (purified by sublimation) is placed in a resistively heated crucible.

[16] The substrate is often heated to a specific temperature (e.g., 65 °C).[9]

• Process Control: The crucible is heated to sublimate the **pentacene**, which deposits on the substrate. The deposition rate is monitored with a quartz crystal microbalance and typically controlled to be slow (e.g., 0.1 - 1 Å/s).[6][9] A final film thickness of 30-60 nm is common for TFT applications.[11]

## **Thin-Film Transistor (TFT) Fabrication**

- Device Structure: A common structure is the top-contact, bottom-gate configuration. The

doped Si acts as the gate, SiO<sub>2</sub> as the dielectric, and the deposited **pentacene** as the active

layer.[27]

- Electrode Deposition: Source and drain electrodes (typically 50 nm of Gold) are then thermally evaporated on top of the **pentacene** film through a shadow mask.[9] The shadow mask defines the channel length (L) and channel width (W) of the transistor.

#### Structural Characterization

- Atomic Force Microscopy (AFM): Performed in tapping mode to visualize the surface morphology of the **pentacene** film. This provides direct information on the grain size, shape, and surface roughness.[14][16]

- X-Ray Diffraction (XRD): Used in a Bragg-Brentano geometry to determine the crystalline structure and orientation of the molecules. The presence of sharp diffraction peaks corresponding to the (00l) planes confirms a high degree of molecular ordering with the long molecular axis oriented nearly perpendicular to the substrate.[5][14] The peak positions allow for identification of the crystalline phase (thin-film vs. bulk).[14]

#### **Electrical Characterization**

- Measurement Setup: The completed TFT is placed in a probe station, often in an inert atmosphere or vacuum to prevent degradation. A semiconductor parameter analyzer is used to apply voltages and measure currents.

- Output Characteristics: The drain current (ID) is measured as a function of the drain-source voltage (VDS) for several different gate voltages (VGS).

- Transfer Characteristics: ID is measured as a function of VGS at a fixed, high VDS (saturation regime). This curve is used to extract the key device parameters.

- Parameter Extraction:

- Mobility (μ): In the saturation regime, mobility is calculated from the slope of the √|ID| vs.

VGS plot using the standard MOSFET equation: ID = (W/2L) \* μ \* Ci \* (VGS Vth)² where

Ci is the capacitance per unit area of the gate dielectric.

- Threshold Voltage (Vth): Determined from the x-intercept of the linear fit to the √|ID| vs.

VGS plot.

- o On/Off Ratio: The ratio of the maximum ID to the minimum ID from the transfer curve.

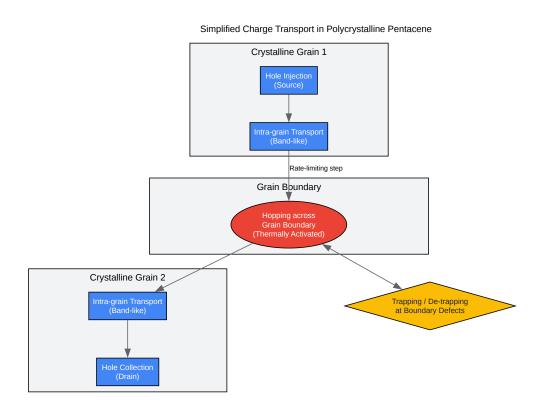

## **Charge Transport Mechanism**

Click to download full resolution via product page

Charge transport pathway in polycrystalline **pentacene** films.

Charge transport in polycrystalline **pentacene** films is generally described by a multiple trapping and release model or a hopping model.[5][19] Conduction is believed to be limited by the grain boundaries.

- Intra-grain Transport: Within the well-ordered crystalline grains, charge carriers are relatively delocalized and transport is efficient, sometimes described as "band-like."[27]

- Inter-grain Transport: To move from one grain to another, carriers must overcome an energy barrier at the grain boundary. This process, known as hopping, is thermally activated and is typically the rate-limiting step for overall conduction in the film.[5][19] The structural disorder and defects concentrated at these boundaries create localized trap states that can immobilize charge carriers, further impeding transport and reducing the effective mobility.[24] Therefore, maximizing grain size and improving the quality of the grain boundaries are key strategies for enhancing the electronic performance of pentacene thin films.

## Conclusion

The electronic properties of **pentacene** thin films are a complex function of molecular-level packing, microscopic morphology, and device architecture. High charge carrier mobilities and excellent switching characteristics can be achieved through careful control of deposition conditions, particularly substrate temperature and deposition rate, and by engineering the semiconductor-dielectric interface with surface treatments. The performance is ultimately governed by the degree of crystalline order and the density of trap states, which are primarily associated with grain boundaries. A thorough understanding of these structure-property relationships, facilitated by detailed structural and electrical characterization, is essential for the continued development and application of **pentacene**-based organic electronics.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. Structure of Pentacene Monolayers on Amorphous Silicon Oxide and Relation to Charge Transport | Stanford Synchrotron Radiation Lightsource [www-ssrl.slac.stanford.edu]

- 2. Pentacene Wikipedia [en.wikipedia.org]

- 3. researchgate.net [researchgate.net]

#### Foundational & Exploratory

- 4. Pentacene organic thin-film transistors-molecular ordering and mobility | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 5. pubs.aip.org [pubs.aip.org]

- 6. cui.umn.edu [cui.umn.edu]

- 7. files01.core.ac.uk [files01.core.ac.uk]

- 8. Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance PMC [pmc.ncbi.nlm.nih.gov]

- 9. pubs.aip.org [pubs.aip.org]

- 10. Characteristics of pentacene organic thin film transistor with top gate and bottom contact [cpsjournals.cn]

- 11. Contact resistance in pentacene thin film transistors | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 12. pubs.aip.org [pubs.aip.org]

- 13. Contact resistance of organic TFTs [fkf.mpg.de]

- 14. beei.org [beei.org]

- 15. mdpi.com [mdpi.com]

- 16. aquila.infn.it [aquila.infn.it]

- 17. Solution processed high performance pentacene thin-film transistors Chemical Communications (RSC Publishing) [pubs.rsc.org]

- 18. Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance UCL Discovery [discovery.ucl.ac.uk]

- 19. researchgate.net [researchgate.net]

- 20. Effect of pentacene—dielectric affinity on pentacene thin film growth morphology in organic field-effect transistors - Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- 21. individual.utoronto.ca [individual.utoronto.ca]

- 22. pubs.aip.org [pubs.aip.org]

- 23. researchgate.net [researchgate.net]

- 24. spiedigitallibrary.org [spiedigitallibrary.org]

- 25. researchgate.net [researchgate.net]

- 26. pubs.acs.org [pubs.acs.org]

- 27. scispace.com [scispace.com]

- To cite this document: BenchChem. [electronic properties of pentacene thin films].

BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b032325#electronic-properties-of-pentacene-thin-films]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com