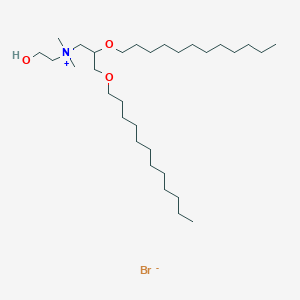

DLRIE

Description

Properties

Molecular Formula |

C31H66BrNO3 |

|---|---|

Molecular Weight |

580.8 g/mol |

IUPAC Name |

2,3-didodecoxypropyl-(2-hydroxyethyl)-dimethylazanium bromide |

InChI |

InChI=1S/C31H66NO3.BrH/c1-5-7-9-11-13-15-17-19-21-23-27-34-30-31(29-32(3,4)25-26-33)35-28-24-22-20-18-16-14-12-10-8-6-2;/h31,33H,5-30H2,1-4H3;1H/q+1;/p-1 |

InChI Key |

LBYIQAJLTHFLEB-UHFFFAOYSA-M |

Canonical SMILES |

CCCCCCCCCCCCOCC(C[N+](C)(C)CCO)OCCCCCCCCCCCC.[Br-] |

Origin of Product |

United States |

Foundational & Exploratory

An In-depth Technical Guide to the Principles of Anisotropic Etching in Silicon

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides a comprehensive overview of the core principles of anisotropic etching in silicon, a critical process in the fabrication of microelectromechanical systems (MEMS) and microfluidic devices. Understanding these principles is essential for the precise engineering of microstructures with applications ranging from drug delivery systems to diagnostic biosensors.

Fundamental Principles: Anisotropic vs. Isotropic Etching

Silicon wet etching is a process that utilizes chemical solutions to remove silicon material. This process can be broadly categorized into two types: isotropic and anisotropic etching.[1]

-

Isotropic Etching: This method removes silicon at an equal rate in all directions, resulting in rounded features and undercutting beneath a mask.[1][2] Isotropic etchants, such as mixtures of hydrofluoric acid (HF) and nitric acid (HNO3), are useful for applications requiring smooth surfaces or the rapid removal of large volumes of material.[1]

-

Anisotropic Etching: In contrast, anisotropic etching exhibits different etch rates depending on the crystallographic orientation of the silicon.[1][3] This orientation-dependent etching allows for the creation of well-defined structures with sharp corners and angled sidewalls, making it indispensable for the fabrication of precise MEMS devices.[1][4]

The fundamental difference in their mechanisms dictates their respective applications. While isotropic etching is faster, anisotropic etching provides superior control over the final geometry of the etched structures.[3]

The Role of Crystallographic Orientation

The anisotropic nature of the etching process is intrinsically linked to the crystal structure of silicon, which has a diamond cubic lattice.[5] The arrangement and density of atoms on different crystal planes lead to significant variations in etch rates.[3][5] The most common crystal planes referenced in silicon micromachining are the (100), (110), and (111) planes.[5]

-

(111) Planes: These are the most densely packed planes in the silicon crystal lattice.[5] Consequently, they exhibit the slowest etch rate and act as etch-stop planes in many anisotropic etchants.[6][7]

-

(100) and (110) Planes: These planes have a less dense atomic arrangement, making them more susceptible to chemical attack and therefore exhibiting faster etch rates.[5]

This differential etch rate is the cornerstone of anisotropic etching, enabling the formation of V-shaped grooves, trenches with vertical sidewalls, and other complex three-dimensional microstructures.[8][9] For instance, etching a square opening on a (100)-oriented silicon wafer with an anisotropic etchant will result in a pyramidal pit bounded by the slow-etching {111} planes, which form an angle of 54.74° with the (100) surface.[3][10]

Common Anisotropic Etchants and Their Properties

The most widely used anisotropic etchants are alkaline solutions, primarily Potassium Hydroxide (B78521) (KOH) and Tetramethylammonium Hydroxide (TMAH).[1]

Potassium Hydroxide (KOH)

KOH is a popular etchant due to its low cost, high etch rate, and excellent anisotropy.[3][11] It exhibits a very high etch rate selectivity between the {100} and {111} crystal planes, often reported to be as high as 400:1.[5][12]

The etching process in KOH is a chemical reaction where silicon is oxidized and then dissolved by hydroxide ions.[4][12] The overall reaction can be simplified as:

Si + 2OH⁻ + 2H₂O → SiO₂(OH)₂²⁻ + 2H₂[9]

Tetramethylammonium Hydroxide (TMAH)

TMAH is another widely used anisotropic etchant, particularly favored in applications where CMOS compatibility is crucial, as it does not introduce mobile ions like potassium.[13][14] TMAH offers good anisotropy and is less hazardous than other etchants like ethylenediamine (B42938) pyrocatechol (B87986) (EDP) and hydrazine.[3][13]

The etching mechanism in TMAH is similar to that of KOH, involving the reaction of hydroxide ions with silicon.[15] However, the etching characteristics, such as the exact etch rates and surface morphology, can differ significantly between the two etchants.[16]

Factors Influencing Anisotropic Etching

Several parameters must be carefully controlled to achieve reproducible and precise etching results.[1][3]

-

Etchant Concentration: The concentration of the alkaline solution significantly affects the etch rate and the anisotropy. For KOH, the etch rate of (100) silicon generally decreases with increasing concentration above a certain point.[17][18] Higher concentrations of KOH can also lead to smoother etched surfaces.[5][17] In TMAH, the etch rate of the (100) plane typically decreases as the concentration increases.[13]

-

Temperature: The etch rate is highly dependent on the temperature of the etchant solution.[5][11] Increasing the temperature generally increases the etch rate for all crystal planes.[11][18] However, the selectivity between different planes can also be affected by temperature changes.[13]

-

Doping Concentration: The etch rate can be significantly influenced by the concentration of dopants in the silicon. High concentrations of boron (p-type doping) can dramatically reduce the etch rate, a phenomenon known as an etch-stop.[10][17][19] This effect is utilized to create thin membranes and other microstructures.

-

Additives: Additives can be introduced to the etchant solution to modify its properties. For example, isopropyl alcohol (IPA) is often added to KOH to improve the surface smoothness of the etched silicon.[10][17] In TMAH, dissolving silicon into the solution can reduce the etch rate of aluminum, which is important for post-CMOS processing.[13][14]

Data Presentation: Etch Rates and Selectivity

The following tables summarize typical etch rates and selectivity for common anisotropic etchants. It is important to note that these values can vary depending on the specific experimental conditions.

Table 1: Etch Rates of Silicon in KOH Solutions

| Crystal Plane | KOH Concentration (wt%) | Temperature (°C) | Etch Rate (µm/min) |

| (100) | 30 | 80 | ~1.0[10] |

| (111) | 30 | 80 | ~0.025 (based on 40:1 ratio) |

| (110) | - | - | Etches faster than (100)[6] |

Note: The etch rate selectivity of (100) to (111) in KOH is often cited as being around 400:1, though it can vary.[5][12]

Table 2: Etch Rates of Silicon in TMAH Solutions

| Crystal Plane | TMAH Concentration (wt%) | Temperature (°C) | Etch Rate (µm/min) |

| (100) | 25 | 85 | ~0.5[20] |

| (100) | 20 | 80 | 0.3 - 1.28[21] |

| (111) | 20 | 80 | 0.013 - 0.061[21] |

| (110) | - | - | ~1.4 times faster than (100)[13] |

Table 3: Etch Selectivity of Common Masking Materials

| Etchant | Masking Material | Etch Rate | Selectivity to Si (100) |

| KOH | Silicon Dioxide (SiO₂) | Slow etching occurs[8][10] | ~465:1[22] |

| KOH | Silicon Nitride (Si₃N₄) | Very slow etching[8][10] | High |

| TMAH | Silicon Dioxide (SiO₂) | Very low etch rate[13] | High |

| TMAH | Silicon Nitride (Si₃N₄) | Almost no etching[13] | Very High |

Experimental Protocols

The following provides a generalized methodology for a typical anisotropic etching experiment using KOH.

Masking Layer Deposition and Patterning

-

Substrate Preparation: Start with a clean, single-crystal silicon wafer of the desired orientation (e.g., <100>).

-

Mask Deposition: Deposit a hard mask layer, such as silicon nitride (Si₃N₄) or silicon dioxide (SiO₂), on the wafer surface. Silicon nitride is often preferred for its lower etch rate in KOH.[10]

-

Photolithography:

-

Apply a layer of photoresist over the mask.

-

Expose the photoresist to UV light through a photomask with the desired pattern.

-

Develop the photoresist to reveal the pattern.

-

-

Mask Etching: Use a suitable etching method (e.g., reactive ion etching - RIE) to transfer the pattern from the photoresist to the hard mask layer, exposing the underlying silicon in the desired areas.[10]

-

Photoresist Removal: Remove the remaining photoresist using a solvent like acetone.[10]

Anisotropic Etching Process

-

Etchant Preparation: Prepare the KOH solution of the desired concentration (e.g., 30% by weight) by dissolving KOH pellets in deionized water.[10] Isopropyl alcohol (IPA) can be added to improve surface finish.[10]

-

Heating: Heat the KOH solution to the desired temperature (e.g., 80°C) in a temperature-controlled bath.[8][10]

-

Wafer Immersion: Immerse the patterned silicon wafer into the heated KOH solution.[10] Hydrogen bubbles will be generated at the exposed silicon surfaces during etching.[10][18]

-

Etching: Allow the etching to proceed for the calculated time required to achieve the desired etch depth. The etch rate is typically around 1 µm/minute under these conditions.[10]

-

Rinsing and Drying: After the desired etch time, remove the wafer from the KOH solution and rinse it thoroughly with deionized water, followed by drying with nitrogen.[10]

Characterization

-

Etch Depth Measurement: Measure the etch depth using a profilometer or a scanning electron microscope (SEM).

-

Surface Morphology Analysis: Inspect the quality of the etched surfaces and the geometry of the microstructures using optical microscopy and SEM.[9][18]

Visualizations of Key Concepts

Anisotropic Etching of (100) Silicon

Caption: Anisotropic etching of a (100) silicon wafer.

Experimental Workflow for Anisotropic Etching

Caption: A typical workflow for silicon anisotropic etching.

Advanced Topics: Corner Undercutting and Surface Roughness

Corner Undercutting

A significant challenge in anisotropic etching is the undercutting of convex corners.[23][24] While concave corners formed by the intersection of {111} planes are stable, convex corners are attacked by the etchant, leading to the exposure of faster-etching planes and a deviation from the desired geometry.[23][24] Various compensation techniques, involving the addition of specific geometric patterns to the mask at the corners, have been developed to mitigate this effect.[24][25]

Surface Roughness

The surface roughness of the etched silicon is a critical parameter for many applications.[26][27] Roughness can be influenced by factors such as etchant concentration, temperature, and the presence of impurities.[26][28] For instance, in KOH etching, higher concentrations and the addition of IPA can lead to smoother surfaces.[17][27] The formation of microscopic pyramids or hillocks on the etched surface can also occur, which is often attributed to factors like the evolution of hydrogen bubbles or material defects.[13][18][28]

References

- 1. modutek.com [modutek.com]

- 2. modutek.wordpress.com [modutek.wordpress.com]

- 3. classweb.ece.umd.edu [classweb.ece.umd.edu]

- 4. researchgate.net [researchgate.net]

- 5. sibranchwafer.com [sibranchwafer.com]

- 6. sensors.myu-group.co.jp [sensors.myu-group.co.jp]

- 7. pubs.acs.org [pubs.acs.org]

- 8. microtechprocess.com [microtechprocess.com]

- 9. digitalcommons.usu.edu [digitalcommons.usu.edu]

- 10. inrf.uci.edu [inrf.uci.edu]

- 11. modutek.com [modutek.com]

- 12. scispace.com [scispace.com]

- 13. sensors.myu-group.co.jp [sensors.myu-group.co.jp]

- 14. engineering.purdue.edu [engineering.purdue.edu]

- 15. microchemicals.com [microchemicals.com]

- 16. ieeexplore.ieee.org [ieeexplore.ieee.org]

- 17. contents.kocw.or.kr [contents.kocw.or.kr]

- 18. tsijournals.com [tsijournals.com]

- 19. Anisotropic and selective etching - Helmholtz-Zentrum Dresden-Rossendorf, HZDR [hzdr.de]

- 20. filelist.tudelft.nl [filelist.tudelft.nl]

- 21. sensors.myu-group.co.jp [sensors.myu-group.co.jp]

- 22. Anisotropic and selective etching - Helmholtz-Zentrum Dresden-Rossendorf, HZDR [hzdr.de]

- 23. A New Model for the Etching Characteristics of Corners Formed by Si{111} Planes on Si{110} Wafer Surface [scirp.org]

- 24. scispace.com [scispace.com]

- 25. Compensating corner undercutting in anisotropic etching of (100) silicon for chip separation | Semantic Scholar [semanticscholar.org]

- 26. Characterization of anisotropic etching properties of single-crustal silicon: surface roughening as a function of crystallographic orientation | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 27. researchgate.net [researchgate.net]

- 28. sensors.myu-group.co.jp [sensors.myu-group.co.jp]

Cryogenic Deep Reactive-Ion Etching: A Technical Guide for Researchers and Professionals

Cryogenic Deep Reactive-Ion Etching (DRIE) is a highly anisotropic plasma etching technique used to fabricate high-aspect-ratio micro and nanostructures. This method is particularly crucial in the fields of microelectromechanical systems (MEMS), photonics, biomedical devices, and drug delivery systems. By operating at extremely low temperatures, typically around -110°C, cryogenic DRIE offers distinct advantages over other etching techniques, most notably the Bosch process, by producing exceptionally smooth and vertical sidewalls without the characteristic "scalloping" effect.

This in-depth technical guide provides a comprehensive overview of the core principles, experimental protocols, and key parameters of cryogenic DRIE, tailored for researchers, scientists, and professionals in drug development who seek to leverage this powerful fabrication technology.

Fundamental Principles

Cryogenic DRIE is a continuous, non-switching etching process that takes place in an inductively coupled plasma (ICP) reactor. The fundamental principle lies in the precise balance between etching and passivation at cryogenic temperatures. The process typically utilizes a gas mixture of sulfur hexafluoride (SF6) and oxygen (O2).

The key mechanisms at play are:

-

Etching: In the plasma, SF6 decomposes to produce fluorine radicals (F*). These highly reactive radicals chemically etch the silicon substrate, forming volatile silicon tetrafluoride (SiF4) as a byproduct.[1]

-

Passivation: Simultaneously, oxygen radicals (O*) react with the silicon and fluorine radicals on the surfaces to form a thin passivation layer of silicon oxyfluoride (SiOxFy).[1][2] At cryogenic temperatures, the deposition of this passivation layer is enhanced.[1]

-

Anisotropy: The directionality of the etch is achieved through ion bombardment. Ions from the plasma, such as SF5+, are accelerated towards the substrate.[1] This ion bombardment is energetic enough to remove the SiOxFy passivation layer at the bottom of the trench, exposing the silicon to the fluorine radicals for further etching.[1] The sidewalls, however, are shielded from this direct ion bombardment and remain protected by the passivation layer, thus preventing lateral etching and ensuring a highly vertical etch profile.[1][2]

This continuous interplay between etching and passivation at low temperatures is what enables the fabrication of deep, smooth, and vertically etched structures.

Process Workflow and Mechanisms

The logical flow of the cryogenic DRIE process involves several critical steps, from wafer preparation to the final etched structure. The underlying physicochemical mechanisms occur simultaneously within the plasma reactor.

The core of the process relies on a delicate balance of chemical reactions and physical bombardment within the plasma.

Key Process Parameters

The success of cryogenic DRIE is highly dependent on the precise control of several process parameters. These parameters influence the etch rate, selectivity, and the final profile of the etched features.

| Parameter | Typical Range | Primary Effects |

| Substrate Temperature | -80°C to -120°C | Affects the formation and stability of the SiOxFy passivation layer. Lower temperatures generally lead to more passivation.[3] |

| SF6 Flow Rate | 20 - 100 sccm | Primary source of fluorine radicals for etching. Higher flow rates can increase the etch rate. |

| O2 Flow Rate | 5 - 25 sccm | Controls the formation of the SiOxFy passivation layer. The O2/SF6 ratio is critical for profile control.[4] |

| ICP Power | 800 - 2500 W | Controls the plasma density and the generation of reactive species. Higher power generally increases the etch rate. |

| RF Bias Power | 3 - 40 W | Controls the energy of ion bombardment, which is crucial for removing the passivation layer at the trench bottom. |

| Chamber Pressure | 5 - 20 mTorr | Influences the mean free path of ions and radicals, affecting the directionality of the etch. |

Experimental Protocols

While specific process parameters will vary depending on the equipment, desired feature geometry, and mask material, a general experimental protocol for cryogenic DRIE of silicon can be outlined. The following provides a foundational methodology.

Objective: To achieve a vertical etch profile in a silicon substrate using a patterned mask.

Materials and Equipment:

-

Silicon wafer with a patterned etch mask (e.g., photoresist, silicon dioxide, or a metal mask).

-

Inductively Coupled Plasma Reactive Ion Etching (ICP-RIE) system with cryogenic capabilities (e.g., Oxford Instruments PlasmaPro 100).[3][5]

-

Process gases: SF6, O2.

-

Scanning Electron Microscope (SEM) for profile analysis.

Methodology:

-

Sample Preparation:

-

System Preparation and Wafer Loading:

-

Load the wafer into the ICP-RIE chamber.

-

Initiate the cooling of the substrate stage to the target temperature, typically between -100°C and -120°C.[3]

-

-

Etching Process:

-

Once the target temperature is stable, introduce the process gases (SF6 and O2) into the chamber at the desired flow rates. A common starting point is an SF6 flow of 60-80 sccm and an O2 flow of 8-15 sccm.[5][7]

-

Set the chamber pressure to the desired level, for instance, 7.5 mTorr.[7]

-

Ignite the plasma by applying ICP power (e.g., 1200-1250 W).[5][7]

-

Apply a low RF bias power to the substrate stage (e.g., 3-10 W) to initiate anisotropic etching.[5][7]

-

The etching time will depend on the desired etch depth and the calibrated etch rate of the specific recipe.

-

-

Process Termination and Wafer Unloading:

-

After the designated etch time, turn off the plasma and gas flows.

-

Warm the substrate stage back to room temperature.

-

Vent the chamber and unload the wafer.

-

-

Post-Etch Analysis:

-

The remaining mask material can be removed using an appropriate stripping process.

-

Cleave the wafer and analyze the etch profile, depth, and sidewall smoothness using an SEM.

-

Parameter Tuning for Profile Control:

-

Vertical Sidewalls: Achieving a 90° sidewall requires a precise balance of the O2/SF6 ratio at a given temperature.

-

Positive Taper (sloped outwards): This can be induced by increasing the O2 flow, leading to "over-passivation".[4]

-

Negative Taper (undercut): A reduction in O2 flow can lead to insufficient passivation and a more isotropic etch profile.[4]

| Parameter Variation | Effect on Etch Profile | Reference |

| Increasing Temperature (-120°C to -80°C) | Shifts profile from negative to positive taper. | [3] |

| Increasing O2 Flow Rate | Shifts profile from negative to positive taper. | [3] |

| Increasing RF Bias Power | Can help to make the profile more vertical by enhancing the removal of the bottom passivation layer. | [5] |

Comparison with the Bosch Process

The primary alternative to cryogenic DRIE for deep silicon etching is the Bosch process. The choice between the two depends on the specific application requirements.

| Feature | Cryogenic DRIE | Bosch Process |

| Process Type | Continuous, single-step etching and passivation. | Cyclical, alternating between etching (SF6) and passivation (C4F8) steps.[6] |

| Sidewall Quality | Very smooth, no scalloping.[8] | Exhibits characteristic "scalloping" or ripples on the sidewalls due to the cyclical nature.[8] |

| Etch Rate | Generally lower than the Bosch process. | Higher etch rates are typically achievable.[9] |

| Operating Temperature | Cryogenic (~ -110°C).[10] | Near room temperature. |

| Passivation Layer | SiOxFy, which evaporates at room temperature.[11] | Fluorocarbon polymer (PTFE-like), which often requires a separate removal step.[2] |

| Complexity | Requires a liquid nitrogen cooling system.[8] | Requires fast-switching gas injection and heated chamber walls to prevent polymer buildup.[8] |

| Applications | Ideal for applications requiring extremely smooth sidewalls, such as photonics and nano-etching.[2] | Widely used for MEMS and other applications where high etch rates are prioritized and some sidewall roughness is tolerable.[2] |

Applications in Research and Drug Development

The unique capabilities of cryogenic DRIE make it a valuable tool for a range of advanced applications:

-

Microfluidics: Fabrication of micro-molds and channels with smooth surfaces for lab-on-a-chip devices and drug delivery systems.[2]

-

Microneedles: Creation of high-aspect-ratio microneedles for transdermal drug delivery, requiring smooth surfaces to minimize tissue damage.[5]

-

Biosensors: Manufacturing of silicon-based sensors with high surface area and precise geometries for detecting biological molecules.

-

Photonics: Etching of silicon waveguides and other optical components where smooth sidewalls are critical to minimize light scattering and loss.[2]

-

MEMS: Production of high-precision MEMS devices where dimensional control and smooth surfaces are paramount.[2]

Troubleshooting Common Issues

| Issue | Potential Cause(s) | Suggested Solution(s) |

| "Black Silicon" or Grass Formation | Over-passivation due to excessive O2 flow or temperature being too low. | Decrease the O2/SF6 ratio or slightly increase the substrate temperature. |

| Negative Sidewall Taper (Undercut) | Insufficient passivation. | Increase the O2/SF6 ratio or decrease the substrate temperature. |

| Positive Sidewall Taper | Excessive passivation. | Decrease the O2/SF6 ratio or increase the substrate temperature. |

| Mask Cracking | Thermal stress on the mask material at cryogenic temperatures. | Use a more robust mask material like silicon dioxide, aluminum oxide, or a metal mask.[4][6] |

| Low Etch Rate | Low ICP power, low SF6 flow, or excessive passivation. | Increase ICP power and/or SF6 flow. Optimize the O2/SF6 ratio to avoid over-passivation. |

References

- 1. pubs.aip.org [pubs.aip.org]

- 2. Deep Reactive Ion Etching (DRIE) - Oxford Instruments [plasma.oxinst.com]

- 3. researchgate.net [researchgate.net]

- 4. Cryogenic deep reactive ion etching of silicon micro and nanostructures [aaltodoc.aalto.fi]

- 5. Cryogenic Etching of Silicon: An Alternative Method For Fabrication of Vertical Microcantilever Master Molds - PMC [pmc.ncbi.nlm.nih.gov]

- 6. mtl.mit.edu [mtl.mit.edu]

- 7. 2.4. Cryogenic Deep Reactive Ion Etching [bio-protocol.org]

- 8. researchgate.net [researchgate.net]

- 9. Recent Advances in Reactive Ion Etching and Applications of High-Aspect-Ratio Microfabrication - PMC [pmc.ncbi.nlm.nih.gov]

- 10. Deep reactive-ion etching - Wikipedia [en.wikipedia.org]

- 11. ispc-conference.org [ispc-conference.org]

An In-depth Technical Guide to Deep Reactive Ion Etching (DRIE) for MEMS Fabrication

For Researchers, Scientists, and Drug Development Professionals

This guide provides a comprehensive overview of the Deep Reactive Ion Etching (DRIE) process, a cornerstone technology in the fabrication of Micro-Electro-Mechanical Systems (MEMS). It is intended for beginners in the field, offering a detailed exploration of the fundamental principles, key process technologies, experimental protocols, and troubleshooting strategies.

Introduction to Deep Reactive Ion Etching (DRIE)

Deep Reactive Ion Etching (DRIE) is a highly anisotropic plasma etching process used to create deep, steep-sided features in a substrate, typically silicon.[1] Unlike conventional Reactive Ion Etching (RIE), which is generally limited to shallower etches, DRIE can produce structures with depths of hundreds of microns and high aspect ratios (the ratio of height to width).[1] This capability is critical for the fabrication of a wide array of MEMS devices, including sensors, actuators, and microfluidic systems.

The core principle of DRIE involves the use of a high-density plasma to generate reactive ions and neutral species. These particles interact with the substrate material, leading to both chemical and physical removal of the material. The key to DRIE's anisotropy lies in the simultaneous or alternating application of a sidewall passivation mechanism that protects the vertical walls of the feature from being etched, while the bottom of the feature continues to be etched downwards.

There are two primary DRIE technologies: the Bosch process and the Cryogenic process. The Bosch process, the most widely used technique, employs a time-multiplexed approach that alternates between etching and passivation steps.[2] The Cryogenic process, on the other hand, achieves anisotropy by cooling the substrate to very low temperatures, which inhibits the chemical etching on the sidewalls.[1]

Core Principles of DRIE

The DRIE process takes place within a vacuum chamber where a plasma is generated from a source gas, typically containing fluorine compounds for silicon etching. An Inductively Coupled Plasma (ICP) source is commonly used to generate a high-density plasma. A separate radio-frequency (RF) bias is applied to the substrate holder to control the energy of the ions bombarding the substrate.[3]

The overall process can be broken down into three key phenomena:

-

Plasma Generation: An RF power source ionizes a gas (e.g., SF6) to create a plasma containing a mixture of ions, electrons, and reactive neutral species (radicals).

-

Ion Bombardment: An electric field accelerates the ions towards the substrate. This physical bombardment helps to remove material and break chemical bonds on the surface.

-

Chemical Reaction: Reactive neutral species diffuse to the substrate surface and react with it to form volatile byproducts that are then pumped out of the chamber.

Anisotropy, the ability to etch vertically with minimal lateral etching, is achieved by protecting the sidewalls of the etched feature. This is the defining characteristic of DRIE and is accomplished through different mechanisms in the Bosch and Cryogenic processes.

Key DRIE Technologies

The Bosch Process

The Bosch process, named after the German company Robert Bosch GmbH where it was developed, is a pulsed or time-multiplexed etching technique.[4] It cycles between two distinct phases: a deposition (passivation) step and an etching step.

-

Passivation Step: A fluorocarbon gas, typically Octafluorocyclobutane (C4F8), is introduced into the chamber. The plasma breaks down the C4F8 molecules, which then polymerize on all surfaces of the substrate, forming a thin, protective film.[5]

-

Etching Step: An etching gas, usually Sulfur Hexafluoride (SF6), is then introduced. The plasma generates fluorine radicals that isotropically etch the silicon. Simultaneously, the RF bias applied to the substrate creates a directional ion bombardment that preferentially removes the protective polymer layer at the bottom of the trench, exposing the silicon to the fluorine radicals. The polymer on the sidewalls remains largely intact, preventing lateral etching.[2][6]

This cycle of passivation and etching is repeated hundreds or even thousands of times, allowing for the creation of very deep, vertical trenches. A characteristic feature of the Bosch process is the presence of "scallops" on the sidewalls, which are ripples formed by the alternating etching and passivation steps. The size of these scallops can be controlled by adjusting the process parameters.[7]

The Cryogenic Process

The Cryogenic DRIE process offers an alternative to the Bosch process for achieving high anisotropy, particularly for features requiring very smooth sidewalls. In this method, the substrate is cooled to cryogenic temperatures, typically below -100°C.[1]

The low temperature significantly reduces the rate of the spontaneous chemical reaction between the fluorine radicals and the silicon on the sidewalls. At the same time, a mixture of SF6 and Oxygen (O2) is used as the etchant gas. The oxygen reacts with the silicon and fluorine radicals to form a thin layer of silicon oxyfluoride (SiOxFy) on the sidewalls. This layer acts as a passivation agent, protecting the sidewalls from the etchant.[2]

The ion bombardment at the bottom of the trench is still effective at removing this passivation layer, allowing the etch to proceed downwards. The result is a highly anisotropic etch with very smooth sidewalls, as the continuous passivation and etching process avoids the scalloping effect seen in the Bosch process. However, cryogenic DRIE can be more challenging to control and is sensitive to the type of mask material used, as some photoresists can crack at very low temperatures.[8]

Data Presentation: Key Process Parameters and Their Effects

The outcome of a DRIE process is highly dependent on a number of key parameters. The following tables summarize the typical ranges and effects of these parameters for both the Bosch and Cryogenic processes.

Table 1: Key Process Parameters for the Bosch DRIE Process

| Parameter | Typical Range | Effect on Etch Profile |

| Etch Gas (SF6) Flow Rate | 50 - 300 sccm | Higher flow rates generally increase the etch rate but can lead to more isotropic profiles if not balanced with passivation.[9] |

| Passivation Gas (C4F8) Flow Rate | 50 - 200 sccm | Higher flow rates increase the thickness of the passivation layer, leading to more vertical sidewalls but can also cause "grass" formation.[9] |

| ICP Power | 600 - 2500 W | Higher ICP power increases the plasma density, leading to higher etch rates. It can also affect the uniformity of the etch. |

| Platen (Bias) Power | 5 - 100 W | Higher platen power increases the ion energy, which enhances the removal of the passivation layer at the bottom of the trench, leading to a higher etch rate and more vertical profiles. However, excessive power can damage the mask and cause sputtering. |

| Chamber Pressure | 5 - 50 mTorr | Pressure affects the mean free path of the ions and radicals. Lower pressure leads to more directional ion bombardment and more anisotropic profiles. |

| Etch/Passivation Cycle Time | 1 - 10 seconds | The ratio of etch to passivation time is critical for controlling the sidewall profile. A longer passivation time leads to a thicker protective layer and more vertical walls, while a longer etch time increases the etch rate but can cause undercutting.[5] |

Table 2: Key Process Parameters for the Cryogenic DRIE Process

| Parameter | Typical Range | Effect on Etch Profile |

| Substrate Temperature | -80°C to -120°C | Lower temperatures enhance the formation of the SiOxFy passivation layer, leading to more anisotropic etching and smoother sidewalls.[10] |

| SF6 Flow Rate | 50 - 200 sccm | The primary etchant gas; higher flow rates increase the etch rate. |

| O2 Flow Rate | 5 - 20 sccm | The passivation gas; the ratio of O2 to SF6 is crucial for controlling the sidewall angle. Higher O2 concentration leads to a thicker passivation layer and can result in a positive taper.[10] |

| ICP Power | 600 - 2000 W | Increases plasma density and etch rate. |

| Platen (Bias) Power | 2 - 20 W | Controls ion energy. Lower power is generally used to minimize mask erosion and maintain smooth sidewalls. |

| Chamber Pressure | 5 - 20 mTorr | Affects ion directionality and uniformity. |

Table 3: Typical Performance Metrics for DRIE Processes

| Metric | Bosch Process | Cryogenic Process |

| Etch Rate | 5 - 20 µm/min | 2 - 8 µm/min |

| Selectivity to Photoresist | 50:1 to 200:1 | 40:1 to 100:1[10] |

| Selectivity to Silicon Dioxide | 150:1 to 500:1 | 100:1 to 300:1 |

| Aspect Ratio | Up to 100:1 | Up to 50:1 |

| Sidewall Angle | 88° - 92° | ~90° (highly vertical) |

| Sidewall Roughness (Scalloping) | 10 - 200 nm | < 10 nm |

Experimental Protocols

Bosch Process Experimental Protocol

This protocol outlines a typical Bosch DRIE process for creating high-aspect-ratio trenches in a silicon wafer using a photoresist mask.

1. Wafer Preparation:

- Start with a clean, dry silicon wafer.

- Apply a photoresist layer of appropriate thickness for the desired etch depth.

- Pattern the photoresist using standard photolithography techniques to define the areas to be etched.

- Hard-bake the photoresist to improve its resistance to the plasma.

2. Chamber Preparation and Wafer Loading:

- Perform a chamber clean recipe to remove any residues from previous runs.

- Vent the load-lock and load the patterned wafer onto the carrier.

- Pump down the load-lock to the base pressure.

- Transfer the wafer into the process chamber.

3. Process Execution:

- Set the substrate temperature, typically between 10°C and 40°C.

- Initiate the Bosch process recipe with the desired parameters (e.g., from Table 1). The process will alternate between the passivation and etch steps for a predetermined number of cycles or time.

- Passivation Step Example:

- C4F8 flow: 100 sccm

- ICP Power: 1500 W

- Platen Power: 10 W

- Pressure: 20 mTorr

- Time: 5 seconds

- Etch Step Example:

- SF6 flow: 200 sccm

- ICP Power: 2000 W

- Platen Power: 50 W

- Pressure: 30 mTorr

- Time: 7 seconds

4. Wafer Unloading and Post-Processing:

- After the process is complete, vent the process chamber and transfer the wafer back to the load-lock.

- Vent the load-lock and unload the wafer.

- Inspect the etched features using a scanning electron microscope (SEM) to verify the depth, sidewall profile, and aspect ratio.

- Remove the remaining photoresist using a suitable solvent or plasma ashing.

Cryogenic Process Experimental Protocol

This protocol describes a typical Cryogenic DRIE process for fabricating deep, smooth-sidewalled structures in silicon.

1. Wafer and Mask Preparation:

- Start with a clean, dry silicon wafer.

- Due to the low temperatures, a hard mask such as silicon dioxide or a specialized cryogenic photoresist is often preferred to avoid cracking.[8]

- Pattern the mask using appropriate lithography and etching techniques.

2. Chamber Preparation and Wafer Loading:

- Perform a chamber clean.

- Cool down the substrate holder to the desired cryogenic temperature (e.g., -110°C).

- Load the wafer into the pre-cooled chamber.

3. Process Execution:

- Initiate the Cryogenic DRIE recipe with the desired parameters (e.g., from Table 2). The process will run continuously until the desired etch depth is reached.

- Cryogenic Etch Step Example:

- Substrate Temperature: -110°C

- SF6 flow: 100 sccm

- O2 flow: 10 sccm

- ICP Power: 1800 W

- Platen Power: 15 W

- Pressure: 10 mTorr

4. Wafer Unloading and Post-Processing:

- After the etch is complete, slowly warm up the chamber and wafer to room temperature to prevent thermal shock.

- Vent the chamber and unload the wafer.

- Characterize the etched features using SEM.

- Remove the hard mask using an appropriate wet or dry etching process.

Mandatory Visualizations

Troubleshooting Common DRIE Issues

Table 4: Troubleshooting Guide for Common DRIE Problems

| Problem | Possible Causes | Potential Solutions |

| Sidewall Scalloping (Bosch Process) | - Etch/passivation cycle times are too long.[11] - Imbalance between etch and passivation steps. | - Decrease the cycle times for both etching and passivation.[11] - Adjust the ratio of etch to passivation time to achieve a better balance. |

| Notching at the bottom of features (especially on SOI wafers) | - Charging of the buried oxide layer deflects ions towards the sidewalls.[12] - Over-etching into the stop layer. | - Use a pulsed RF bias to neutralize charge buildup. - Optimize the over-etch time. - Introduce a conductive layer beneath the device layer.[7] |

| Aspect Ratio Dependent Etching (ARDE) or RIE Lag | - Depletion of reactive species at the bottom of high-aspect-ratio features.[6] - Reduced ion flux reaching the bottom of deep trenches. | - Increase the source power to generate more reactive species. - Decrease the chamber pressure to increase the mean free path of ions.[6] - Adjust the etch and passivation times to compensate for the lag.[13] |

| "Grass" or Micromasking | - Incomplete removal of the passivation layer at the bottom of the trench. - Sputtering of the mask material, which then redeposits on the surface. - Contamination in the chamber. | - Increase the bias power or the etch time to ensure complete removal of the passivation layer. - Use a more robust mask material with higher selectivity. - Perform a thorough chamber clean. |

| Tapered or Bowed Sidewalls | - Imbalance between ion bombardment and chemical etching. - Insufficient passivation. | - Adjust the bias power and pressure to control the directionality of the ions. - Increase the passivation gas flow or the passivation step time in the Bosch process. - In the cryogenic process, adjust the O2/SF6 ratio and temperature.[10] |

| Mask Cracking (Cryogenic Process) | - Thermal stress due to the large temperature difference between the wafer and the mask material.[8] | - Use a hard mask (e.g., SiO2, Si3N4) instead of a photoresist. - Use a specialized photoresist designed for cryogenic applications. - Ramp the temperature down and up slowly to minimize thermal shock. |

Conclusion

Deep Reactive Ion Etching is a powerful and versatile technology that has been instrumental in the advancement of MEMS and other micro- and nano-scale devices. The choice between the Bosch and Cryogenic processes depends on the specific requirements of the application, such as the desired sidewall smoothness, aspect ratio, and etch rate. A thorough understanding of the key process parameters and their interplay is essential for achieving the desired etch results. This guide provides a foundational understanding for researchers and professionals new to the field, enabling them to effectively utilize DRIE in their fabrication processes.

References

- 1. researchgate.net [researchgate.net]

- 2. samcointl.com [samcointl.com]

- 3. researchgate.net [researchgate.net]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. engineering.purdue.edu [engineering.purdue.edu]

- 7. researchgate.net [researchgate.net]

- 8. pubs.aip.org [pubs.aip.org]

- 9. engineering.purdue.edu [engineering.purdue.edu]

- 10. researchgate.net [researchgate.net]

- 11. mdpi.com [mdpi.com]

- 12. researchgate.net [researchgate.net]

- 13. pubs.aip.org [pubs.aip.org]

The Heart of Miniaturization: A Technical Guide to the Fundamental Mechanisms of Deep Silicon Etching

For Researchers, Scientists, and Drug Development Professionals

This in-depth technical guide delves into the core principles of deep silicon etching (DSE), a cornerstone technology in the fabrication of microelectromechanical systems (MEMS), microfluidics, and advanced drug delivery devices. Understanding the fundamental mechanisms of DSE is paramount for researchers and scientists seeking to design and fabricate novel micro- and nano-scale structures with high precision and repeatability. This document provides a comprehensive overview of the two primary DSE techniques—the Bosch process and cryogenic etching—supported by quantitative data, detailed experimental protocols, and visual representations of the underlying processes.

Introduction to Deep Silicon Etching

Deep silicon etching, often referred to as Deep Reactive Ion Etching (DRIE), is a highly anisotropic plasma-based etching process used to create deep, steep-sided features in silicon wafers.[1] Unlike conventional etching techniques that are often isotropic (etching in all directions), DRIE enables the fabrication of high-aspect-ratio structures, which are critical for a wide range of applications, from sensors and actuators in MEMS to micro-needles and lab-on-a-chip devices in the biomedical field.[2]

The key to achieving high anisotropy in DSE lies in the careful balance between etching and sidewall passivation. Two dominant industrial processes have emerged to achieve this: the time-multiplexed Bosch process and the continuous cryogenic etching process.

The Bosch Process: A Cyclical Approach to Anisotropy

The Bosch process, named after the German company Robert Bosch GmbH where it was patented, is a time-multiplexed etching technique that alternates between two distinct steps: an etching step and a passivation (deposition) step.[2][3] This cyclical nature allows for the creation of nearly vertical sidewalls, although it characteristically produces scalloped or corrugated sidewall textures with an amplitude of 100-500 nm.[3]

The Bosch Process Cycle

The process consists of two main phases that are repeated hundreds to thousands of times to achieve the desired etch depth.[3]

-

Passivation Step: A chemically inert passivation layer, typically a fluorocarbon polymer similar to Teflon, is deposited over the entire surface of the silicon wafer.[2] This is achieved using a plasma containing a gas like octafluorocyclobutane (B90634) (C₄F₈).[4]

-

Etching Step: A fluorine-based plasma, usually generated from sulfur hexafluoride (SF₆), is used to etch the silicon.[2] The key to the anisotropy of the Bosch process is that the directional ion bombardment in this step preferentially removes the passivation layer at the bottom of the trench, exposing the silicon to the reactive fluorine radicals.[3] The passivation on the sidewalls remains largely intact, protecting them from lateral etching.[4]

This two-step cycle allows for deep, vertical etching with high etch rates and excellent selectivity to masking materials.[5]

Chemical Reactions in the Bosch Process

The primary chemical reactions involved in the Bosch process are:

-

Etching: The fluorine radicals (F•) from the SF₆ plasma react with silicon (Si) to form volatile silicon tetrafluoride (SiF₄).[6]

-

Si + 4F• → SiF₄ (gas)

-

-

Passivation: The C₄F₈ plasma generates CF₂ radicals that polymerize on the silicon surface, forming a protective (CF₂)n film.

Cryogenic Etching: A Continuous Path to Smooth Sidewalls

Cryogenic deep silicon etching offers an alternative to the Bosch process, particularly when smooth sidewalls are a critical requirement.[6] This technique operates at cryogenic temperatures, typically between -100°C and -140°C.[3][7]

The Cryogenic Etching Mechanism

In cryogenic etching, the silicon substrate is cooled to a very low temperature. A mixture of SF₆ and oxygen (O₂) is introduced into the plasma chamber.[8] The low temperature serves two primary purposes:

-

Spontaneous Etching Inhibition: The rate of the spontaneous, isotropic chemical reaction between fluorine radicals and silicon is significantly reduced at cryogenic temperatures.[3]

-

Sidewall Passivation: A thin layer of silicon oxyfluoride (SiOₓFᵧ) forms on the sidewalls of the etched features.[6][8] This passivation layer is formed from the reaction of etching byproducts (SiF₄) and the added oxygen with the cold silicon surface.

Directional ion bombardment from the plasma is still necessary to remove the passivation layer at the bottom of the trench, allowing the etching to proceed vertically.[8] Because the passivation and etching occur simultaneously, cryogenic etching produces very smooth sidewalls without the characteristic scallops of the Bosch process.[2]

Quantitative Data and Process Parameters

The performance of deep silicon etching processes is characterized by several key metrics, including etch rate, selectivity, and aspect ratio. The following tables summarize typical quantitative data for both Bosch and cryogenic etching processes.

Table 1: Typical Bosch Process Parameters

| Parameter | Value | Reference |

|---|---|---|

| Etch Gas | SF₆ | [2] |

| Passivation Gas | C₄F₈ | [4] |

| SF₆ Flow Rate | 100 sccm | [5] |

| C₄F₈ Flow Rate | 85 sccm | [5] |

| ICP Power | 500 - 1000 W | [5] |

| Platen Power (RF) | 10 - 30 W | [5] |

| Chamber Pressure | 30 mTorr | [5] |

| Temperature | 10 °C | [5] |

| Etch Rate | 10 - 20 µm/min | [2] |

| Selectivity (Si:Photoresist) | > 150:1 | [9] |

| Selectivity (Si:SiO₂) | > 200:1 |[10] |

Table 2: Typical Cryogenic Etching Process Parameters

| Parameter | Value | Reference |

|---|---|---|

| Etch Gas | SF₆ | [6] |

| Passivation Gas | O₂ | [8] |

| SF₆ Flow Rate | 30 - 100 sccm | [11] |

| O₂ Flow Rate | 3 - 15 sccm | [7] |

| ICP Power | 600 - 750 W | [11] |

| Platen Power (RF) | 2 - 15 W | [7][11] |

| Chamber Pressure | 7 - 10 mTorr | [11] |

| Temperature | -100 to -130 °C | [7][11] |

| Etch Rate | 2 - 5 µm/min | [2] |

| Selectivity (Si:Photoresist) | ~70:1 - 89:1 | [7] |

| Selectivity (Si:SiO₂) | ~150:1 | |

Experimental Protocols

Substrate Preparation and Masking

A critical prerequisite for successful deep silicon etching is the preparation of a high-quality etch mask. This is typically achieved through photolithography.

-

Substrate Cleaning: Silicon wafers are rigorously cleaned to remove any organic and inorganic contaminants. A common procedure involves a piranha solution (a mixture of sulfuric acid and hydrogen peroxide). The wafer is then rinsed with deionized water and dried with nitrogen gas.

-

Adhesion Promotion: To ensure good adhesion of the photoresist to the silicon wafer, an adhesion promoter such as Hexamethyldisilane (HMDS) is often applied.

-

Photoresist Coating: A layer of photoresist, a light-sensitive polymer, is spin-coated onto the wafer to a desired thickness.

-

Soft Bake: The wafer is baked on a hot plate to evaporate the solvent from the photoresist.

-

Exposure: The photoresist is exposed to ultraviolet (UV) light through a photomask containing the desired pattern.

-

Post-Exposure Bake: A post-exposure bake is often performed to enhance the contrast of the pattern.

-

Development: The wafer is immersed in a developer solution, which selectively removes either the exposed (for positive photoresist) or unexposed (for negative photoresist) areas, revealing the pattern.

-

Hard Bake: A final bake at a higher temperature is performed to harden the photoresist and improve its resistance to the etching process.

For very deep etches or when using aggressive plasma chemistries, a hard mask such as silicon dioxide (SiO₂) or a metal like aluminum or chromium is used instead of photoresist due to their higher selectivity.

Deep Silicon Etching Procedure (General)

-

Wafer Loading: The prepared wafer is loaded into the DRIE chamber.

-

Process Recipe Execution: The appropriate etching recipe (Bosch or cryogenic) is selected and executed. The process parameters are carefully controlled to achieve the desired etch depth, profile, and sidewall characteristics.

-

Endpoint Detection: An endpoint detection system, such as optical emission spectroscopy, can be used to determine when the etch has reached the desired depth.

-

Wafer Unloading and Mask Removal: After the etching is complete, the wafer is removed from the chamber. The remaining mask material is stripped using appropriate solvents or plasma ashing.

Key Phenomena and Challenges

Aspect Ratio Dependent Etching (ARDE)

A significant challenge in deep silicon etching is Aspect Ratio Dependent Etching (ARDE), also known as RIE lag.[10] This phenomenon describes the observation that features with smaller widths (and thus higher aspect ratios for a given depth) etch slower than wider features. Several mechanisms contribute to ARDE:

-

Ion Shadowing: At high aspect ratios, the top corners of the feature can "shadow" the bottom, reducing the flux of ions reaching the etch front.

-

Neutral Transport Limitation: The transport of neutral reactant species (e.g., fluorine radicals) to the bottom of deep and narrow trenches becomes limited, reducing the chemical etch rate.

-

Byproduct Removal: The removal of volatile etch byproducts (e.g., SiF₄) from the bottom of high-aspect-ratio features is also hindered.

Other Etching Defects

Other common defects in deep silicon etching include:

-

Notching: Enhanced lateral etching at the interface of silicon and an underlying insulator layer (in Silicon-On-Insulator wafers).

-

Bowing: A curved or bowed sidewall profile.

-

Microtrenching: The formation of small trenches at the bottom corners of a feature.

-

Silicon Grass: The formation of needle-like silicon residues at the bottom of the etched feature, often due to micromasking by contaminants or excessive passivation.[5]

Conclusion

The fundamental mechanisms of deep silicon etching, embodied by the Bosch and cryogenic processes, are critical for the advancement of micro- and nanotechnology. The choice between these two powerful techniques depends on the specific application requirements, with the Bosch process offering higher etch rates and the cryogenic process providing smoother sidewalls. A thorough understanding of the underlying plasma chemistry, process parameters, and potential challenges such as ARDE is essential for researchers and scientists to successfully fabricate complex, high-aspect-ratio silicon structures for a myriad of applications, from next-generation electronics to innovative biomedical devices.

References

- 1. Critical aspect ratio dependence in deep reactive ion etching of silicon | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 2. azonano.com [azonano.com]

- 3. researchgate.net [researchgate.net]

- 4. Effects of Mask Material on Lateral Undercut of Silicon Dry Etching [mdpi.com]

- 5. researchgate.net [researchgate.net]

- 6. murata.com [murata.com]

- 7. microchemicals.com [microchemicals.com]

- 8. pubs.aip.org [pubs.aip.org]

- 9. pubs.aip.org [pubs.aip.org]

- 10. mtl.mit.edu [mtl.mit.edu]

- 11. research.engineering.ucdavis.edu [research.engineering.ucdavis.edu]

A Deep Dive into Anisotropic Etching: A Technical Guide to RIE and DRIE Processes

For Researchers, Scientists, and Drug Development Professionals

In the realm of microfabrication, the precise removal of material to create intricate three-dimensional structures is paramount. Among the arsenal (B13267) of techniques available, dry etching processes, particularly Reactive Ion Etching (RIE) and its advanced variant, Deep Reactive Ion Etching (DRIE), stand out for their ability to achieve high-fidelity pattern transfer with exceptional anisotropy. This technical guide provides an in-depth exploration of the core principles, experimental protocols, and key differences between RIE and DRIE, with a focus on their applications in research, scientific discovery, and the burgeoning field of drug development.

Fundamental Principles: A Tale of Two Etching Philosophies

At its core, Reactive Ion Etching (RIE) is a plasma-based process that synergistically combines chemical and physical mechanisms to remove material.[1] A chemically reactive gas is introduced into a vacuum chamber and ionized by a radio frequency (RF) electromagnetic field, creating a plasma of ions, electrons, and reactive neutral species.[1] An electric field accelerates these energetic ions towards the substrate, where they physically bombard the surface, a process known as sputtering. Simultaneously, the reactive neutral species chemically react with the substrate material, forming volatile byproducts that are subsequently pumped away.[2] This combination allows for directional etching, a key advantage over purely chemical wet etching methods.[2]

Deep Reactive Ion Etching (DRIE) is a specialized subclass of RIE developed to fabricate high-aspect-ratio microstructures, such as deep trenches and through-silicon vias (TSVs).[3] The primary distinction between RIE and DRIE lies in the achievable etch depth and anisotropy. While RIE is typically limited to depths of around 10 µm, DRIE can create features extending hundreds of micrometers deep with near-vertical sidewalls.[2][3] This remarkable capability is achieved through sophisticated sidewall passivation techniques, which are the hallmark of the two primary DRIE technologies: the Bosch process and the cryogenic process.

Quantitative Performance Metrics: A Comparative Analysis

The selection of an appropriate etching process is dictated by the specific requirements of the application, including the desired etch rate, selectivity, anisotropy, and achievable aspect ratio. The following tables summarize the key quantitative performance metrics for RIE, Bosch DRIE, and Cryogenic DRIE, primarily for silicon, the most common substrate in microfabrication.

| Process | Typical Etch Rate (Si) | Selectivity (Si:SiO₂) | Selectivity (Si:Photoresist) | Anisotropy (Depth:Width) |

| RIE | 0.1 - 1 µm/min[2][3] | 5:1 - 20:1 | 2:1 - 10:1 | < 10:1 |

| Bosch DRIE | 5 - 20 µm/min[3][4] | > 100:1[5] | > 75:1 | > 30:1[3] |

| Cryogenic DRIE | 3 - 10 µm/min | > 100:1 | > 50:1 | > 50:1 |

Table 1: Comparison of Etch Rate, Selectivity, and Anisotropy.

| Process | Typical Sidewall Roughness (RMS) | Key Advantages | Key Disadvantages |

| RIE | 5 - 20 nm | Simplicity, cost-effective for shallow etches. | Limited anisotropy and depth, lower selectivity.[2] |

| Bosch DRIE | 10 - 50 nm (scalloping)[6][7] | High etch rates, excellent selectivity, high aspect ratios.[8] | Sidewall scalloping, process complexity.[4] |

| Cryogenic DRIE | < 10 nm[6] | Very smooth sidewalls, high anisotropy.[8] | Lower etch rates than Bosch, requires cryogenic cooling.[4] |

Table 2: Comparison of Sidewall Roughness and Process Characteristics.

Experimental Protocols: A Guide to Practical Implementation

The success of any etching process hinges on the precise control of various experimental parameters. Below are detailed methodologies for key RIE and DRIE processes.

General Reactive Ion Etching (RIE) of Silicon

This protocol outlines a typical RIE process for etching silicon using a sulfur hexafluoride (SF₆) and oxygen (O₂) plasma.

Materials and Equipment:

-

RIE system with RF power supply (13.56 MHz)

-

Silicon wafer with a patterned mask (e.g., photoresist, silicon dioxide)

-

Process gases: SF₆, O₂, Argon (Ar)

-

Vacuum pumping system

Methodology:

-

Substrate Loading: Place the patterned silicon wafer onto the substrate electrode in the RIE chamber.

-

Chamber Evacuation: Evacuate the chamber to a base pressure typically in the range of 10⁻⁵ to 10⁻⁶ Torr.

-

Gas Introduction: Introduce the process gases into the chamber at controlled flow rates. A common gas mixture for silicon etching is SF₆ and O₂. Argon is often added as a sputtering agent to enhance physical etching.

-

Plasma Ignition: Apply RF power to the substrate electrode to ignite the plasma.

-

Etching: The energetic ions and reactive species in the plasma etch the exposed silicon. The process is monitored in real-time or timed to achieve the desired etch depth.

-

Process Termination: Turn off the RF power and gas flows.

-

Venting and Unloading: Vent the chamber to atmospheric pressure and unload the etched wafer.

Typical Process Parameters for Silicon RIE:

| Parameter | Range |

|---|---|

| SF₆ Flow Rate | 10 - 100 sccm |

| O₂ Flow Rate | 5 - 50 sccm |

| Pressure | 10 - 200 mTorr |

| RF Power | 50 - 300 W |

| DC Bias | -50 to -300 V |

Deep Reactive Ion Etching (DRIE) - The Bosch Process

The Bosch process is a time-multiplexed etching technique that alternates between an etching step and a passivation step to achieve deep, anisotropic trenches.[2]

Materials and Equipment:

-

DRIE system with high-density plasma source (e.g., ICP) and separate RF bias control

-

Silicon wafer with a patterned hard mask (e.g., silicon dioxide, silicon nitride)

-

Process gases: SF₆ (etchant), C₄F₈ (passivant)

-

Fast-switching mass flow controllers and pressure control

Methodology:

-

Substrate Loading and Evacuation: Similar to the RIE process.

-

Cyclic Etching and Passivation: The process cycles through the following steps, each lasting a few seconds:

-

Etch Step: An SF₆ plasma is ignited to isotropically etch the silicon.

-

Passivation Step: A C₄F₈ plasma is introduced, which deposits a protective fluorocarbon polymer layer on all surfaces.

-

Ion Bombardment: The directional ion bombardment from the subsequent etch step preferentially removes the polymer from the bottom of the feature, allowing the etch to proceed downwards, while the sidewalls remain protected.

-

-

Process Termination and Unloading: Similar to the RIE process. The number of cycles determines the final etch depth.

Typical Process Parameters for Bosch DRIE of Silicon:

| Parameter | Etch Step | Passivation Step |

|---|---|---|

| Gas | SF₆ | C₄F₈ |

| Flow Rate | 50 - 200 sccm | 50 - 150 sccm |

| ICP Power | 1000 - 2500 W | 800 - 2000 W |

| Bias Power | 10 - 100 W | 0 - 20 W |

| Pressure | 10 - 50 mTorr | 10 - 50 mTorr |

| Cycle Time | 2 - 10 seconds | 2 - 8 seconds |

Deep Reactive Ion Etching (DRIE) - The Cryogenic Process

The cryogenic DRIE process achieves anisotropy by performing the etch at very low temperatures, which inhibits the chemical etching on the sidewalls.

Materials and Equipment:

-

DRIE system with a cryogenic substrate holder capable of reaching temperatures below -100°C

-

Silicon wafer with a patterned mask

-

Process gases: SF₆, O₂

-

Liquid nitrogen supply for cooling

Methodology:

-

Substrate Loading and Cooling: The wafer is loaded onto the cryogenic chuck, which is then cooled to the desired process temperature (typically -110°C to -130°C).

-

Chamber Evacuation and Gas Introduction: The chamber is evacuated, and the process gases (SF₆ and O₂) are introduced.

-

Plasma Ignition and Etching: A high-density plasma is ignited. The low temperature slows down the spontaneous chemical reaction of fluorine radicals with silicon on the sidewalls. A thin layer of SiOxFy forms on the sidewalls, further passivating them. The energetic ions, however, continue to bombard the bottom of the feature, enabling directional etching.

-

Process Termination and Unloading: The plasma and gas flows are turned off, and the substrate is warmed up to room temperature before venting and unloading.

Typical Process Parameters for Cryogenic DRIE of Silicon:

| Parameter | Range |

|---|---|

| SF₆ Flow Rate | 50 - 200 sccm |

| O₂ Flow Rate | 5 - 20 sccm |

| ICP Power | 1000 - 2500 W |

| Bias Power | 5 - 50 W |

| Pressure | 5 - 20 mTorr |

| Temperature | -110°C to -130°C |

Process Mechanisms and Visualizations

The intricate interplay of chemical reactions and physical bombardment is best understood through visual representations of the process pathways.

Applications in Drug Development and Research

The precision and versatility of RIE and DRIE have opened up new frontiers in drug development and biomedical research. These techniques are instrumental in the fabrication of a wide array of microdevices that are revolutionizing how drugs are delivered, and how biological processes are studied.

-

Microneedles for Transdermal Drug Delivery: DRIE is extensively used to fabricate hollow or solid silicon microneedles.[9][10][11][12] These microneedles can painlessly penetrate the outer layer of the skin, the stratum corneum, to deliver drugs directly into the viable epidermis, enhancing drug bioavailability and enabling the delivery of macromolecules that cannot be administered orally.[9][13] The high-aspect-ratio capabilities of DRIE are crucial for creating sharp, robust needles with precise dimensions.[10][11][12]

-

Lab-on-a-Chip Devices for Drug Screening and Analysis: RIE and DRIE are fundamental to the fabrication of microfluidic "lab-on-a-chip" devices.[14][15][16] These miniaturized platforms integrate multiple laboratory functions on a single chip, enabling high-throughput screening of drug candidates, analysis of drug metabolites, and cell-based assays with minimal sample and reagent consumption.[14][17] The ability to create complex channel geometries and integrated features with high precision is a key advantage of these etching techniques.

-

Implantable Drug Delivery Systems: Microfabrication techniques, including RIE and DRIE, are employed to create sophisticated implantable devices for long-term, controlled drug release.[13] These devices can be designed with reservoirs and microchannels to deliver therapeutics at a precise rate directly to the target site, minimizing systemic side effects.

Conclusion

Reactive Ion Etching and Deep Reactive Ion Etching are indispensable tools in the microfabrication landscape, offering unparalleled control over the creation of intricate microstructures. While RIE provides a cost-effective solution for shallow etching, DRIE, through the Bosch and cryogenic processes, enables the fabrication of high-aspect-ratio features essential for a growing number of advanced applications. For researchers, scientists, and drug development professionals, a thorough understanding of the principles, capabilities, and practical considerations of these powerful techniques is crucial for driving innovation and translating microfabrication concepts into real-world solutions that can address pressing challenges in medicine and beyond.

References

- 1. corial.plasmatherm.com [corial.plasmatherm.com]

- 2. classweb.ece.umd.edu [classweb.ece.umd.edu]

- 3. Deep reactive-ion etching - Wikipedia [en.wikipedia.org]

- 4. azonano.com [azonano.com]

- 5. me.jhu.edu [me.jhu.edu]

- 6. researchgate.net [researchgate.net]

- 7. Comparison between Bosch and STiGer Processes for Deep Silicon Etching - PMC [pmc.ncbi.nlm.nih.gov]

- 8. Deep Reactive Ion Etching (DRIE) - Oxford Instruments [plasma.oxinst.com]

- 9. msmn.formulationbio.com [msmn.formulationbio.com]

- 10. pubs.aip.org [pubs.aip.org]

- 11. pubs.aip.org [pubs.aip.org]

- 12. Hollow silicon microneedle fabrication using advanced plasma etch technologies for applications in transdermal drug delivery - Lab on a Chip (RSC Publishing) [pubs.rsc.org]

- 13. mdpi.com [mdpi.com]

- 14. Lab-On-a-Chip drug testing in Microfluidics [elveflow.com]

- 15. researchgate.net [researchgate.net]

- 16. Revisiting lab-on-a-chip technology for drug discovery - PMC [pmc.ncbi.nlm.nih.gov]

- 17. esmed.org [esmed.org]

An In-depth Technical Guide to Key Parameters in Deep Reactive-Ion Etching (DRIE)

Audience: Researchers, scientists, and drug development professionals.

Introduction to Deep Reactive-Ion Etching (DRIE)

Deep Reactive-Ion Etching (DRIE) is a highly anisotropic plasma etching process used to create deep, steep-sided features in substrates, typically silicon. Developed for the fabrication of Micro-Electro-Mechanical Systems (MEMS), its applications have expanded to include high-density capacitor trenches for DRAM, through-silicon vias (TSVs) for 3D wafer-level packaging, microfluidics, and photonics.[1][2][3][4] The key characteristic of DRIE is its ability to produce high-aspect-ratio structures, meaning the etch depth is significantly greater than the feature width.

The DRIE process takes place in a reactor where a substrate is exposed to a plasma generated from various gases.[1] This plasma contains ions that are accelerated towards the substrate, where they react with the surface material to form volatile byproducts that are then pumped away.[1] This chemical etching is combined with a physical component, where the energetic ions can physically dislodge atoms from the substrate.[1] To achieve the high degree of anisotropy required for deep vertical etching, DRIE processes employ sidewall passivation techniques to prevent lateral etching.

There are two primary technologies for high-rate DRIE: the Bosch process and the cryogenic process.[1] The Bosch process, also known as pulsed or time-multiplexed etching, is the most widely recognized production technique and involves alternating between etching and passivation steps.[1] The cryogenic process, on the other hand, achieves sidewall passivation by cooling the substrate to very low temperatures.[1]

Core DRIE Technologies and Their Key Parameters

The success of a DRIE process is critically dependent on the precise control of several key parameters. These parameters influence the etch rate, selectivity, anisotropy, and sidewall profile.

The Bosch Process

The Bosch process, patented by the German company Robert Bosch GmbH, is a time-multiplexed etching technique that cycles between two main steps: an etching step and a passivation step.[1][5] This cyclic nature allows for the creation of nearly vertical sidewalls.[1]

-

Etching Step: A plasma containing fluorine-based radicals, typically from sulfur hexafluoride (SF6), isotropically etches the silicon substrate.[1][3]

-

Passivation Step: A fluorocarbon gas, commonly octafluorocyclobutane (B90634) (C4F8), is introduced to deposit a chemically inert passivation layer, similar to Teflon, on all surfaces.[1][3]

During the subsequent etch cycle, the directional ion bombardment removes the passivation layer from the bottom of the trench, allowing the etch to proceed downwards, while the passivation on the sidewalls remains largely intact, protecting them from lateral etching.[3] This alternating process, however, results in characteristic vertical ripples on the sidewalls known as "scalloping".[3]

The balance between the etch and passivation steps is crucial for achieving the desired etch profile. The key parameters that control this balance are:

-

Gas Flow Rates: The flow rates of the etchant gas (e.g., SF6) and the passivation gas (e.g., C4F8) directly impact the etch and deposition rates.

-

RF Power: The radio frequency (RF) power applied to the plasma source (Inductively Coupled Plasma - ICP) and the substrate (platen) controls the plasma density and ion energy, respectively. Higher ICP power generally increases the etch rate, while platen power influences the directionality of the etch and the removal of the passivation layer.[3]

-

Pressure: The chamber pressure affects the mean free path of the ions and radicals, influencing the conformality of the passivation layer and the directionality of the ion bombardment.

-

Cycle Time: The duration of the etch and passivation steps is a critical parameter for controlling the sidewall profile and the amount of scalloping.[3] Shorter cycles generally lead to smoother sidewalls but may have lower etch rates.

-

Substrate Temperature: The temperature of the wafer needs to be controlled, often with helium backside cooling, to prevent the degradation of the photoresist mask and the passivation layer.[3][5]

Table 1: Typical Bosch DRIE Process Parameters

| Parameter | Typical Range | Effect on Process |

| Etch Gas (SF6) Flow Rate | 50 - 300 sccm | Higher flow increases etch rate but can lead to more isotropic etching if not balanced with passivation. |

| Passivation Gas (C4F8) Flow Rate | 50 - 200 sccm | Higher flow improves sidewall protection, but excessive flow can lead to tapered profiles or "grass" formation. |

| ICP Power | 1000 - 3000 W | Increases plasma density, leading to higher etch rates. |

| Platen Power (Bias) | 10 - 150 W | Controls ion energy and directionality. Higher power improves anisotropy but can increase mask erosion. |

| Pressure | 10 - 100 mTorr | Affects ion and radical transport. Lower pressure improves directionality but can reduce etch rate. |

| Etch Step Time | 2 - 10 seconds | Longer time increases etch depth per cycle but can lead to more scalloping. |

| Passivation Step Time | 2 - 8 seconds | Longer time provides better sidewall protection but can lead to tapered profiles. |

| Substrate Temperature | -10 to 40 °C | Affects mask and passivation layer integrity. |

Note: These are general ranges and the optimal parameters are highly dependent on the specific DRIE tool, feature geometry, and desired outcome.

The Cryogenic Process

The cryogenic DRIE process offers an alternative to the Bosch process, particularly for applications requiring smoother sidewalls without the characteristic scalloping.[1] In this method, the substrate is cooled to very low temperatures, typically between -100°C and -140°C.

At these low temperatures, a passivation layer of silicon oxyfluoride (SiOxFy) is formed on the sidewalls from the reaction of the etching species (from SF6) and oxygen (O2), which is added to the plasma.[1] This passivation layer is less volatile at cryogenic temperatures and protects the sidewalls from lateral etching. The directional ion bombardment at the bottom of the trench is still effective at removing this layer, allowing the etch to proceed vertically.

-

Substrate Temperature: This is the most critical parameter in cryogenic DRIE. The temperature must be low enough to promote the formation of a stable passivation layer.

-

Gas Composition (SF6/O2 Ratio): The ratio of sulfur hexafluoride to oxygen is crucial for controlling the balance between etching and passivation. A higher O2 concentration generally leads to a thicker passivation layer and a more tapered profile.

-

RF Power (ICP and Platen): Similar to the Bosch process, ICP power controls the plasma density and etch rate, while platen power influences the ion energy and anisotropy.

-

Pressure: The chamber pressure affects the plasma characteristics and the transport of reactive species to the substrate.

Table 2: Typical Cryogenic DRIE Process Parameters

| Parameter | Typical Range | Effect on Process |

| Etchant Gas (SF6) Flow Rate | 50 - 200 sccm | Primary source of fluorine radicals for etching. |

| Passivation Gas (O2) Flow Rate | 5 - 50 sccm | Reacts with silicon and fluorine to form the SiOxFy passivation layer. |

| ICP Power | 800 - 2500 W | Controls plasma density and etch rate. |

| Platen Power (Bias) | 5 - 50 W | Influences ion energy and helps to remove the passivation layer at the trench bottom. |

| Pressure | 5 - 30 mTorr | Affects plasma uniformity and ion directionality. |

| Substrate Temperature | -140 to -100 °C | Critical for the formation and stability of the sidewall passivation layer. |

Note: These are general ranges and the optimal parameters are highly dependent on the specific DRIE tool, feature geometry, and desired outcome.

Experimental Protocols

While specific recipes are highly tool- and application-dependent, a general experimental workflow for a DRIE process can be outlined.

Generalized Experimental Workflow

References

Materials compatible with deep reactive-ion etching

An In-depth Technical Guide to Materials Compatible with Deep Reactive-Ion Etching

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides a comprehensive overview of materials compatible with deep reactive-ion etching (DRIE), a critical fabrication technique for creating high-aspect-ratio microstructures. This document is intended for researchers, scientists, and drug development professionals who utilize microfabrication for applications such as MEMS, microfluidics, and advanced drug delivery systems.

Deep reactive-ion etching is a highly anisotropic plasma etching process that enables the fabrication of deep, steep-sided trenches and holes in a substrate.[1][2] Unlike conventional reactive-ion etching (RIE), which is typically used for shallow pattern transfer, DRIE can create structures with depths of hundreds of microns and aspect ratios exceeding 50:1.[3] This capability is essential for the manufacturing of a wide range of devices, including microelectromechanical systems (MEMS), through-silicon vias (TSVs) for 3D electronics integration, and complex microfluidic channels for lab-on-a-chip applications.[4]

Two primary DRIE technologies are in widespread use: the Bosch process and the cryogenic process.[2] Both methods are capable of producing highly anisotropic etch profiles but employ different mechanisms for sidewall passivation, a critical step in preventing lateral etching and achieving vertical sidewalls.

Substrate Materials for DRIE

While silicon is the most common substrate material for DRIE, the technique can be adapted for a variety of other materials, each with unique properties suited for specific applications.

Silicon (Si)

Silicon is the cornerstone material for the semiconductor and MEMS industries due to its well-understood properties, high purity, and established processing techniques. DRIE of silicon is a mature technology, enabling the fabrication of complex microstructures with high precision and repeatability.[5]

Glass and Fused Silica (B1680970)

Glass and fused silica are attractive materials for microfluidics and optical applications due to their optical transparency, chemical inertness, and biocompatibility. DRIE of these materials is more challenging than silicon due to their insulating nature and lower etch rates. High plasma power is required, which in turn demands robust masking materials.[4][6]

Polymers

Polymers are increasingly used in microfabrication for applications requiring flexibility, biocompatibility, and low cost. Common polymers subjected to DRIE include SU-8 and PMMA. The etching of polymers often involves alternating steps of etching and passivation, similar to the Bosch process for silicon.[4][7]

III-V Semiconductors

Compound semiconductors such as Gallium Arsenide (GaAs) and Indium Phosphide (InP) are used in high-frequency electronics and optoelectronics. DRIE of these materials is possible, though less common than silicon, and typically employs different plasma chemistries.

Masking Materials for DRIE

The choice of masking material is critical for a successful DRIE process, as it must withstand the harsh plasma environment and provide the necessary etch selectivity to achieve the desired etch depth.

Photoresists

Photoresists are the most common masking materials due to their ease of patterning using standard photolithography. However, their selectivity to the substrate is often limited, and they can be susceptible to degradation and cracking, especially in cryogenic processes.[8][9]

Silicon Dioxide (SiO₂) and Silicon Nitride (Si₃N₄)

Silicon dioxide and silicon nitride are excellent hard masks for DRIE, offering significantly higher selectivity than photoresists.[2][9] They are typically deposited using techniques like thermal oxidation or chemical vapor deposition (CVD) and patterned using a preliminary RIE step with a photoresist mask.

Metals

Metal masks, such as aluminum (Al), nickel (Ni), and chromium (Cr), provide very high etch selectivity and are robust in aggressive plasma environments.[4] However, their use adds complexity to the fabrication process, requiring additional deposition and etching steps.

Aluminum Oxide (Al₂O₃)

Aluminum oxide is an exceptionally robust mask material, particularly for cryogenic DRIE, offering extremely high selectivity.[9]

Etch Stop Layers

Etch stop layers are used to precisely control the etch depth, particularly in the fabrication of structures on silicon-on-insulator (SOI) wafers or in multilayered devices. These layers are made of a material that has a very low etch rate in the specific DRIE chemistry being used. Common etch stop materials include silicon dioxide and heavily doped silicon layers.[5][10]

Quantitative Data for DRIE Processes

The following tables summarize key quantitative data for various material combinations in DRIE processes.

Table 1: Etch Rates and Selectivity for Silicon DRIE

| Substrate | Mask Material | Etch Rate (μm/min) | Selectivity (Substrate:Mask) | Process Type | Reference |