# Technical Support Center: DRIE Process Control for Repeatable Results

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |

|----------------------|-----------|-----------|

| Compound Name:       | DLRIE     |           |

| Cat. No.:            | B12398742 | Get Quote |

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to help researchers, scientists, and drug development professionals achieve repeatable results with their Deep Reactive Ion Etching (DRIE) processes.

## **Frequently Asked Questions (FAQs)**

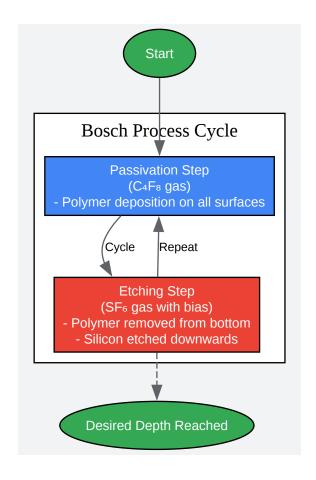

Q1: What is the Bosch process in DRIE?

The Bosch process is a widely used DRIE technique that enables the fabrication of high aspect ratio microstructures in silicon.[1] It is a cyclical process that alternates between two main steps:

- Passivation Step: A fluorocarbon gas, typically C<sub>4</sub>F<sub>8</sub>, is used to deposit a chemically inert polymer layer on all surfaces of the silicon wafer.[2][3] This layer protects the sidewalls from being etched.

- Etching Step: A fluorine-based gas, usually SF<sub>6</sub>, is introduced to isotropically etch the silicon.

[2][3] An applied bias directs ions to the bottom of the trench, where they remove the protective polymer layer, allowing the etch to proceed downwards.[4]

This cycle of passivation and etching is repeated to create deep, vertical structures.[2] The characteristic "scallops" on the sidewalls of DRIE-etched structures are a result of this alternating process.[4][5]

Q2: What are the key process parameters in a DRIE process and how do they affect the etch results?

Precise control of process parameters is crucial for achieving the desired etch profile and dimensions.[6] The key parameters include:

| Parameter                                                           | Effect on Etch Results                                                                                                                                                                                                           |  |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ICP (Inductively Coupled Plasma) Power                              | Primarily controls the plasma density and the generation of reactive species. Higher ICP power generally leads to a higher etch rate.[7]                                                                                         |  |

| Bias Power (Platen Power)                                           | Controls the energy of the ions bombarding the wafer surface. Higher bias power increases the directionality of the etch, leading to more vertical sidewalls, but can also increase mask erosion and the risk of notching.[7][8] |  |

| Pressure                                                            | Affects the mean free path of the reactive species and ions. Lower pressure during the etch cycle can lead to smoother sidewalls and reduced scalloping.[8][9]                                                                   |  |

| Gas Flow Rates (SF <sub>6</sub> and C <sub>4</sub> F <sub>8</sub> ) | The ratio of $SF_6$ to $C_4F_8$ flow rates determines<br>the balance between etching and passivation. A<br>higher $SF_6$ flow increases the etch rate, while a<br>higher $C_4F_8$ flow enhances passivation.[7]                  |  |

| Cycle Time (Etch vs. Passivation)                                   | The duration of the etch and passivation steps influences the size of the scallops and the overall etch profile. Shorter cycle times generally result in smaller scallops.[9][10]                                                |  |

| Wafer Temperature                                                   | Wafer cooling is essential to prevent the degradation of the passivation layer and ensure uniform etching.[2] Inadequate cooling can lead to a loss of profile control.[11]                                                      |  |

Q3: What is "micromasking" and how can it be prevented?

Micromasking occurs when unwanted particles or residues on the wafer surface act as a mask, preventing the underlying silicon from being etched and resulting in a rough, "grassy" surface. [12][13] To prevent micromasking:

- Ensure the wafer backside and edges are clean before processing.[13]

- Perform an oxygen plasma "descum" and a brief hydrofluoric acid (HF) dip before etching to remove any organic residues or native oxide.[13]

- If using a photoresist mask, ensure it is completely developed and that there is no edge bead.[13]

- For hard masks like Al<sub>2</sub>O<sub>3</sub>, ensure the mask etch is clean and all resist is stripped before the DRIE step.[12]

# Troubleshooting Guide Issue 1: Poor Verticality / Tapered Sidewalls

Symptoms: The etched sidewalls are not perpendicular to the surface, exhibiting a positive or negative taper.

| Cause                                     | Solution                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Imbalance between Etching and Passivation | A profile that is too positively sloped (wider at the top) indicates excessive passivation. Decrease the $C_4F_8$ flow or the passivation step time.[14] A re-entrant or negatively sloped profile (wider at the bottom) suggests insufficient passivation. Increase the $C_4F_8$ flow or the passivation step time.[14] |

| Low Bias Power                            | Insufficient ion energy can lead to less directional etching. Increase the bias power to promote vertical ion bombardment.[7]                                                                                                                                                                                            |

| High Pressure                             | High pressure can lead to more scattering of ions, reducing their directionality. Try reducing the process pressure.                                                                                                                                                                                                     |

## **Issue 2: Excessive Scalloping**

Symptoms: The sidewalls of the etched features have large, pronounced ripples.

| Cause                          | Solution                                                                                                                                                                                                    |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Long Cycle Times               | Longer etch and passivation cycles lead to larger scallops.[9] Reduce the cycle times to minimize scallop size.[10]                                                                                         |

| High Etch Rate                 | A very high etch rate can contribute to larger scallops. Consider reducing the SF <sub>6</sub> flow or ICP power to slow down the etch rate.                                                                |

| High Pressure during Etch Step | Higher pressure can increase the isotropic nature of the etch. Lowering the pressure during the etch cycle can result in smoother sidewalls.  [9]                                                           |

| Insufficient Passivation       | A thinner or less robust passivation layer can be more easily removed during the etch step, leading to larger undercuts. Increasing the C <sub>4</sub> F <sub>8</sub> flow or passivation time can help.[9] |

A post-DRIE smoothing step, such as a wet etch with a low concentration alkaline solution, can also be used to reduce scalloping.[15]

# Issue 3: Aspect Ratio Dependent Etching (ARDE) or RIE Lag

Symptoms: Features with different widths etch to different depths. Typically, wider features etch deeper than narrower features.[4][16][17] This is due to limitations in the transport of reactive species into and out of high aspect ratio features.[17]

| Cause                         | Solution                                                                                                              |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Depletion of Reactive Species | In high aspect ratio features, the concentration of fluorine radicals at the bottom of the trench is reduced.[17][18] |

| Ion Flux Reduction            | The flux of ions reaching the bottom of the feature decreases as the aspect ratio increases.  [17]                    |

#### Strategies to Minimize ARDE:

- Process Parameter Optimization: An optimized two-step Bosch process has been shown to reduce etch lag to below 1.5%.[4][16][19]

- Multi-Step Processes: A three-step Bosch process can be employed for fabricating deep structures with high aspect ratios.[4]

- Ramping Parameters: Ramping process parameters, such as the etch step time, can help to compensate for the decrease in etch rate as the aspect ratio increases.[20]

# Issue 4: Notching at the Dielectric Interface (e.g., on SOI wafers)

Symptoms: Lateral etching or undercutting occurs at the interface between the silicon device layer and the buried oxide (BOX) layer on a Silicon-On-Insulator (SOI) wafer.[18][21] This is often caused by charging effects at the insulating BOX layer.[22]

#### Possible Causes & Solutions:

| Cause                              | Solution                                                                                                       |

|------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Charging of the Buried Oxide Layer | The insulating BOX layer can accumulate charge, which deflects incoming ions and leads to lateral etching.[22] |

#### Strategies to Prevent Notching:

- Modified DRIE Process: A multi-step process involving the deposition of a conformal spacer oxide layer can be used to protect the sidewalls and prevent notching.[23][24]

- Conductive Stop Layers: Using a conductive stop layer can help to dissipate the charge buildup.[25]

- Process Optimization: Adjusting the ratio of the etching and passivation cycle times and the process pressure can help to minimize notching.[25]

### **Issue 5: Etch Stop**

Symptoms: The etching process stops before reaching the desired depth.

| Cause                        | Solution                                                                                                                                                                                                                 |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Excessive Polymer Deposition | Too much passivation can lead to the formation of a thick polymer layer at the bottom of the trench that the ions are unable to break through. Reduce the $C_4F_8$ flow or the passivation time.                         |

| Micromasking                 | As described in the FAQs, contaminants on the surface can act as a mask and halt the etching process.[12][13] Ensure proper wafer cleaning and preparation.                                                              |

| Hard Mask Failure            | If the etch mask erodes completely before the etch is finished, the underlying silicon will be exposed and may not etch as desired. Ensure the mask is sufficiently thick and has good selectivity for the DRIE process. |

| Chamber Conditioning         | In a multi-user environment, the chamber chemistry can be affected by previous processes. Running a chamber conditioning recipe before your process can help ensure repeatable results.[26]                              |

## **Experimental Protocols**

Protocol 1: Basic Chamber Conditioning

To ensure a stable and repeatable process, especially in a multi-user facility, it is recommended to condition the chamber before starting your DRIE process.

- Load a dummy silicon wafer into the process chamber.

- Run an oxygen plasma clean for 5-10 minutes to remove any residual fluorocarbon polymers.

- Follow with a standard DRIE recipe for 10-15 minutes to coat the chamber walls with a fresh passivation layer. This helps to stabilize the plasma conditions for your actual process.[26]

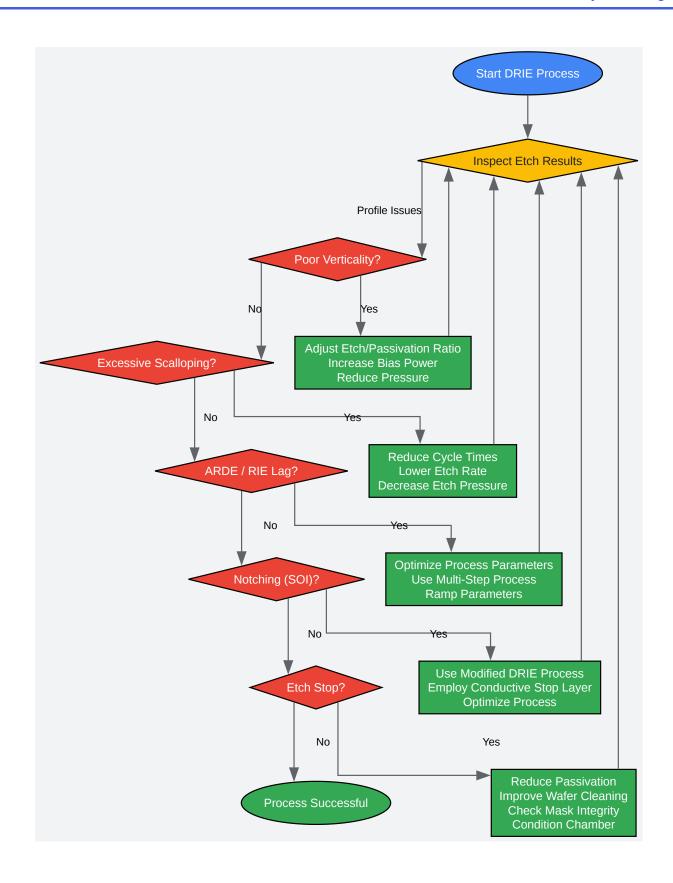

### **Visualizations**

Click to download full resolution via product page

Caption: A troubleshooting workflow for common DRIE process issues.

Click to download full resolution via product page

Caption: The cyclical nature of the Bosch process in DRIE.

### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. Deep Reactive Ion Etch (DRIE) [isit.fraunhofer.de]

- 2. ninescrolls.com [ninescrolls.com]

- 3. youtube.com [youtube.com]

- 4. Reduced Etch Lag and High Aspect Ratios by Deep Reactive Ion Etching (DRIE) [mdpi.com]

## Troubleshooting & Optimization

- 5. Reduced Etch Lag and High Aspect Ratios by Deep Reactive Ion Etching (DRIE) PMC [pmc.ncbi.nlm.nih.gov]

- 6. corial.plasmatherm.com [corial.plasmatherm.com]

- 7. pubs.aip.org [pubs.aip.org]

- 8. researchgate.net [researchgate.net]

- 9. researchgate.net [researchgate.net]

- 10. The Improvement of Performance through Minimizing Scallop Size in MEMS Based Micro Wind Turbine PMC [pmc.ncbi.nlm.nih.gov]

- 11. nrf.aux.eng.ufl.edu [nrf.aux.eng.ufl.edu]

- 12. researchgate.net [researchgate.net]

- 13. wiki.nanofab.usc.edu [wiki.nanofab.usc.edu]

- 14. mfz140.ust.hk [mfz140.ust.hk]

- 15. researchgate.net [researchgate.net]

- 16. Reduced Etch Lag and High Aspect Ratios by Deep Reactive Ion Etching (DRIE) -PubMed [pubmed.ncbi.nlm.nih.gov]

- 17. pubs.aip.org [pubs.aip.org]

- 18. samcointl.com [samcointl.com]

- 19. [2104.02763] Reduced etch lag and high aspect ratios by deep reactive ion etching (DRIE) [arxiv.org]

- 20. ispc-conference.org [ispc-conference.org]

- 21. researchgate.net [researchgate.net]

- 22. pubs.aip.org [pubs.aip.org]

- 23. pubs.aip.org [pubs.aip.org]

- 24. researchgate.net [researchgate.net]

- 25. researchgate.net [researchgate.net]

- 26. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: DRIE Process Control for Repeatable Results]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b12398742#drie-process-control-for-repeatable-results]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com