# Technical Support Center: Preventing Notching Effect at the SiO2 Interface in DRIE

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |

|----------------------|-----------|-----------|

| Compound Name:       | DLRIE     |           |

| Cat. No.:            | B12398742 | Get Quote |

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to help researchers, scientists, and drug development professionals prevent the notching effect at the silicon dioxide (SiO2) interface during Deep Reactive Ion Etching (DRIE).

# Frequently Asked Questions (FAQs) Q1: What is the notching effect at the SiO2 interface in DRIE?

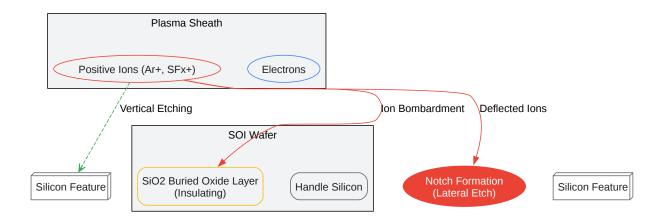

A1: The notching effect, also known as "footing," is the undesirable lateral etching of silicon at the interface with an underlying SiO2 stop layer. This phenomenon occurs during over-etching, which is often necessary to ensure complete etching of features with different sizes and aspect ratios across a wafer (due to RIE lag). The result is an undercut at the base of the silicon structures, which can compromise the mechanical integrity and performance of the fabricated devices.

### Q2: What is the primary cause of the notching effect?

A2: The primary cause of notching is a localized charging effect at the insulating SiO2 layer.[1] During the DRIE process, the exposed SiO2 surface accumulates positive charge from the ion bombardment. This charge buildup repels incoming positive ions, deflecting them towards the base of the silicon sidewalls. This oblique bombardment leads to aggressive lateral etching of the silicon at the Si/SiO2 interface, creating the characteristic notch.

## Q3: How does the aspect ratio of a feature affect notching?

A3: The notching effect is highly dependent on the aspect ratio of the etched features. Generally, wider trenches (with lower aspect ratios) are more susceptible to notching. This is because the insulating SiO2 layer at the bottom of wider trenches is more exposed to the plasma, leading to greater charge accumulation. For trenches with very high aspect ratios, the notching effect may be less severe or even negligible.[2]

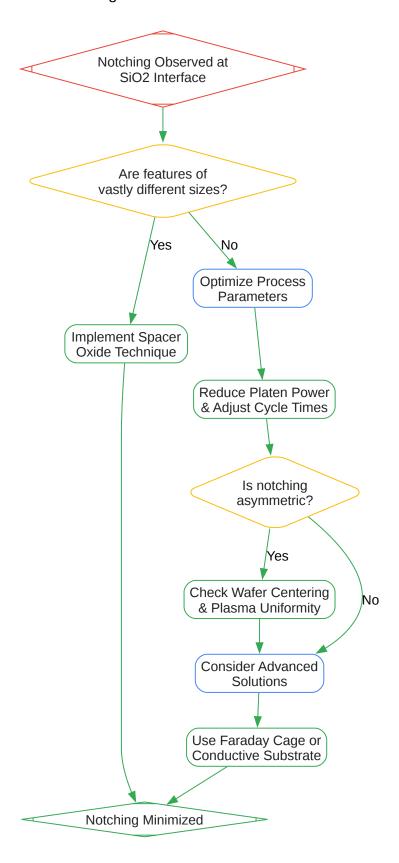

### **Troubleshooting Guide**

Problem: Significant notching is observed at the base of silicon features after DRIE on an SOI wafer.

### Troubleshooting & Optimization

Check Availability & Pricing

| Potential Cause                                    | Recommended Solution                                                                                                                                                                                                                                                                                                                                                                  | Underlying Principle                                                                                                                                                                                                                       |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Charge Accumulation on<br>Buried Oxide (BOX) Layer | 1. Process Parameter Optimization: Reduce platen power/bias voltage, and optimize etch/passivation cycle times. 2. Pulsed-Bias DRIE: If available, use a pulsed low- frequency bias to neutralize charge buildup during the etch cycle.[3] 3. Faraday Cage: Place the sample inside a Faraday cage within the etch chamber to create a field-free region and modify ion trajectories. | Reducing the ion energy and providing time for charge dissipation can minimize the deflection of ions that causes lateral etching. A Faraday cage alters the plasma sheath, directing ions more uniformly and reducing localized charging. |

| RIE Lag and Necessary Over-<br>etch                | Spacer Oxide Technique: Employ a multi-step etch and deposition process to protect the sidewalls of already-etched features during the over-etch step required for smaller features.                                                                                                                                                                                                  | By depositing a conformal layer of SiO2 after the larger features have reached the BOX layer, their sidewalls are protected from lateral etching while the smaller features continue to be etched vertically.                              |

| Substrate Conductivity Issues                      | Use of Specialized Substrates: For applications where it is feasible, using a Silicon-on- Glass (SOG) wafer with a thin metallic interlayer (e.g., Silicon-on-Patterned-Metal- and-Glass or SOMG) can eliminate the charging effect. [1]                                                                                                                                              | The metallic interlayer provides a conductive path for the charge to dissipate, preventing the buildup that leads to ion deflection and notching.[1]                                                                                       |

Problem: Notching is more severe in wider trenches compared to narrower ones.

| Potential Cause                                     | Recommended Solution                                                                                                                                                                                                                                          | Underlying Principle                                                                                                                                                                                                                          |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Aspect Ratio Dependent<br>Etching (ARDE) or RIE Lag | Layout and Design Compensation: If possible, design features with similar aspect ratios to minimize the required over-etch time. Multi- Step Etching (Spacer Oxide Technique): This is the most effective method for features with widely varying dimensions. | RIE lag causes smaller or high-aspect-ratio features to etch slower. By designing for uniform etch rates or protecting features that etch faster, the over-etch time and consequent notching on larger features can be significantly reduced. |

Problem: Asymmetric notching is observed (one side of a feature is notched more than the other).

| Potential Cause                         | Recommended Solution                                                                                                                                                                                                                                                                                                                          | Underlying Principle                                                                                                                                |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Non-Uniform Plasma<br>Distribution      | 1. Check and Optimize Chamber Conditions: Ensure the wafer is centered and the chamber is clean. Run chamber conditioning processes as recommended by the equipment manufacturer. 2. Adjust Gas Flow and Pressure: Variations in gas flow dynamics can lead to plasma non-uniformity. Experiment with slight adjustments to these parameters. | An uneven plasma density or ion flux across the wafer can lead to differential charging and etching, resulting in asymmetric notching.              |

| Feature Layout and Proximity<br>Effects | Layout Modification: Be mindful of the density and arrangement of features on the mask. Large open areas adjacent to dense features can sometimes lead to localized plasma non-uniformities.                                                                                                                                                  | The local density of features can affect the availability of reactive species and the local electric field, potentially causing asymmetric etching. |

### **Quantitative Data on Notching Prevention**

The effectiveness of different process parameters on notching and other DRIE results can be quantified. The following table summarizes key findings from various studies.

| Parameter<br>Adjusted          | Effect on<br>Notching                                   | Other Effects                                                                 | Quantitative<br>Observation                                                                                                                     | Source |

|--------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Platen Power /<br>Bias Voltage | Decreasing<br>power reduces<br>notching.                | Decreases etch rate; may affect anisotropy.                                   | Increasing platen<br>bias power from<br>5 W to 25 W can<br>dramatically<br>increase<br>undercut (a form<br>of lateral<br>etching).              | [4]    |

| Etch/Passivation<br>Cycle Time | Optimizing the balance can reduce notching.             | Affects sidewall scalloping and profile angle.                                | A study on reducing RIE lag showed that optimizing cycle times could reduce depth variation between 5 μm and 20 μm wide trenches to below 1.5%. | [5]    |

| Over-etch Time                 | Increased overetch time directly increases notch depth. | No significant effect on other profile features if the main etch is complete. | For 50-µm-deep trenches, notch depth can grow significantly with over-etch time, with wider trenches showing faster notch growth.               | [6]    |

| Aspect Ratio                   | Higher aspect ratio features exhibit less notching.     | Higher aspect ratios have lower etch rates (RIE lag).                         | Notching is often<br>negligible for<br>aspect ratios<br>greater than a<br>certain threshold                                                     | [2]    |

(e.g., >15-20), while it is significant for low aspect ratios.

# Experimental Protocols Protocol 1: Spacer Oxide Technique for Notching Prevention

This protocol describes a multi-step process to eliminate notching in structures with varying aspect ratios.

- · Initial DRIE Step:

- Perform the Bosch process DRIE to etch the widest trenches until they reach the buried

SiO2 layer.

- Typical Parameters: Use a standard Bosch recipe with alternating SF6 etch and C4F8 passivation steps.[7]

- Conformal SiO2 Deposition (Spacer Layer):

- Deposit a thin, conformal layer of silicon dioxide using Plasma-Enhanced Chemical Vapor

Deposition (PECVD). This layer will protect the sidewalls of the etched trenches.

- Typical PECVD SiO2 Recipe:

Precursors: SiH4 and N2O

Temperature: 250-300°C

■ Pressure: ~1 Torr

Power: 100 W

■ Deposition Rate: ~100-200 nm/min (deposit a layer thick enough to protect sidewalls during subsequent etching, e.g., 500 nm).

- Anisotropic SiO2 Etch (Spacer Removal from Trench Bottom):

- Perform a highly anisotropic RIE process to remove the deposited SiO2 from the bottom of the trenches, while leaving it on the sidewalls.

- Typical Anisotropic SiO2 Etch Recipe:

- Gases: CHF3 or CF4, often with Ar or O2.

- Pressure: 2-10 mTorr

- Bias Voltage/Power: 200-250 V / 150-200 W (to ensure directionality).[8][9]

- Endpoint Detection: Use optical emission spectroscopy or a timed etch to stop precisely on the silicon at the bottom of the narrower trenches.

- Subsequent DRIE Step(s):

- Continue the Bosch process DRIE to etch the next set of narrower trenches down to the buried SiO2 layer. The spacer oxide on the sidewalls of the wider trenches prevents them from notching.

- Repeat and Final Oxide Removal:

- Repeat steps 2-4 as necessary for features with multiple distinct size groups.

- After all silicon etching is complete, the protective spacer oxide can be removed using a

wet etch (e.g., buffered hydrofluoric acid) or a dry isotropic etch if required for the final

device.

## Protocol 2: Implementing a Faraday Cage in the DRIE Chamber

- Faraday Cage Construction:

- Construct a cage from a conductive material, such as aluminum or stainless steel mesh.

The mesh size should be small enough to create a relatively uniform electric field inside.

- The cage should be large enough to house the sample without it touching the sides.

- Experimental Setup:

- Place the Faraday cage on the platen in the DRIE chamber.

- Mount the sample inside the Faraday cage.

- Ensure the Faraday cage is electrically grounded to the platen. For many systems, this is achieved by simple physical contact.

#### • DRIE Process:

Run the DRIE process as usual. The cage will modify the plasma sheath, causing the ions

to be directed normal to the cage's surfaces. This results in a more uniform ion

bombardment on the sample, reducing the localized charging that causes notching.[10]

### **Visualizations**

Click to download full resolution via product page

Caption: Mechanism of the notching effect at the Si/SiO2 interface.

Click to download full resolution via product page

Caption: Troubleshooting workflow for DRIE notching.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. DRIE fabrication of notch-free silicon structures using a novel silicon-on-patterned metal and glass wafer [inis.iaea.org]

- 2. researchgate.net [researchgate.net]

- 3. files.core.ac.uk [files.core.ac.uk]

- 4. researchgate.net [researchgate.net]

- 5. 4.2.2 Etching of Silicon Dioxide [iue.tuwien.ac.at]

- 6. samcointl.com [samcointl.com]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- 9. wiki.nanofab.ucsb.edu [wiki.nanofab.ucsb.edu]

- 10. [1603.03735] Faraday cage angled-etching of nanostructures in bulk dielectrics [arxiv.org]

- To cite this document: BenchChem. [Technical Support Center: Preventing Notching Effect at the SiO2 Interface in DRIE]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b12398742#preventing-notching-effect-at-the-sio2-interface-in-drie]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

### BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com