JX040

Descripción

Propiedades

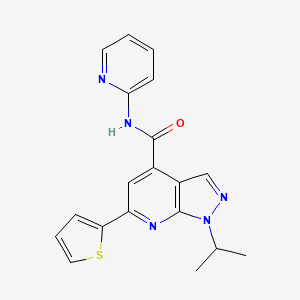

Fórmula molecular |

C19H17N5OS |

|---|---|

Peso molecular |

363.4 g/mol |

Nombre IUPAC |

1-propan-2-yl-N-pyridin-2-yl-6-thiophen-2-ylpyrazolo[5,4-b]pyridine-4-carboxamide |

InChI |

InChI=1S/C19H17N5OS/c1-12(2)24-18-14(11-21-24)13(10-15(22-18)16-6-5-9-26-16)19(25)23-17-7-3-4-8-20-17/h3-12H,1-2H3,(H,20,23,25) |

Clave InChI |

ZBXQJUDGXUEWEG-UHFFFAOYSA-N |

Apariencia |

Solid powder |

Pureza |

>98% (or refer to the Certificate of Analysis) |

Vida útil |

>2 years if stored properly |

Solubilidad |

Soluble in DMSO |

Almacenamiento |

Dry, dark and at 0 - 4 C for short term (days to weeks) or -20 C for long term (months to years). |

Sinónimos |

JX040; JX-040; JX 040; |

Origen del producto |

United States |

Foundational & Exploratory

The JX040 SCR: A Technical Analysis for Research Applications

An In-depth Technical Guide for Researchers, Scientists, and Drug Development Professionals

This technical guide provides a comprehensive analysis of the JX040 Silicon-Controlled Rectifier (SCR) chip. While the this compound is an electronic component primarily designed for power control applications, this paper will detail its technical specifications for researchers and scientists who may encounter it in laboratory equipment. Furthermore, to address the interests of drug development professionals, this guide will draw a parallel to the more biologically relevant "organ-on-a-chip" technology, which is at the forefront of preclinical research.

This compound SCR Chip: Core Technical Data

The this compound is a series of sensitive gate SCRs known for their high dV/dt rate and resistance to electromagnetic interference.[1][2] These characteristics make them suitable for applications such as voltage regulation, and in triggering mechanisms for devices like igniters and residual current circuit breakers.[1][2] The component is manufactured by JIEJIE MICROELECTRONICS CO., Ltd.[3][4][5]

Absolute Maximum Ratings

This table summarizes the absolute maximum ratings for the this compound series under specified conditions. Exceeding these values may cause permanent damage to the device.

| Parameter | Symbol | Value | Unit |

| Storage Junction Temperature Range | Tstg | -40 to 150 | ℃ |

| Operating Junction Temperature Range | Tj | -40 to 110 (up to 125 with ≤1kΩ gate-cathode resistor) | ℃ |

| Repetitive Peak Off-State Voltage | VDRM | 600 | V |

| Repetitive Peak Reverse Voltage | VRRM | 600 | V |

| RMS On-State Current (Package Dependent) | IT(RMS) | 4 | A |

| Non-Repetitive Surge Peak On-State Current (tp=10ms) | ITSM | 30 | A |

| I²t Value for Fusing (tp=10ms) | I²t | 4.5 | A²s |

| Peak Gate Current (tp=20µs, Tj=110℃) | IGM | 1.2 | A |

| Average Gate Power Dissipation (Tj=110℃) | PG(AV) | 0.2 | W |

Data sourced from the this compound Series datasheets.[1][2]

Electrical Characteristics (Tj=25℃ unless otherwise specified)

This table details the electrical characteristics of the this compound SCR, which are crucial for understanding its performance in a circuit.

| Parameter | Symbol | Test Condition | Min. | Typ. | Max. | Unit |

| On-State Voltage | VTM | IT=8A, tp=380µs | - | - | 1.5 | V |

| Off-State Leakage Current | IDRM / IRRM | VD=VDRM, VR=VRRM | - | - | 5 | µA |

| Off-State Leakage Current (Tj=110℃) | IDRM / IRRM | VD=VDRM, VR=VRRM | - | - | 100 | µA |

| Gate Trigger Current | IGT | VD=12V, RL=33Ω | - | - | 200 | µA |

| Gate Trigger Voltage | VGT | VD=12V, RL=33Ω | - | 0.6 | 0.8 | V |

| Gate Non-Trigger Voltage | VGD | VD=VDRM, Tj=110℃ | 0.2 | - | - | V |

| Latching Current | IL | IG=1.2 IGT | - | - | 6 | mA |

| Holding Current | IH | IT=0.05A | - | - | 5 | mA |

| Critical Rate of Rise of Off-State Voltage | dV/dt | VD=2/3VDRM, Tj=110℃, RGK=1KΩ | 50 | - | - | V/µs |

Data sourced from the this compound Series datasheets.[1][2]

Thermal Resistances

| Parameter | Symbol | Value | Unit |

| Junction to Case (DC) | Rth(j-c) | 7.5 | ℃/W |

| Junction to Ambient (DC) | Rth(j-a) | 120 | ℃/W |

Data sourced from the JX040Q datasheet.[2]

Experimental Protocols: Electrical Characterization of the this compound SCR

The "experiments" for the this compound involve electrical testing to ensure it meets its specified characteristics. The methodologies are defined by the test conditions in the electrical characteristics table.

1. On-State Voltage (VTM) Measurement:

-

Objective: To determine the voltage drop across the SCR when it is in the "on" or conducting state.

-

Methodology: A forward current (IT) of 8A is passed through the SCR for a short duration (tp=380µs). The voltage across the anode and cathode terminals is then measured. This is performed at a junction temperature (Tj) of 25℃.

2. Gate Trigger Current (IGT) and Voltage (VGT) Measurement:

-

Objective: To find the minimum gate current and voltage required to switch the SCR from an "off" to an "on" state.

-

Methodology: A DC voltage (VD) of 12V is applied across the anode and cathode with a load resistor (RL) of 33Ω. A gradually increasing current is applied to the gate terminal. The current and voltage at the gate at the precise moment the SCR switches on are recorded as IGT and VGT, respectively.

3. Latching (IL) and Holding (IH) Current Measurement:

-

Objective: To determine the minimum anode current required to keep the SCR in the "on" state after the gate signal is removed (latching current) and the minimum anode current to maintain the "on" state (holding current).

-

Methodology:

-

Latching Current: The SCR is triggered on with a gate current of 1.2 times the specified IGT. The anode current is then increased until it remains latched in the "on" state after the gate signal is removed.

-

Holding Current: With the SCR in the "on" state, the anode current is gradually decreased from a higher value (e.g., 0.05A) until the SCR switches to the "off" state. The anode current just before turn-off is the holding current.

-

4. Critical Rate of Rise of Off-State Voltage (dV/dt) Measurement:

-

Objective: To measure the SCR's ability to withstand a rapidly rising anode voltage without falsely triggering.

-

Methodology: With the gate open or connected to the cathode through a specified resistor (RGK=1KΩ), a voltage equal to two-thirds of the VDRM is applied across the SCR at an elevated junction temperature (Tj=110℃). The rate of rise of this voltage is increased until the SCR triggers without a gate signal.

Caption: Logical diagram of a this compound SCR in a basic power control circuit.

From Silicon Chips to "Organ-on-a-Chip": A Paradigm Shift for Drug Development

While the this compound is a silicon-based electronic chip, the term "chip" in modern drug development more commonly refers to "organ-on-a-chip" (OOC) or microphysiological systems.[6] These devices are revolutionizing preclinical research by providing more accurate models of human physiology than traditional 2D cell cultures or animal models.[7][8]

OOCs are microfluidic devices, typically made from a flexible polymer, that contain micro-channels lined with living human cells to emulate the structure and function of a human organ.[7][9] These systems can simulate blood flow, nutrient delivery, and even mechanical forces like breathing in a lung-on-a-chip.[7] By linking multiple OOCs, researchers can create a "human-body-on-a-chip" to study multi-organ interactions and a drug's pharmacokinetics and pharmacodynamics.[7][10]

The primary goal of OOC technology is to improve the efficiency and accuracy of preclinical drug evaluation, thereby reducing the high failure rate of drug candidates in human clinical trials.[6][9]

A Generalized Experimental Workflow for Drug Screening Using Organ-on-a-Chip

The following diagram illustrates a typical workflow for assessing the efficacy and toxicity of a new drug candidate using OOC technology.

Caption: A generalized workflow for preclinical drug testing using Organ-on-a-Chip technology.

References

- 1. surgecomponents.com [surgecomponents.com]

- 2. jjm.com [jjm.com]

- 3. This compound pdf, this compound Download, this compound Description, this compound Datasheet, this compound view ::: ALLDATASHEET ::: [pdfapp.alldatasheet.com]

- 4. This compound Datasheet(PDF) - JIEJIE MICROELECTRONICS CO.,Ltd [alldatasheet.com]

- 5. JX04 Datasheet(PDF) - JIEJIE MICROELECTRONICS CO.,Ltd [alldatasheet.com]

- 6. Organ-on-a-Chip: A new paradigm for drug development - PMC [pmc.ncbi.nlm.nih.gov]

- 7. m.youtube.com [m.youtube.com]

- 8. Transforming drug development with groundbreaking organ-on-chip tech | News | CORDIS | European Commission [cordis.europa.eu]

- 9. news.harvard.edu [news.harvard.edu]

- 10. Enhancing drug testing with human body-on-chip systems | EurekAlert! [eurekalert.org]

Unveiling the JX040 SCR: A Technical Guide to its Electrical Characteristics

For Immediate Release

This technical guide provides an in-depth analysis of the electrical characteristics of the JX040 series Silicon Controlled Rectifier (SCR), a sensitive gate thyristor known for its high dV/dt rate and robust resistance to electromagnetic interference.[1][2][3][4] This document is intended for researchers, scientists, and drug development professionals who may utilize this component in their instrumentation and experimental setups.

Core Electrical Characteristics

The this compound series SCRs are primarily designed for applications such as residual current circuit breakers, igniters, and other control circuits.[1][2][3] A comprehensive summary of their key electrical parameters is presented below, compiled from manufacturer datasheets. These values are crucial for understanding the device's switching behavior and operational limits.

Summary of Quantitative Data

| Parameter | Symbol | Test Condition | Min. | Typ. | Max. | Unit |

| Gate Trigger Current | IGT | VD=12V, RL=33Ω | - | 50 | 200 | µA |

| Gate Trigger Voltage | VGT | VD=12V, RL=33Ω | - | 0.6 | 0.8 | V |

| Non-Trigger Gate Voltage | VGD | VD=VDRM, Tj=110/125℃ | 0.2 | - | - | V |

| Latching Current | IL | IG=1.2 IGT | - | - | 6 | mA |

| Holding Current | IH | IT=0.05A | - | - | 5 | mA |

| On-State Voltage | VTM | IT=8A, tp=380µs, Tj=25℃ | - | - | 1.5 - 1.6 | V |

| Repetitive Peak Off-State Voltage | VDRM | Tj=25℃ | - | - | 600 | V |

| Repetitive Peak Reverse Voltage | VRRM | Tj=25℃ | - | - | 600 | V |

| RMS On-State Current | IT(RMS) | TC=85-97℃ (depending on package) | - | - | 4 | A |

| Critical Rate of Rise of Off-State Voltage | dV/dt | VD=2/3VDRM or 400V, Tj=110/125℃, RGK=1kΩ | 10/50 | - | - | V/µs |

| Off-State Leakage Current | IDRM/IRRM | VD=VDRM, VR=VRRM, Tj=25℃ | - | - | 5 | µA |

| Off-State Leakage Current | IDRM/IRRM | VD=VDRM, VR=VRRM, Tj=110/125℃ | - | - | 100/500 | µA |

Note: Values may vary slightly depending on the specific model (e.g., JX040K, JX040Q) and the manufacturer. Refer to the specific datasheet for precise values.[1][2][3]

Experimental Protocols

The characterization of the this compound SCR's electrical parameters involves a series of standardized tests. The methodologies for determining the key switching characteristics are outlined below.

Gate Trigger Voltage (VGT) and Current (IGT) Measurement

-

Setup: A variable DC voltage source is connected to the gate and cathode terminals of the SCR. A separate DC voltage (VD = 12V) is applied across the anode and cathode through a load resistor (RL = 33Ω).

-

Procedure: The gate voltage (VGT) is gradually increased from zero.

-

Measurement: The gate voltage and the corresponding gate current (IGT) are measured at the precise moment the SCR switches from its off-state (blocking) to its on-state (conducting). This transition is identified by the sudden drop in the anode-cathode voltage and the flow of load current.

Latching Current (IL) Measurement

-

Setup: The anode is supplied through a variable current source, and a gate current pulse (typically 1.2 times the maximum IGT) is applied to turn the SCR on.

-

Procedure: Immediately after the SCR turns on, the gate signal is removed. The anode current is then gradually increased.

-

Measurement: The latching current is the minimum anode current required to keep the SCR in the 'on' state after the gate signal has been removed.[5][6][7]

Holding Current (IH) Measurement

-

Setup: The SCR is in the 'on' state with a continuous anode current flowing (e.g., IT = 0.05A).

-

Procedure: The anode current is then gradually decreased.

-

Measurement: The holding current is the value of the anode current at which the SCR turns 'off' and reverts to its forward blocking state.[5][6][7]

Visualizing SCR Characteristics and Testing

To further clarify the concepts and procedures, the following diagrams illustrate the logical relationships between key SCR parameters and a typical experimental workflow for their characterization.

References

Technical Specifications of the JX040 Sensitive Gate SCR

The JX040 is a sensitive gate Silicon Controlled Rectifier (SCR) manufactured by JIEJIE MICROELECTRONICS CO.,Ltd.[1][2][3]. This electronic component is designed for applications requiring high dv/dt rates and strong resistance to electromagnetic interference, such as residual current circuit breakers and igniters[4][5]. As a semiconductor device, its function is governed by electrical principles and does not involve biological signaling pathways or drug development protocols.

Gate Triggering Characteristics

The gate is the terminal responsible for switching the SCR from a non-conducting "off" state to a conducting "on" state. This is achieved by applying a small voltage and current to the gate. The key parameters defining this switching action are the Gate Trigger Voltage (VGT) and Gate Trigger Current (IGT). These values represent the minimum voltage and current required at the gate to ensure the SCR switches on reliably under specified conditions[5].

The electrical characteristics for the this compound series are typically measured at a junction temperature (Tj) of 25°C unless otherwise specified[5].

Electrical Specification Summary

The primary gate trigger voltage and current specifications for the this compound series are summarized below.

| Parameter | Symbol | Test Condition | Min. | Typ. | Max. | Unit |

| Gate Trigger Current | IGT | VD = 12V, RL = 33Ω | - | - | 200 | µA |

| Gate Trigger Voltage | VGT | VD = 12V, RL = 33Ω | - | 0.6 | 0.8 | V |

| Gate Non-Trigger Voltage | VGD | VD = VDRM, Tj = 110℃ | 0.2 | - | - | V |

Table compiled from the this compound series datasheet[5].

Logical Relationship for SCR Triggering

The fundamental operational principle of the this compound SCR is its transition from a high-impedance (off) state to a low-impedance (on) state. This transition is initiated by the gate signal. The logical condition for this state change can be visualized as a simple workflow.

Note on Experimental Context

The request for detailed experimental protocols and signaling pathways, which are methodologies common in biological and chemical sciences, is not applicable to the characterization of this electronic component. The specifications of the this compound are determined through standardized electronic testing procedures, not through the types of experimental assays relevant to drug development professionals. The "experimental protocol" for determining gate trigger characteristics involves applying a controlled voltage and current to the gate terminal while the device is under specified load and temperature conditions and measuring the precise point at which it switches to a conducting state[5]. These test conditions are outlined in the "Test Condition" column of the specification table.

References

- 1. This compound pdf, this compound Download, this compound Description, this compound Datasheet, this compound view ::: ALLDATASHEET ::: [pdfapp.alldatasheet.com]

- 2. This compound Datasheet, PDF - Alldatasheet [alldatasheet.com]

- 3. Warning [alldatasheet.com]

- 4. datasheet4u.com [datasheet4u.com]

- 5. surgecomponents.com [surgecomponents.com]

An In-depth Technical Guide to the JX040 Sensitive Gate SCR

This technical guide provides a detailed overview of the JX040 series, a sensitive gate Silicon Controlled Rectifier (SCR). The this compound is designed for applications requiring high dv/dt rates and robust resistance to electromagnetic interference, making it particularly suitable for use in residual current circuit breakers, igniters, and other power control circuits. This document is intended for researchers, scientists, and professionals in electronic engineering and component application.

Core Electrical Characteristics

The this compound series is characterized by its stable performance across a range of operating conditions. A summary of its absolute maximum ratings and key electrical characteristics is provided below. These values are critical for ensuring reliable and safe operation within specified limits.

Data Presentation: Maximum Ratings and Electrical Specifications

The following tables summarize the key quantitative data for the this compound series SCR, based on the manufacturer's datasheets.[1][2]

Absolute Maximum Ratings

| Parameter | Symbol | Value | Unit |

| Repetitive Peak Off-State Voltage | VDRM | 600 | V |

| Repetitive Peak Reverse Voltage | VRRM | 600 | V |

| RMS On-State Current | IT(RMS) | 4 | A |

| Non-Repetitive Surge Peak On-State Current (tp=10ms) | ITSM | 30 | A |

| Critical Rate of Rise of On-State Current | dI/dt | 50 | A/µs |

| Peak Gate Current (tp=20µs, Tj=110℃) | IGM | 1.2 | A |

| Peak Gate Power (tp=20µs, Tj=110℃) | PGM | 2 | W |

| Average Gate Power Dissipation (Tj=110℃) | PG(AV) | 0.2 | W |

| Operating Junction Temperature Range | Tj | -40 to 110 | ℃ |

| Storage Junction Temperature Range | Tstg | -40 to 150 | ℃ |

Static Electrical Characteristics (Tj=25℃ unless otherwise specified)

| Parameter | Symbol | Test Condition | Max Value | Unit |

| Peak On-State Voltage | VTM | IT=8A, tp=380µs | 1.5 | V |

| Peak Off-State Current | IDRM | VD=VDRM, VR=VRRM | 5 | µA |

| Peak Reverse Current | IRRM | VD=VDRM, VR=VRRM | 5 | µA |

| Gate Trigger Current | IGT | VD=12V, RL=33Ω | 200 | µA |

| Gate Trigger Voltage | VGT | VD=12V, RL=33Ω | 0.8 | V |

| Holding Current | IH | IT=0.05A | 5 | mA |

| Latching Current | IL | IG=1.2 IGT | 6 | mA |

Experimental Protocols: Test Conditions for Electrical Characteristics

The electrical characteristics of the this compound SCR are determined under specific test conditions as outlined in the manufacturer's documentation.[1][2] These protocols ensure consistency and comparability of the component's performance metrics.

-

Gate Trigger Current (IGT) and Gate Trigger Voltage (VGT): These parameters are measured with a drain voltage (VD) of 12V and a load resistance (RL) of 33Ω.

-

Peak On-State Voltage (VTM): This is determined with a forward current (IT) of 8A for a pulse duration (tp) of 380µs.

-

Holding Current (IH): The holding current is measured at an on-state current (IT) of 0.05A.

-

Latching Current (IL): This is tested with a gate current (IG) that is 1.2 times the gate trigger current (IGT).

-

Critical Rate of Rise of Off-State Voltage (dV/dt): This is measured with a drain voltage (VD) at two-thirds of the VDRM, a junction temperature (Tj) of 110℃, and a gate-cathode resistance (RGK) of 1KΩ.

Operational Logic and State Transitions

The fundamental operation of the this compound SCR involves transitioning between a non-conducting (off) state and a conducting (on) state. The following diagram illustrates the logical relationship and the conditions required for these state changes.

The diagram above illustrates the two primary operational states of the this compound SCR. The device remains in the "Off State," blocking voltage, until a sufficient gate current (IGT) is applied while the anode-to-cathode voltage is positive. This triggers the transition to the "On State," where it conducts current. The SCR will return to the "Off State" if the anode current drops below the holding current (IH) or if the anode-to-cathode voltage is reversed.

References

JX040 SCR: A Comprehensive Technical Guide to Thermal Characteristics and Operating Temperature Range

For Researchers, Scientists, and Drug Development Professionals

This in-depth technical guide provides a detailed analysis of the thermal characteristics and operating temperature range of the JX040 series of Silicon Controlled Rectifiers (SCRs). The this compound is a sensitive SCR designed for applications such as residual current circuit breakers, igniters, and other control circuits. A thorough understanding of its thermal properties is critical for ensuring operational reliability and longevity in demanding applications. This document outlines the key thermal parameters, the methodologies for their determination, and the logical relationships governing the thermal performance of the device.

Quantitative Thermal Characteristics

The thermal performance of the this compound SCR is summarized in the tables below. Data is provided for two package variants: the JX040K (TO-252) and the JX040Q (TO-126). These values are essential for thermal modeling and heatsink design to maintain the junction temperature within safe operating limits.

Table 1: Absolute Maximum Ratings

| Parameter | Symbol | JX040K | JX040Q | Unit |

| Storage Junction Temperature Range | Tstg | -40 to 150 | -40 to 150 | °C |

| Operating Junction Temperature Range | Tj | -40 to 125¹ | -40 to 125¹ | °C |

¹ Note: The operating junction temperature (Tj) can be extended to 125°C when a resistor of less than or equal to 1kΩ is connected between the gate and cathode. Without this resistor, the maximum operating junction temperature is 110°C.[1][2]

Table 2: Thermal Resistances

| Parameter | Symbol | JX040K | JX040Q | Unit |

| Junction to Case (DC) | Rth(j-c) | 8.0 | 7.5 | °C/W |

| Junction to Ambient (DC) | Rth(j-a) | 100 | 120 | °C/W |

Experimental Protocols for Thermal Characterization

The determination of the thermal characteristics of SCRs like the this compound series adheres to standardized methodologies, such as those outlined by JEDEC (Joint Electron Device Engineering Council) and the IEC (International Electrotechnical Commission). While the specific internal testing procedures of the manufacturer are proprietary, the following describes a generalized, industry-standard approach to these measurements.

Measurement of Junction Temperature (Tj)

The junction temperature is a critical parameter that is not directly measurable in an operational circuit. Therefore, it is typically determined using an indirect method that leverages a temperature-sensitive electrical parameter (TSEP) of the device. For a thyristor, the forward voltage drop (VF) at a low sense current is a commonly used TSEP.

Methodology:

-

Calibration of the Temperature-Sensitive Electrical Parameter (TSEP):

-

The SCR is placed in a temperature-controlled environment, such as a thermal chamber or on a temperature-controlled plate.

-

The device is unpowered, and its case temperature is allowed to stabilize at a series of known temperatures (e.g., 25°C, 50°C, 75°C, 100°C, 125°C).

-

At each temperature, a small, constant measurement current is passed through the gate-cathode junction or the anode-cathode path. This current is low enough to not cause self-heating.

-

The corresponding forward voltage drop (VF) is measured at each temperature.

-

A calibration curve of VF versus temperature is plotted. This relationship is typically linear.

-

-

Heating and Measurement:

-

The SCR is mounted on a suitable heat sink and placed in the test environment.

-

A heating current is applied to the device to simulate operational power dissipation.

-

The device is allowed to reach thermal equilibrium, at which point the heating current is momentarily interrupted.

-

Immediately after the interruption, the small measurement current is applied, and the forward voltage drop is measured.

-

The junction temperature is then determined by correlating the measured forward voltage with the previously established calibration curve.

-

Measurement of Thermal Resistance (Rth)

Thermal resistance is a measure of a material's or interface's opposition to heat flow. It is calculated as the ratio of the temperature difference between two points to the power dissipated.

Methodology for Rth(j-c) (Junction-to-Case):

-

The SCR is mounted on an actively cooled heatsink or a cold plate, with a thermal interface material applied to ensure good thermal contact. The temperature of the case (Tc) is monitored with a thermocouple attached to a specified location on the package.

-

A known power (PD) is dissipated in the SCR by applying a current and voltage.

-

The device is allowed to reach thermal equilibrium, and the case temperature (Tc) is recorded.

-

The junction temperature (Tj) is determined using the TSEP method described above.

-

The junction-to-case thermal resistance is calculated using the formula: Rth(j-c) = (Tj - Tc) / PD

Methodology for Rth(j-a) (Junction-to-Ambient):

-

The SCR is mounted in a still-air chamber with a specified orientation to represent a typical operating environment without forced convection.

-

The ambient temperature (Ta) inside the chamber is monitored.

-

A known power (PD) is dissipated in the SCR.

-

The device is allowed to reach thermal equilibrium.

-

The junction temperature (Tj) is determined using the TSEP method.

-

The junction-to-ambient thermal resistance is calculated using the formula: Rth(j-a) = (Tj - Ta) / PD

Visualizations

The following diagrams illustrate key relationships in the thermal management of the this compound SCR.

References

An In-Depth Technical Guide to Latching and Holding Currents in JX040 SCR Circuits

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides a comprehensive overview of latching and holding currents in the context of JX040 series Silicon Controlled Rectifier (SCR) circuits. This document is intended for researchers, scientists, and drug development professionals who utilize electronic control systems in their experimental setups and require a thorough understanding of these fundamental SCR parameters.

Core Concepts: Latching and Holding Currents

In the operation of a Silicon Controlled Rectifier (SCR), two critical parameters dictate its switching behavior: the latching current (IL) and the holding current (IH) . Understanding the distinction between these two currents is paramount for the reliable design and troubleshooting of SCR-based circuits.

Latching Current (IL) is the minimum anode current that must be reached while the gate pulse is applied to ensure that the SCR remains in the 'ON' or conducting state after the gate signal is removed.[1][2] If the anode current does not rise to the latching current level while the gate is triggered, the SCR will turn 'OFF' as soon as the gate signal ceases. The latching current is associated with the turn-on process of the SCR.

Holding Current (IH) is the minimum anode current required to maintain the SCR in the 'ON' state.[1][2] Once the SCR is latched and conducting, if the anode current drops below the holding current, the device will revert to its 'OFF' or non-conducting state. The holding current is associated with the turn-off process of the SCR. A key characteristic is that the holding current is always less than the latching current (IH < IL).[3]

Quantitative Data for the this compound SCR Series

The this compound series are sensitive gate SCRs with a root-mean-square (RMS) on-state current of 4A and a repetitive peak off-state voltage of 600V.[4][5][6] The critical parameters of latching and holding currents for the this compound series at a junction temperature of 25°C are summarized in the table below.

| Parameter | Symbol | Test Condition | Maximum Value | Unit |

| Latching Current | IL | IG = 1.2 IGT | 6 | mA |

| Holding Current | IH | IT = 0.05 A | 5 | mA |

Note: These values are the maximum specified limits. The typical values may be lower. It is also important to note that both latching and holding currents are temperature-dependent. As the junction temperature increases, both the latching and holding currents tend to decrease. A representative graph from the JX040K datasheet illustrates this relationship, showing the normalized values of IGT, IH, and IL as a function of junction temperature.[5]

Experimental Protocols for Determining Latching and Holding Currents

Precise measurement of latching and holding currents is crucial for circuit design and validation. The following sections detail the methodologies for these measurements.

Experimental Setup

A generalized test circuit for measuring latching and holding currents is depicted below. The circuit consists of a variable DC voltage source (VAA) for the anode circuit, a separate DC voltage source (VG) for the gate trigger circuit, a current-limiting resistor for the gate (RG), and a variable load resistor (RL) to control the anode current. Ammeters are placed in series with the anode and gate to measure the respective currents (IA and IG).

Protocol for Measuring Latching Current (IL)

-

Circuit Assembly: Assemble the test circuit as shown in the diagram above. Set the variable load resistor (RL) to its maximum value to limit the initial anode current.

-

Initial State: Ensure the anode voltage (VAA) and gate voltage (VG) are set to zero.

-

Apply Anode Voltage: Set the anode voltage source (VAA) to a value below the forward breakover voltage of the this compound SCR.

-

Apply Gate Trigger: Apply a gate current (IG) pulse. According to the this compound datasheet, the test condition for IL is a gate current of 1.2 times the gate trigger current (IGT).[4]

-

Observe Latching: While the gate pulse is applied, gradually decrease the load resistance (RL) to increase the anode current (IA).

-

Remove Gate Trigger: Remove the gate trigger pulse.

-

Determine Latching: If the SCR remains 'ON', the anode current has exceeded the latching current. If the SCR turns 'OFF', the anode current was below the latching current.

-

Isolate IL: The latching current is the minimum anode current value at which the SCR remains conducting after the gate pulse is removed. This can be found by iteratively adjusting RL and applying gate pulses.

Protocol for Measuring Holding Current (IH)

-

Turn ON the SCR: Following the initial steps of the latching current measurement, ensure the SCR is in a stable 'ON' state with an anode current significantly above the expected holding current. The gate signal can now be removed.

-

Decrease Anode Current: Slowly and gradually increase the load resistance (RL) to decrease the anode current (IA).

-

Observe Turn-OFF: Monitor the anode current ammeter. The holding current is the value of the anode current just before the SCR abruptly turns 'OFF' and the anode current drops to zero (or a very small leakage current).[7] The this compound datasheet specifies a test condition of an initial on-state current (IT) of 0.05A for this measurement.[4]

Mandatory Visualizations

Signaling Pathway of SCR Triggering and Conduction

The following diagram illustrates the logical flow of events for an SCR to turn on and remain in the conducting state, highlighting the roles of gate trigger, latching current, and holding current.

Caption: Logical flow for SCR turn-on and conduction.

Experimental Workflow for Latching and Holding Current Measurement

The diagram below outlines the sequential workflow for the experimental determination of both latching and holding currents.

Caption: Workflow for measuring IL and IH.

References

JX040 dv/dt and di/dt ratings and their implications

An in-depth analysis of the user's request reveals a significant subject matter inconsistency. The topic specified, "JX040 dv/dt and di/dt ratings and their implications," pertains to the field of power electronics. Specifically, dv/dt (rate of change of voltage) and di/dt (rate of change of current) are critical parameters for semiconductor devices such as thyristors, Insulated Gate Bipolar Transistors (IGBTs), and Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs). These ratings define the maximum rate of voltage or current change the device can withstand without being damaged or malfunctioning.

However, the designated audience for this technical guide is "Researchers, scientists, and drug development professionals." The professional activities of this audience are focused on pharmacology, molecular biology, and therapeutic development. The operational characteristics of power electronic components have no discernible application or relevance to this field. It is therefore highly probable that the topic and the intended audience have been erroneously combined.

Given this fundamental discrepancy, it is not feasible to create a coherent and meaningful technical guide as requested. A document discussing the intricacies of semiconductor physics and circuit design would be of no practical use to professionals in the pharmaceutical and life sciences sectors. Conversely, attempting to metaphorically link these concepts to biological processes would be scientifically unsound and misleading.

To proceed, clarification on the intended subject matter is required. It is recommended that the user verify the topic and ensure it aligns with the expertise and interests of the target audience. For instance, if "this compound" is a designation for a compound, protein, or biological pathway, this information would be the correct foundation upon which to build the requested technical guide.

In the interest of providing a helpful response, a brief, generalized overview of dv/dt and di/dt ratings in their proper context is provided below.

In power electronics, the switching of semiconductor devices from a non-conducting (off) state to a conducting (on) state, and vice versa, must be carefully managed. The speed of these transitions is critical for efficiency but also introduces stresses on the components.

-

dv/dt (Rate of Change of Voltage): This rating specifies the maximum rate at which the voltage across the device (typically from anode to cathode in a thyristor) can rise without triggering an unintended turn-on. Exceeding the dv/dt rating can lead to a loss of control over the switching behavior of the device, potentially causing short circuits and system failure. The primary cause of this phenomenon is the charging current of the internal capacitance of the semiconductor junctions.

-

di/dt (Rate of Change of Current): This rating defines the maximum rate of rise of current through the device during turn-on. If the current rises too quickly, it can concentrate in a small area of the silicon die before spreading throughout the entire junction. This localized current density can lead to excessive heating, creating "hot spots" that can permanently damage or destroy the device.

The management of dv/dt and di/dt is a critical aspect of designing reliable power electronic circuits and often involves the use of snubber circuits, which are small networks of resistors and capacitors designed to limit these rates of change to safe levels.

Should the user provide a topic relevant to the field of drug development, a comprehensive technical guide incorporating data tables, experimental protocols, and Graphviz diagrams as originally requested can be produced.

An In-depth Technical Guide to the JX040 Sensitive Gate Silicon Controlled Rectifier

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides a detailed examination of the JX040, a sensitive gate silicon controlled rectifier (SCR). The content delves into the physical construction, semiconductor layers, and fabrication processes typical for a device of this class. Furthermore, it outlines comprehensive experimental protocols for the characterization of its electrical and thermal properties, and presents key performance data for the this compound.

Physical Construction and Semiconductor Layers

The this compound, like other silicon controlled rectifiers, is a four-layer semiconductor device with a P-N-P-N structure. This construction forms three P-N junctions in series. The device has three terminals: an anode, a cathode, and a gate, which serves as the control input.

The functionality of the SCR is dictated by the doping concentrations and thicknesses of its constituent semiconductor layers. While specific proprietary data for the this compound is not publicly available, the following table summarizes the typical layer characteristics for a sensitive gate SCR. The cathode is the most heavily doped layer, while the central N-type layer is the thickest and most lightly doped to support a high blocking voltage.

| Layer | Type | Typical Doping Concentration (atoms/cm³) | Typical Thickness (µm) |

| Anode | P+ | 10¹⁹ - 10²⁰ | 30 - 50 |

| Blocking Layer | N- | 10¹³ - 10¹⁴ | 50 - 200 |

| Gate | P | 10¹⁶ - 10¹⁷ | 10 - 20 |

| Cathode | N+ | > 10²⁰ | 5 - 15 |

Fabrication Workflow

The fabrication of a sensitive gate SCR such as the this compound involves a series of sophisticated processes to create the multi-layer P-N-P-N structure with high precision. The following diagram illustrates a typical fabrication workflow, primarily involving photolithography and diffusion processes.

Caption: A simplified workflow for the fabrication of a sensitive gate SCR.

Electrical and Thermal Characteristics of the this compound

The following tables summarize the key electrical and thermal performance parameters of the this compound series sensitive gate SCRs, as specified in their datasheets.[1][2][3]

Absolute Maximum Ratings

| Parameter | Symbol | Value | Unit |

| Repetitive Peak Off-State Voltage | VDRM/VRRM | 600 | V |

| RMS On-State Current | IT(RMS) | 4 | A |

| Peak Gate Power (tp=20µs) | PGM | 5 | W |

| Average Gate Power Dissipation | PG(AV) | 0.5 | W |

| Operating Junction Temperature Range | Tj | -40 to 125 | °C |

| Storage Temperature Range | Tstg | -40 to 150 | °C |

Electrical Characteristics (Tj = 25°C unless otherwise specified)

| Parameter | Symbol | Test Condition | Min. | Typ. | Max. | Unit |

| Gate Trigger Current | IGT | VD=12V, RL=33Ω | - | 50 | 200 | µA |

| Gate Trigger Voltage | VGT | VD=12V, RL=33Ω | - | 0.6 | 0.8 | V |

| Holding Current | IH | IT=0.05A | - | - | 5 | mA |

| Latching Current | IL | IG=1.2 IGT | - | - | 6 | mA |

| On-State Voltage | VTM | IT=8A, tp=380µs | - | - | 1.6 | V |

| Critical Rate of Rise of Off-State Voltage | dV/dt | VD=400V, Tj=125℃, RGK=1kΩ | 50 | - | - | V/µs |

Thermal Resistances

| Parameter | Symbol | Value | Unit |

| Junction to Case | Rth(j-c) | 3.5 | °C/W |

| Junction to Ambient | Rth(j-a) | 100 | °C/W |

Experimental Protocols

Electrical Characterization: V-I Characteristics, Latching Current, and Holding Current

Objective: To determine the voltage-current (V-I) characteristics of the this compound SCR and to measure its latching and holding currents.

Equipment:

-

Variable DC power supply (for anode-cathode circuit)

-

Variable DC power supply (for gate circuit)

-

Digital multimeters (2)

-

Resistors (as per test conditions)

-

This compound SCR device under test (DUT)

Procedure:

-

V-I Characteristics:

-

Construct the test circuit with the anode and cathode of the SCR connected to the main power supply through a load resistor.

-

Connect the gate and cathode to the second power supply through a current-limiting resistor.

-

With the gate circuit open, gradually increase the anode-to-cathode voltage (Vak) and measure the anode current (Ia). This will trace the forward blocking region.

-

Apply a small gate current (e.g., 50 µA) and repeat the previous step. Observe the lower breakover voltage.

-

Once the SCR is triggered, vary the load resistor to obtain different values of Ia and measure the corresponding Vak to trace the forward conduction region.

-

-

Latching Current (IL):

-

With the SCR in the off-state, apply a gate pulse to turn it on.

-

Immediately after triggering, remove the gate signal.

-

The minimum anode current required to keep the SCR in the on-state is the latching current.

-

-

Holding Current (IH):

-

With the SCR in the on-state, gradually decrease the anode current by increasing the load resistance.

-

The value of the anode current just before the SCR switches to the off-state is the holding current.

-

Thermal Characterization: Transient Thermal Analysis

Objective: To analyze the transient thermal behavior of the this compound under pulsed power conditions.

Equipment:

-

High-current pulse generator

-

Infrared (IR) thermal camera

-

Thermocouples

-

Data acquisition system

-

Test fixture with appropriate heat sinking for the this compound

Procedure:

-

Mount the this compound on the test fixture, ensuring good thermal contact with the heat sink.

-

Attach thermocouples to the case of the device to monitor its temperature.

-

Position the IR thermal camera to have a clear view of the device package.

-

Apply single or repetitive high-current pulses to the SCR.

-

Simultaneously record the temperature of the device case using the thermocouples and the temperature distribution on the package surface using the IR camera.

-

Analyze the recorded data to determine the transient thermal impedance and the rate of temperature rise under different pulse conditions. This data is crucial for establishing the safe operating area (SOA) of the device.

Signaling and Control

The fundamental control mechanism of the this compound is the application of a current pulse to the gate terminal. The following diagram illustrates the logical relationship between the gate signal and the state of the SCR.

Caption: Logical control diagram for an SCR.

References

An In-depth Technical Guide to the Turn-on and Turn-off Time Characteristics of the OX40-OX40L Interaction

Disclaimer: Initial searches for a drug or compound designated "JX040" relevant to drug development and life sciences did not yield any specific information. The provided technical guide uses the well-characterized interaction between the immune receptor OX40 and its ligand OX40L as a representative example to fulfill the structural and content requirements of the request. This guide is intended to serve as a template for presenting kinetic binding data, experimental protocols, and signaling pathways for a biological therapeutic.

This technical guide provides a detailed overview of the binding kinetics, experimental methodologies for their determination, and the downstream signaling pathways associated with the interaction of the co-stimulatory receptor OX40 (also known as CD134 or TNFRSF4) and its ligand, OX40L (CD252 or TNFSF4). This information is critical for researchers, scientists, and drug development professionals working on immunotherapies targeting this pathway.

Data Presentation: OX40-OX40L Binding Kinetics

The "turn-on" (association) and "turn-off" (dissociation) rates are fundamental parameters that define the affinity and duration of the OX40-OX40L interaction. These have been quantified using various biophysical techniques, most notably Surface Plasmon Resonance (SPR). The following table summarizes key kinetic data from studies on this interaction.

| Interacting Molecules | Method | Association Rate (k_on) (M⁻¹s⁻¹) | Dissociation Rate (k_off) (s⁻¹) | Equilibrium Dissociation Constant (K_D) (nM) | Reference |

| Soluble murine OX40L binding to immobilized murine OX40 | Surface Plasmon Resonance (BIAcore) | Not explicitly stated | 4 x 10⁻⁵ | 0.2-0.4 | [1][2] |

| Soluble murine OX40L binding to immobilized murine OX40 | Surface Plasmon Resonance (BIAcore) | Not explicitly stated | Not explicitly stated | 3.8 | [1][2] |

| Soluble murine OX40 binding to immobilized murine OX40L | Surface Plasmon Resonance (BIAcore) | Not explicitly stated | 2 x 10⁻² | 190 | [1][2] |

Note: The variability in reported K_D values can be attributed to differences in experimental setup, such as which molecule is immobilized and which is in solution, as well as the specific constructs of the proteins used.

Experimental Protocols: Determination of Binding Kinetics using Surface Plasmon Resonance (SPR)

The following protocol provides a generalized methodology for measuring the binding kinetics of the OX40-OX40L interaction using an SPR-based biosensor, such as a BIAcore instrument.[1][2][3][4][5][6]

Objective: To determine the association rate (k_on), dissociation rate (k_off), and equilibrium dissociation constant (K_D) for the OX40-OX40L interaction.

Materials:

-

Recombinant soluble human or murine OX40 extracellular domain (ligand)

-

Recombinant soluble human or murine OX40L extracellular domain (analyte)

-

SPR sensor chip (e.g., CM5 chip for amine coupling)

-

Amine coupling kit (containing N-hydroxysuccinimide (NHS), 1-ethyl-3-(3-dimethylaminopropyl)carbodiimide hydrochloride (EDC), and ethanolamine-HCl)

-

SPR running buffer (e.g., HBS-EP buffer: 0.01 M HEPES pH 7.4, 0.15 M NaCl, 3 mM EDTA, 0.005% v/v Surfactant P20)

-

Regeneration solution (e.g., a low pH buffer like glycine-HCl)

Procedure:

-

Ligand Immobilization:

-

Equilibrate the sensor chip with running buffer.

-

Activate the carboxymethylated dextran surface of the sensor chip by injecting a mixture of NHS and EDC.

-

Inject the soluble OX40 protein (ligand) at a low concentration in a low ionic strength buffer (e.g., 10 mM sodium acetate, pH 4.5) to promote pre-concentration on the surface.

-

Deactivate any remaining active esters by injecting ethanolamine-HCl. This blocks unreacted groups on the sensor surface.

-

A reference flow cell should be prepared in the same way but without the injection of the ligand to allow for subtraction of bulk refractive index changes and non-specific binding.

-

-

Analyte Interaction Analysis:

-

Inject a series of concentrations of the soluble OX40L (analyte) over both the ligand-immobilized and reference flow cells at a constant flow rate. The binding is monitored in real-time as an increase in resonance units (RU). This is the association phase .

-

After the injection of the analyte, switch back to flowing only the running buffer over the sensor surface. The decrease in RU over time is monitored. This is the dissociation phase .

-

Between different analyte concentrations, the sensor surface is regenerated by injecting a pulse of the regeneration solution to remove all bound analyte. The regeneration solution should be chosen carefully to ensure it removes the analyte completely without denaturing the immobilized ligand.

-

-

Data Analysis:

-

The sensorgrams (plots of RU versus time) are processed by subtracting the signal from the reference flow cell from the signal from the ligand-immobilized flow cell.

-

The resulting sensorgrams for each analyte concentration are then fitted to a kinetic binding model (e.g., a 1:1 Langmuir binding model) using the instrument's analysis software.

-

This fitting process yields the association rate constant (k_on) and the dissociation rate constant (k_off).

-

The equilibrium dissociation constant (K_D) is then calculated as the ratio of k_off to k_on (K_D = k_off / k_on).

-

Mandatory Visualizations

OX40 Signaling Pathway

The interaction between OX40 on activated T-cells and OX40L on antigen-presenting cells (APCs) initiates a downstream signaling cascade that is crucial for T-cell survival, proliferation, and cytokine production.[7][8][9][10][11][12][13]

-

Receptor-Ligand Binding and TRAF Recruitment: Upon binding of OX40L, the OX40 receptors on the T-cell surface trimerize.[7] This conformational change leads to the recruitment of TNF receptor-associated factors (TRAFs), primarily TRAF2 and TRAF5, to the cytoplasmic tail of the OX40 receptor.[7][8]

-

Activation of Downstream Pathways:

-

NF-κB Pathway: The recruited TRAF proteins activate the IκB kinase (IKK) complex.[8] The IKK complex then phosphorylates the inhibitor of NF-κB (IκB), leading to its ubiquitination and degradation. This releases the nuclear factor-κB (NF-κB) transcription factor, allowing it to translocate to the nucleus and initiate the transcription of target genes.[7]

-

PI3K/Akt Pathway: The OX40-TRAF complex also leads to the activation of the Phosphoinositide 3-kinase (PI3K) pathway.[7][9] PI3K activation leads to the phosphorylation and activation of the serine/threonine kinase Akt (also known as Protein Kinase B).

-

-

Cellular Outcomes: The activation of these signaling pathways results in several key outcomes for the T-cell:

-

Enhanced Survival: Both the NF-κB and Akt pathways promote T-cell survival by upregulating the expression of anti-apoptotic proteins such as Bcl-2, Bcl-xL, and survivin.[8][10]

-

Increased Proliferation: The signaling cascade enhances T-cell proliferation, leading to clonal expansion of antigen-specific T-cells.

-

Augmented Cytokine Production: OX40 signaling boosts the production of various cytokines, such as IL-2, which further promotes T-cell growth and function.[11]

-

Memory T-cell Formation: This co-stimulatory signal is critical for the development and maintenance of long-lived memory T-cells.[9]

-

References

- 1. Affinity and kinetics of the interaction between soluble trimeric OX40 ligand, a member of the tumor necrosis factor superfamily, and its receptor OX40 on activated T cells - PubMed [pubmed.ncbi.nlm.nih.gov]

- 2. researchgate.net [researchgate.net]

- 3. path.ox.ac.uk [path.ox.ac.uk]

- 4. Measuring binding kinetics of surface-bound molecules using the surface plasmon resonance technique - PubMed [pubmed.ncbi.nlm.nih.gov]

- 5. Binding Kinetics and Epitope Binning Using Surface Plasmon Resonance - PubMed [pubmed.ncbi.nlm.nih.gov]

- 6. Measuring antibody-antigen binding kinetics using surface plasmon resonance - PubMed [pubmed.ncbi.nlm.nih.gov]

- 7. bpsbioscience.com [bpsbioscience.com]

- 8. researchgate.net [researchgate.net]

- 9. The Significance of OX40 and OX40L to T cell Biology and Immune Disease - PMC [pmc.ncbi.nlm.nih.gov]

- 10. creative-diagnostics.com [creative-diagnostics.com]

- 11. The role of OX40-mediated co-stimulation in T cell activation and survival - PMC [pmc.ncbi.nlm.nih.gov]

- 12. geneglobe.qiagen.com [geneglobe.qiagen.com]

- 13. Regulation of T Cell Immunity by OX40 and OX40L - Madame Curie Bioscience Database - NCBI Bookshelf [ncbi.nlm.nih.gov]

In-Depth Technical Guide to the Sensitive Gate Feature of the JX040 Silicon Controlled Rectifier

For Researchers, Electronics Engineers, and Semiconductor Professionals

This technical guide provides a detailed exploration of the sensitive gate characteristics of the JX040 Silicon Controlled Rectifier (SCR). The this compound series is designed for applications requiring high dV/dt rates and strong resistance to electromagnetic interference, making it particularly suitable for circuits such as residual current circuit breakers, igniters, and other low-power switching applications.[1][2][3] The sensitive gate feature allows the device to be triggered with very low gate currents, a critical requirement in many control circuits.

Core Electrical Characteristics and Absolute Maximum Ratings

The operational parameters of the this compound SCR are summarized below. These values are critical for circuit design and ensuring the reliability of the device under various operating conditions.

Absolute Maximum Ratings

Exceeding these ratings may result in permanent damage to the device.

| Parameter | Symbol | Value | Unit |

| Storage Junction Temperature Range | Tstg | -40 to 150 | °C |

| Operating Junction Temperature Range | Tj | -40 to 125 | °C |

| Repetitive Peak Off-State Voltage (Tj=25°C) | VDRM | 600 | V |

| Repetitive Peak Reverse Voltage (Tj=25°C) | VRRM | 600 | V |

| RMS On-State Current (TC≤93°C) | IT(RMS) | 4 | A |

| Average On-State Current (TC≤93°C) | IT(AV) | 2.5 | A |

| Non-Repetitive Surge Peak On-State Current (tp=10ms, Tj=25°C) | ITSM | 40 | A |

| Critical Rate of Rise of On-State Current (IG=2xIGT, f=100Hz, Tj=125°C) | dI/dt | 50 | A/μs |

| Peak Gate Current (tp=20μs, Tj=125°C) | IGM | 2 | A |

| Average Gate Power Dissipation (Tj=125°C) | PG(AV) | 0.5 | W |

Data sourced from the JX040K datasheet.[1]

Electrical Characteristics (Tj=25°C unless otherwise specified)

These parameters define the triggering and on-state characteristics of the this compound's sensitive gate.

| Parameter | Symbol | Test Condition | Min. | Typ. | Max. | Unit |

| Gate Trigger Current | IGT | VD=12V, RL=33Ω | - | 50 | 200 | μA |

| Gate Trigger Voltage | VGT | VD=12V, RL=33Ω | - | 0.6 | 0.8 | V |

| Gate Non-Trigger Voltage | VGD | VD=VDRM, Tj=125°C | 0.2 | - | - | V |

| Latching Current | IL | IG=1.2 IGT | - | - | 6 | mA |

| Holding Current | IH | IT=0.05A | - | - | 5 | mA |

| Critical Rate of Rise of Off-State Voltage | dV/dt | VD=400V, Tj=125°C, RGK=1kΩ | 50 | - | - | V/μs |

Data sourced from the JX040K and this compound Series datasheets.[1][2]

Experimental Protocols

The following sections describe the methodologies for testing the key parameters of the this compound sensitive gate SCR. These protocols are based on standard industry practices for thyristor characterization.

Gate Trigger Current (IGT) and Gate Trigger Voltage (VGT) Measurement

Objective: To determine the minimum gate current (IGT) and gate voltage (VGT) required to switch the SCR from the off-state to the on-state.

Methodology:

-

Configure the test circuit as shown in the "SCR Triggering Test Circuit" diagram.

-

Set the anode voltage (VD) to 12V with a load resistor (RL) of 33Ω.

-

Initially, the gate voltage (Vg) is set to 0V.

-

Gradually increase the gate current (IG) by adjusting the variable voltage source connected to the gate.

-

Continuously monitor the anode-to-cathode voltage (VAK).

-

The SCR will trigger, and the VAK will drop to a low on-state voltage.

-

Record the gate current (IG) and gate voltage (VG) at the point of triggering. These values correspond to IGT and VGT, respectively.

Latching Current (IL) and Holding Current (IH) Measurement

Objective: To determine the minimum anode current required to latch the SCR in the on-state after the gate signal is removed (IL), and the minimum anode current to maintain the on-state (IH).

Methodology for Latching Current (IL):

-

Trigger the SCR using a gate current of 1.2 times the measured IGT.

-

Once the SCR is in the on-state, remove the gate signal.

-

Gradually increase the anode current (IA) by adjusting the anode circuit's variable voltage source.

-

The minimum anode current at which the SCR remains in the on-state after the gate signal is removed is the latching current.

Methodology for Holding Current (IH):

-

Ensure the SCR is in a stable on-state with an anode current well above the expected holding current (e.g., 50mA).

-

Gradually decrease the anode current by reducing the anode circuit's voltage.

-

The anode current value just before the SCR switches to the off-state (VAK rises to the anode supply voltage) is the holding current.

Visualizations

SCR Two-Transistor Model and Triggering

The fundamental operation of an SCR can be visualized using a two-transistor analogy, which helps in understanding the regenerative action that leads to latching.

SCR Two-Transistor Analogy

This diagram illustrates how a gate current applied to the base of the NPN transistor initiates a regenerative feedback loop, causing both transistors to saturate and latch the SCR in the "on" state.

SCR Triggering Test Circuit Workflow

The following diagram outlines the logical workflow for testing the gate trigger characteristics of the this compound SCR.

Gate Trigger Test Workflow

This flowchart details the step-by-step process for accurately measuring the gate trigger current (IGT) and gate trigger voltage (VGT) of the this compound SCR.

References

Methodological & Application

Introduction: Core Principles of MOSFET Gate Driver Design

Application Note: A General Framework for Designing Stable Gate Driver Circuits for Power Switching Devices

Notice: The component identifier "JX040" corresponds to a Sensitive Gate Silicon-Controlled Rectifier (SCR) manufactured by JIEJIE MICROELECTRONICS.[1][2][3][4] An SCR is a thyristor, not a transistor like a MOSFET or IGBT, and its gating (turn-on) requirements are fundamentally different. A continuous, high-speed switching gate driver as typically designed for a MOSFET is not the appropriate circuit for an SCR. An SCR is latched on by a single gate pulse and turns off only when its anode current falls below a holding current level.

This document proceeds by providing a detailed, general methodology for designing a stable gate driver for a power MOSFET , as this is a common requirement in high-frequency power electronics. The principles and protocols discussed can be adapted for other voltage-controlled transistors like IGBTs. Researchers using the this compound SCR should consult its datasheet for specific gate trigger current (IGT) and voltage (VGT) requirements to design a simple trigger circuit, rather than the complex driver described below.

A gate driver circuit serves as the crucial interface between a low-voltage control signal (from a microcontroller) and a high-power MOSFET. Its primary purpose is to rapidly charge and discharge the MOSFET's gate capacitance to switch it between on and off states with minimal losses.[5][6][7] A stable and well-designed driver circuit is critical for ensuring efficiency, reliability, and managing electromagnetic interference (EMI).

Key design challenges include:

-

Gate Capacitance: MOSFETs have inherent capacitances (Ciss, Coss, Crss) that must be charged and discharged quickly.[7][8] The gate driver must have low output impedance and be capable of sourcing and sinking high peak currents to achieve fast switching.

-

Switching Speed: Fast switching reduces power loss but can lead to voltage overshoot and ringing due to parasitic inductances in the circuit layout.[9] A balance must be struck between switching speed and stability.

-

Parasitic Inductances: Inductance in the PCB traces of the gate drive loop can cause voltage ringing on the gate, potentially leading to false turn-on events or exceeding the MOSFET's maximum gate-source voltage (Vgs_max).

-

Miller Effect: The gate-drain capacitance (Cgd or Crss) creates a feedback effect known as the Miller effect, which can slow down switching and cause a "Miller plateau" in the Vgs waveform.[7][8]

Critical Parameters for Gate Driver Design

Before designing the circuit, it is mandatory to extract key parameters from the power MOSFET's datasheet. These values dictate the selection of the gate driver IC and peripheral components.

| Parameter | Symbol | Example Value | Significance in Driver Design |

| Gate-Source Threshold Voltage | Vgs(th) | 3.5 V | The minimum gate voltage required to begin turning the MOSFET on. The driver's output high voltage must significantly exceed this.[7][10] |

| Total Gate Charge | Qg(tot) | 70 nC | The total charge required to turn the device on. Determines the peak current and average power the driver must supply.[10] |

| Input Capacitance | Ciss | 2500 pF | Comprises Cgs + Cgd. A primary factor in determining the required drive current for a desired switching speed.[7][8] |

| Reverse Transfer Capacitance | Crss | 150 pF | Also known as the Miller capacitance. A smaller value allows for faster switching.[8] |

| On-Resistance | Rds(on) | 15 mΩ | The resistance of the MOSFET when fully on. While not a direct driver design parameter, it is critical for calculating overall efficiency.[5][7] |

| Max Gate-Source Voltage | Vgs(max) | ±20 V | The gate driver circuit must be designed to never exceed this voltage, including any ringing or overshoot.[10] |

Core Gate Driver Circuit Topology

A common and effective gate driver configuration uses a dedicated gate driver IC placed very close to the MOSFET. This minimizes parasitic inductance in the critical gate drive loop.

Fundamental Components

-

Gate Driver IC: Provides high peak source/sink current and level shifting.

-

Decoupling Capacitor (C_VCC): A low-ESR ceramic capacitor placed as close as possible to the driver IC's VCC and GND pins. It supplies the high-frequency current pulses required to charge the MOSFET gate.

-

Gate Resistor (Rg): Controls the switching speed. A smaller Rg leads to faster switching but increases the risk of ringing and EMI. A larger Rg slows switching but improves stability.

-

Pull-down Resistor (R_pd): Ensures the MOSFET gate is held low when the driver is unpowered, preventing accidental turn-on.

Caption: A fundamental gate driver circuit topology.

Experimental Protocols for Stability Verification

To ensure the designed driver circuit is stable and efficient, rigorous testing is required. The double-pulse test is the industry-standard method for characterizing the switching performance of a power semiconductor.[11][12][13]

Protocol: Double-Pulse Test for Switching Characterization

Objective: To measure the turn-on and turn-off characteristics, including switching times, voltage overshoot, and energy losses, under controlled conditions.[11][12][13]

Methodology:

-

Circuit Setup: Assemble the half-bridge circuit as shown in the workflow diagram below. The upper MOSFET acts as a freewheeling diode, and the lower MOSFET is the Device Under Test (DUT). An inductor is used as the load.[9][11]

-

Instrumentation:

-

Use a high-bandwidth oscilloscope with appropriate voltage and current probes.

-

A function generator is required to create the double-pulse signal.[11]

-

A DC power supply provides the bus voltage.

-

-

Pulse Generation:

-

Apply a first, longer pulse to the DUT's gate driver. The duration of this pulse determines the inductor current, setting the test condition.

-

After a short off-time, apply a second, shorter pulse. The switching characteristics are measured on the rising edge (turn-on) and falling edge (turn-off) of this second pulse.[12][13]

-

-

Data Acquisition:

-

Probe the gate-source voltage (Vgs), drain-source voltage (Vds), and drain current (Id) of the DUT.

-

Capture the waveforms during the second pulse's switching transitions. Pay close attention to any ringing or overshoot.

-

-

Analysis:

Caption: Workflow for the double-pulse test protocol.

Data Presentation and Analysis

Summarizing the results from stability testing in a clear format is essential for comparison and optimization.

Table: Example Double-Pulse Test Results for Different Gate Resistors (Rg)

| Parameter | Rg = 4.7 Ω | Rg = 10 Ω | Rg = 22 Ω | Target Specification |

| Turn-on Time (t_on) | 25 ns | 45 ns | 90 ns | < 50 ns |

| Turn-off Time (t_off) | 40 ns | 70 ns | 150 ns | < 75 ns |

| Vgs Overshoot | 3.5 V (17.5%) | 1.8 V (9%) | 0.5 V (2.5%) | < 10% |

| Vds Overshoot | 65 V (16.3%) | 30 V (7.5%) | 12 V (3%) | < 10% |

| Turn-on Loss (E_on) | 150 µJ | 220 µJ | 410 µJ | As low as possible |

| Turn-off Loss (E_off) | 110 µJ | 190 µJ | 350 µJ | As low as possible |

This data demonstrates the fundamental trade-off: a lower Rg (4.7 Ω) provides fast switching and low energy loss but at the cost of significant voltage overshoot. A higher Rg (22 Ω) provides excellent stability but with much slower switching and higher losses. The 10 Ω resistor offers a balanced compromise.[9]

Troubleshooting Common Instabilities

If the experimental results show instability, a logical troubleshooting process is necessary.

Caption: A logical workflow for troubleshooting gate driver instability.

References

- 1. This compound pdf, this compound Download, this compound Description, this compound Datasheet, this compound view ::: ALLDATASHEET ::: [pdfapp.alldatasheet.com]

- 2. datasheet4u.com [datasheet4u.com]

- 3. This compound Datasheet, PDF - Alldatasheet [alldatasheet.com]

- 4. This compound Datasheet(PDF) - JIEJIE MICROELECTRONICS CO.,Ltd [alldatasheet.com]

- 5. ti.com [ti.com]

- 6. toshiba.semicon-storage.com [toshiba.semicon-storage.com]

- 7. assets.nexperia.com [assets.nexperia.com]

- 8. fscdn.rohm.com [fscdn.rohm.com]

- 9. youtube.com [youtube.com]

- 10. infineon.com [infineon.com]

- 11. tek.com [tek.com]

- 12. keysight.com [keysight.com]

- 13. matsusada.com [matsusada.com]

- 14. What Is a Double Pulse Test, and How Do You Run One in PSpice? [resources.pcb.cadence.com]

Application Notes for JX040 in High-Power Switching Circuit Designs

Disclaimer: The JX040 is a sensitive gate Silicon Controlled Rectifier (SCR), a semiconductor component used in electronic circuits for power control and switching. The intended audience for information regarding this component typically consists of electronics engineers, circuit designers, and technicians. The following application notes have been adapted to the specified format but are technical in nature and pertain to electronic circuit design, not drug development research.

Introduction to the this compound SCR

The this compound series is a family of sensitive gate Silicon Controlled Rectifiers designed for applications requiring high dv/dt capability and strong resistance to electromagnetic interference.[1][2] These characteristics make it particularly suitable for use in circuits such as residual current circuit breakers, igniters, and motor controls.[1][2] As an SCR, the this compound is a unidirectional switch that is triggered into conduction by a small gate current and remains in the "on" state as long as the current through the device is above the holding current.

Absolute Maximum Ratings and Electrical Characteristics

For reliable operation and to prevent damage to the component, the this compound must be operated within its specified absolute maximum ratings. The electrical characteristics define the performance of the device under various operating conditions.

Table 1: Absolute Maximum Ratings (Tj = 25°C unless otherwise specified)

| Parameter | Symbol | Value | Unit |

| Repetitive Peak Off-State Voltage | VDRM | 600 | V |

| Repetitive Peak Reverse Voltage | VRRM | 600 | V |

| RMS On-State Current (TC=97℃ for TO-220B) | IT(RMS) | 4 | A |

| Non-Repetitive Surge Peak On-State Current (tp=10ms) | ITSM | 30 | A |

| I²t Value for Fusing (tp=10ms) | I²t | 4.5 | A²s |

| Critical Rate of Rise of On-State Current | dI/dt | 50 | A/µs |

| Peak Gate Current (tp=20µs, Tj=110℃) | IGM | 1.2 | A |

| Peak Gate Power (tp=20µs, Tj=110℃) | PGM | 3 | W |

| Average Gate Power Dissipation (Tj=110℃) | PG(AV) | 0.2 | W |

| Storage Junction Temperature Range | Tstg | -40 to 150 | °C |

| Operating Junction Temperature Range | Tj | -40 to 110 | °C |

| Source:[2] |

Table 2: Electrical Characteristics (Tj = 25°C unless otherwise specified)

| Parameter | Symbol | Test Condition | Min. | Typ. | Max. | Unit |

| Gate Trigger Current | IGT | VD=12V, RL=33Ω | - | - | 200 | µA |

| Gate Trigger Voltage | VGT | VD=12V, RL=33Ω | - | 0.6 | 0.8 | V |

| Gate Non-Trigger Voltage | VGD | VD=VDRM, Tj=110℃ | 0.2 | - | - | V |

| Holding Current | IH | IT=0.05A | - | 5 | - | mA |

| Latching Current | IL | IG=1.2 IGT | - | 6 | - | mA |

| On-State Voltage | VTM | IT=8A, tp=380µs | - | - | 1.5 | V |

| Off-State Leakage Current | IDRM/IRRM | VD=VDRM, VR=VRRM | - | - | 5 | µA |

| Off-State Leakage Current (Tj=110℃) | IDRM/IRRM | VD=VDRM, VR=VRRM | - | - | 100 | µA |

| Critical Rate of Rise of Off-State Voltage | dV/dt | VD=2/3VDRM, Tj=110℃, RGK=1KΩ | 20 | - | - | V/µs |

| Source:[2] |

Experimental Protocols: Characterization of this compound Switching Behavior

This protocol outlines a procedure to verify the fundamental switching characteristics of the this compound SCR in a laboratory setting.

Objective:

To measure the Gate Trigger Current (IGT), Gate Trigger Voltage (VGT), and Holding Current (IH) of the this compound.

Materials:

-

This compound SCR

-

Variable DC Power Supply (for anode voltage)

-

Variable DC Current Source (for gate current)

-

Load Resistor (RL)

-

Gate Resistor (RG)

-

Digital Multimeters (3)

-

Breadboard and connecting wires

Methodology:

Part 1: Measuring Gate Trigger Current (IGT) and Gate Trigger Voltage (VGT)

-

Construct the test circuit as shown in the workflow diagram below.

-

Set the anode DC voltage supply (V_AA) to 12V.

-

Connect a multimeter in series with the gate to measure IGT and another in parallel with the gate and cathode to measure VGT.

-

Connect a third multimeter in series with the anode to monitor the anode current (I_A).

-

Slowly increase the current from the gate current source.

-

Observe the anode current. The moment the anode current suddenly increases and the SCR latches on, record the readings on the gate current and gate voltage multimeters. These are the IGT and VGT values.

-

Reduce the gate current to zero.

Part 2: Measuring Holding Current (IH)

-

With the SCR in the "on" state from the previous step, ensure the gate current is zero.

-

Slowly decrease the anode voltage supply (V_AA).

-

Monitor the anode current (I_A).

-

The value of the anode current just before the SCR turns off (i.e., the current drops to zero) is the holding current (IH). Record this value.

Experimental Workflow Diagram

Caption: Workflow for this compound SCR Characterization.

High-Power Switching Circuit Design Considerations

When designing a high-power switching circuit using the this compound, several factors must be taken into account to ensure reliable and safe operation.

-

Gate Drive Circuit: A reliable gate drive circuit is essential to ensure the SCR is triggered properly. The gate current should be sufficient to turn the device on quickly and reliably, but not so high as to exceed the maximum gate power dissipation.

-

Snubber Circuit: In applications with inductive loads, a snubber circuit (typically an RC network) across the SCR is necessary to limit the rate of rise of off-state voltage (dV/dt) and prevent false triggering.

-

Thermal Management: The this compound will dissipate power, primarily during the on-state. A heat sink is crucial to maintain the junction temperature below the maximum rating of 110°C, especially when conducting high currents.[2] The total thermal resistance from the junction to the ambient air must be low enough to dissipate the generated heat effectively.

-

Overcurrent Protection: A fast-acting fuse or circuit breaker should be included in series with the SCR to protect it from overcurrent and short-circuit conditions. The I²t rating of the protective device should be less than that of the SCR.[2]

Logical Relationship: Simplified SCR Switching Circuit

References

JX040 application in AC power control and phase angle control

It appears there has been a misunderstanding in the query. The topic "JX040 application in AC power control and phase angle control" belongs to the field of electrical engineering. However, the specified audience and the requested content, such as "signaling pathways" and "drug development professionals," are firmly in the domain of life sciences and pharmacology. These two fields are distinct and do not overlap in this context.

"AC power control" and "phase angle control" are techniques used to manage the flow of electrical energy and are not related to biological processes or drug development. Furthermore, there is no readily available information linking a component or designation "this compound" to applications in either electrical engineering or life sciences.

Given this discrepancy, it is not possible to create the requested application notes and protocols. Could you please verify the topic and the intended audience? It is possible that "this compound" is a typo for a drug or biological compound.

Application Note: Construction and Protocol for a Solid-State Relay Using the JX040 SCR for Laboratory Automation

Abstract

This application note provides a detailed protocol for the construction and verification of a custom Solid-State Relay (SSR) for switching alternating current (AC) loads. The design is centered around the JX040 sensitive gate Silicon Controlled Rectifier (SCR) and incorporates optical isolation for safe interfacing with low-voltage control logic, such as microcontrollers or data acquisition systems. SSRs offer significant advantages over traditional electromechanical relays in scientific instrumentation, including silent operation, absence of moving parts, and rapid, clean switching.[1][2] The protocol is intended for researchers and scientists who require custom hardware solutions for automating laboratory equipment, such as heaters, pumps, valves, and stirrers, where precise and reliable control of AC power is paramount.

Introduction to Solid-State Relays in a Research Context

In laboratory and drug development settings, precise control over experimental parameters is critical. Many apparatus, including thermal cyclers, incubators, peristaltic pumps, and magnetic stirrers, rely on AC mains power. A Solid-State Relay (SSR) is an electronic switching device that uses semiconductor components to switch power, providing a robust alternative to mechanical relays.[3]

The key advantages of an SSR in a scientific environment include:

-

High Reliability: The absence of moving parts eliminates mechanical wear and contact arcing, leading to a longer operational lifespan.[4]

-

Silent Operation: Lack of mechanical contacts means no audible clicking, which is beneficial in quiet laboratory environments.

-

Electrical Isolation: An optocoupler is used to create a high-impedance barrier between the low-voltage control circuit and the high-voltage AC load, ensuring the safety of sensitive control electronics and the operator.[1][5]

-

Fast Switching & Zero-Crossing Capability: SSRs can switch much faster than mechanical relays. Furthermore, specialized circuits can be designed to activate the load only when the AC voltage crosses zero, which minimizes electromagnetic interference (EMI) and current inrush, protecting both the load and the SSR.[6]

This document details the construction of a non-zero-crossing SSR, which is suitable for general-purpose resistive loads. The design utilizes the this compound SCR, a sensitive gate thyristor capable of being triggered by low-current logic.[7][8]

Component Data and Characteristics

Successful construction requires components that meet specific operational parameters. The primary components for this protocol are the this compound SCR and the MOC3021 random-phase optocoupler. Their critical electrical characteristics are summarized below.

Table 1: this compound SCR Electrical Characteristics (Tj=25℃ unless specified)

| Parameter | Symbol | Value | Unit |

|---|---|---|---|

| Repetitive Peak Off-State Voltage | VDRM / VRRM | 600 | V |

| RMS On-State Current | IT(RMS) | 4 | A |

| Non-Repetitive Surge Peak On-State Current | ITSM | 30 | A |

| Gate Trigger Current | IGT | ≤ 200 | µA |

| Gate Trigger Voltage | VGT | 0.6 (typ) / 0.8 (max) | V |

| Holding Current | IH | 5 (typ) | mA |

| Operating Junction Temperature | Tj | -40 to 110 | °C |

Data sourced from this compound Series Datasheet.[8][9]

Table 2: MOC3021 Optocoupler Electrical Characteristics (Ta=25℃)

| Parameter | Symbol | Value | Unit |

|---|---|---|---|

| LED Input Forward Voltage | VF | 1.15 (typ) | V |

| LED Input Trigger Current | IFT | 15 (max) | mA |

| Output Repetitive Peak Off-State Voltage | VDRM | 400 | V |