# Technical Support Center: JX040 Circuits & Power Dissipation

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |         |           |

|----------------------|---------|-----------|

| Compound Name:       | JX040   |           |

| Cat. No.:            | B608285 | Get Quote |

This technical support center provides troubleshooting guidance and answers to frequently asked questions regarding the reduction of power dissipation in advanced integrated circuits, with principles applicable to **JX040** series components. The information is intended for researchers, scientists, and drug development professionals who may be utilizing complex integrated circuits in their experimental setups.

## **Troubleshooting Guide**

This guide addresses specific issues that may arise during the operation of **JX040** or similar high-performance circuits.

Q1: My **JX040** circuit is overheating during prolonged experiments. What are the immediate steps to mitigate this?

A1: Overheating is a direct consequence of excessive power dissipation. Immediate actions involve reducing the workload on the circuit. If your application allows, try reducing the clock frequency of the circuit. Dynamic power, a major component of total power consumption, is directly proportional to frequency.[1][2] You can also explore if the circuit's operating voltage can be safely lowered, as dynamic power is proportional to the square of the voltage, offering significant power savings.[2][3][4] For longer-term solutions, you may need to implement more sophisticated power reduction techniques as described in the FAQs below or improve the thermal management of your experimental setup with heat sinks or active cooling.

## Troubleshooting & Optimization

Q2: The battery life of my portable device using a **JX040** circuit is shorter than expected. How can I identify the source of the high power consumption?

A2: Unexpectedly high power consumption in a battery-powered device can stem from both dynamic and static power dissipation.

- Dynamic Power: This occurs when the circuit is actively switching.[1][2] If the circuit is performing continuous, intensive computations, dynamic power will be high. Analyze your software to see if the circuit can be put into a low-power or sleep state more frequently.

- Static Power (Leakage): This is power consumed even when the circuit is idle.[1][5] In advanced, small-scale transistors, leakage power can be a significant contributor to overall consumption.[1] If the device spends a lot of time in standby, high leakage power might be the culprit.

To pinpoint the source, you will need to perform power measurements under different operating conditions (e.g., full load, idle, sleep mode) as detailed in the Experimental Protocols section.

Q3: I'm observing inconsistent performance with my **JX040** circuit when trying to implement power-saving features. Why might this be happening?

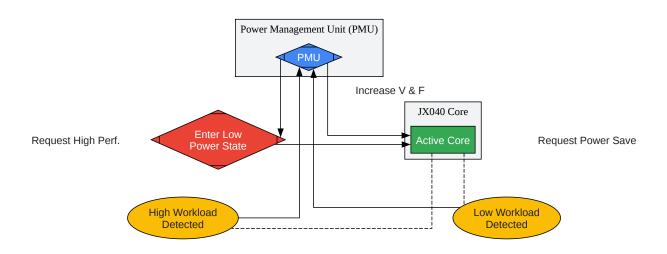

A3: Inconsistent performance when enabling power-saving features often points to issues with the implementation of techniques like Dynamic Voltage and Frequency Scaling (DVFS) or power gating.

- DVFS Instability: DVFS adjusts the circuit's voltage and frequency on the fly to match the workload.[3][6][7] If the scaling algorithm is too aggressive or not properly tuned for your application, it can lead to timing violations and computational errors when the workload suddenly increases.[2]

- Power Gating Latency: Power gating reduces leakage power by shutting off power to unused blocks of the circuit.[8][9] However, there is a "wake-up" latency associated with restoring power to these blocks.[8] If your application requires a rapid transition from an idle to an active state, this latency can manifest as performance inconsistency.

Review the control logic for your power management features to ensure they are appropriate for the performance requirements of your application.

## Frequently Asked Questions (FAQs)

What are the primary sources of power dissipation in a circuit like the **JX040**?

Power dissipation in modern CMOS circuits is broadly categorized into two types:

- Dynamic Power: This is the power consumed when transistors switch states to perform computations. It is dependent on the clock frequency, supply voltage, and the capacitance of the switching nodes.[1][2]

- Static Power (Leakage Power): This is the power consumed due to leakage currents when transistors are not switching. In advanced fabrication processes with smaller transistors, static power has become a major concern.[1][10]

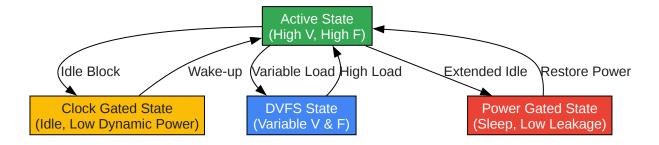

What is Clock Gating and how does it reduce power consumption?

Clock gating is a technique that reduces dynamic power by disabling the clock signal to parts of the circuit that are not in use.[1][8][11] Since the clock signal drives the switching activity of transistors, turning it off prevents unnecessary power consumption in idle circuit blocks.[5][12]

What is Power Gating and how does it differ from Clock Gating?

Power gating is a more aggressive power-saving technique that completely shuts off the power supply to inactive blocks of the circuit.[8][9] This significantly reduces static (leakage) power, which is not addressed by clock gating.[8][11] The main trade-off is the increased complexity and the time delay (wake-up latency) required to restore power and bring the block back to an operational state.[8]

What is Dynamic Voltage and Frequency Scaling (DVFS)?

DVFS is a power management technique that dynamically adjusts the operating voltage and frequency of a circuit to match the computational demands of the workload.[3][6][7] When the workload is light, DVFS lowers the voltage and frequency to save power.[6] When the workload increases, it raises them to provide higher performance.[7] This technique is highly effective because reducing the voltage has a quadratic impact on power savings.[3][4]

# **Quantitative Data on Power Reduction Techniques**

The effectiveness of various power reduction techniques can vary based on the circuit design, workload, and process technology. The following table provides a summary of typical power savings that can be achieved.

| Power Reduction<br>Technique                       | Power Component<br>Targeted | Typical Power<br>Savings                 | Key Trade-offs                                                                      |

|----------------------------------------------------|-----------------------------|------------------------------------------|-------------------------------------------------------------------------------------|

| Clock Gating                                       | Dynamic Power               | 10% - 30%                                | Increased design complexity, potential for clock skew.[11]                          |

| Power Gating                                       | Static (Leakage)<br>Power   | 50% - 90% (for the gated block)          | Wake-up latency,<br>increased area<br>overhead, design<br>complexity.[8]            |

| Dynamic Voltage and<br>Frequency Scaling<br>(DVFS) | Dynamic Power               | 27% - 47% or more                        | Performance scaling,<br>potential for instability<br>if not managed<br>properly.[6] |

| Multi-Threshold<br>CMOS (MTCMOS)                   | Static (Leakage)<br>Power   | Varies significantly with implementation | Process complexity, performance impact on critical paths.[1]                        |

# **Experimental Protocols**

Methodology for Measuring Power Dissipation

This protocol outlines the steps to accurately measure the power dissipation of a **JX040** circuit under various operating conditions.

1. Objective: To quantify the power consumption of the **JX040** circuit in different operational states (e.g., idle, full-load, specific task execution) and to evaluate the effectiveness of implemented power reduction techniques.

#### 2. Materials:

JX040 circuit mounted on a test board.

- Variable DC power supply with high-resolution voltage and current readouts.

- Digital Multimeter (DMM) or a dedicated power measurement tool (e.g., power analyzer).

- Oscilloscope to monitor clock and signal integrity.

- Workload generator (e.g., software script, function generator).

- Thermometer or thermal imaging camera to monitor circuit temperature.[13]

- 3. Procedure:

- Setup:

- Connect the DC power supply to the JX040 test board.

- Insert the DMM in series with the main power rail of the JX040 to measure the current (I).

- Connect the DMM in parallel across the power input of the **JX040** to measure the voltage (V).

- Baseline Measurement (Idle State):

- Power on the circuit with the workload generator inactive.

- Allow the circuit to stabilize for a few minutes.

- Record the voltage (V\_idle) and current (I\_idle).

- Calculate the idle power: P\_idle = V\_idle \* I\_idle.[14][15]

- Full-Load Measurement:

- Activate the workload generator to run a computationally intensive task on the JX040.

- Monitor the circuit's temperature to ensure it stays within safe operating limits.

- Record the stable voltage (V load) and current (I load).

- Calculate the full-load power: P load = V load \* I load.

- Task-Specific Measurement:

- Run a specific, repeatable task relevant to your research application.

- Measure the voltage and current during the execution of this task.

- Calculate the task-specific power consumption.

- Evaluation of Power Reduction Techniques:

- Enable a specific power reduction feature (e.g., activate clock gating, enable DVFS with a power-saving profile).

- Repeat steps 2, 3, and 4.

- Compare the power measurements with and without the power reduction technique to quantify its effectiveness.

#### 4. Data Analysis:

- Tabulate the power consumption values for each operational state and with different powersaving configurations.

- Calculate the percentage of power reduction achieved by each technique.

- Correlate power consumption with circuit temperature.

## **Visualizations**

#### Click to download full resolution via product page

Caption: Signaling pathway for DVFS and power state transitions.

Click to download full resolution via product page

Caption: Experimental workflow for power dissipation measurement.

Click to download full resolution via product page

Caption: Logical relationships between different power states.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. mckinsey-electronics.com [mckinsey-electronics.com]

- 2. medium.com [medium.com]

- 3. fiveable.me [fiveable.me]

- 4. usenix.org [usenix.org]

- 5. medium.com [medium.com]

- 6. mdpi.com [mdpi.com]

- 7. techtarget.com [techtarget.com]

- 8. fiveable.me [fiveable.me]

- 9. Power gating Wikipedia [en.wikipedia.org]

- 10. Understanding Power Consumption and Reduction Techniques [allpcb.com]

- 11. The Ultimate Guide to Clock Gating AnySilicon [anysilicon.com]

- 12. 10 Tips for Saving SoC Power Consumption AnySilicon [anysilicon.com]

- 13. allaboutcircuits.com [allaboutcircuits.com]

- 14. youtube.com [youtube.com]

- 15. Basics: Power dissipation and electronic components | Evil Mad Scientist Laboratories [evilmadscientist.com]

- To cite this document: BenchChem. [Technical Support Center: JX040 Circuits & Power Dissipation]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b608285#techniques-for-reducing-power-dissipation-in-jx040-circuits]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com