# An In-depth Technical Guide to the JX040 Sensitive Gate Silicon Controlled Rectifier

Author: BenchChem Technical Support Team. Date: December 2025

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides a detailed examination of the **JX040**, a sensitive gate silicon controlled rectifier (SCR). The content delves into the physical construction, semiconductor layers, and fabrication processes typical for a device of this class. Furthermore, it outlines comprehensive experimental protocols for the characterization of its electrical and thermal properties, and presents key performance data for the **JX040**.

## **Physical Construction and Semiconductor Layers**

The **JX040**, like other silicon controlled rectifiers, is a four-layer semiconductor device with a P-N-P-N structure. This construction forms three P-N junctions in series. The device has three terminals: an anode, a cathode, and a gate, which serves as the control input.

The functionality of the SCR is dictated by the doping concentrations and thicknesses of its constituent semiconductor layers. While specific proprietary data for the **JX040** is not publicly available, the following table summarizes the typical layer characteristics for a sensitive gate SCR. The cathode is the most heavily doped layer, while the central N-type layer is the thickest and most lightly doped to support a high blocking voltage.

| Layer          | Туре | Typical Doping<br>Concentration<br>(atoms/cm³) | Typical Thickness<br>(μm) |

|----------------|------|------------------------------------------------|---------------------------|

| Anode          | P+   | 10 <sup>19</sup> - 10 <sup>20</sup>            | 30 - 50                   |

| Blocking Layer | N-   | 1013 - 1014                                    | 50 - 200                  |

| Gate           | Р    | 10 <sup>16</sup> - 10 <sup>17</sup>            | 10 - 20                   |

| Cathode        | N+   | > 10 <sup>20</sup>                             | 5 - 15                    |

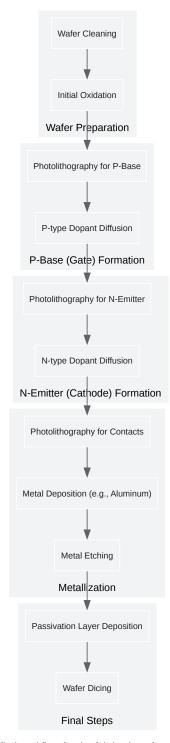

## **Fabrication Workflow**

The fabrication of a sensitive gate SCR such as the **JX040** involves a series of sophisticated processes to create the multi-layer P-N-P-N structure with high precision. The following diagram illustrates a typical fabrication workflow, primarily involving photolithography and diffusion processes.

Figure 1: A simplified workflow for the fabrication of a sensitive gate SCR.

Click to download full resolution via product page

Caption: A simplified workflow for the fabrication of a sensitive gate SCR.

## **Electrical and Thermal Characteristics of the JX040**

The following tables summarize the key electrical and thermal performance parameters of the **JX040** series sensitive gate SCRs, as specified in their datasheets.[1][2][3]

### **Absolute Maximum Ratings**

| Parameter                             | Symbol    | Value      | Unit |

|---------------------------------------|-----------|------------|------|

| Repetitive Peak Off-<br>State Voltage | VDRM/VRRM | 600        | V    |

| RMS On-State<br>Current               | IT(RMS)   | 4          | A    |

| Peak Gate Power (tp=20μs)             | PGM       | 5          | W    |

| Average Gate Power Dissipation        | PG(AV)    | 0.5        | W    |

| Operating Junction Temperature Range  | Tj        | -40 to 125 | °C   |

| Storage Temperature<br>Range          | Tstg      | -40 to 150 | °C   |

Electrical Characteristics (Tj = 25°C unless otherwise specified)

| Paramete<br>r                               | Symbol | Test<br>Condition                | Min. | Тур. | Max. | Unit |

|---------------------------------------------|--------|----------------------------------|------|------|------|------|

| Gate<br>Trigger<br>Current                  | IGT    | VD=12V,<br>RL=33Ω                | -    | 50   | 200  | μΑ   |

| Gate<br>Trigger<br>Voltage                  | VGT    | VD=12V,<br>RL=33Ω                | -    | 0.6  | 0.8  | V    |

| Holding<br>Current                          | IH     | IT=0.05A                         | -    | -    | 5    | mA   |

| Latching<br>Current                         | IL     | IG=1.2 IGT                       | -    | -    | 6    | mA   |

| On-State<br>Voltage                         | VTM    | IT=8A,<br>tp=380μs               | -    | -    | 1.6  | V    |

| Critical Rate of Rise of Off- State Voltage | dV/dt  | VD=400V,<br>Tj=125°C,<br>RGK=1kΩ | 50   | -    | -    | V/μs |

#### Thermal Resistances

| Parameter           | Symbol   | Value | Unit |

|---------------------|----------|-------|------|

| Junction to Case    | Rth(j-c) | 3.5   | °C/W |

| Junction to Ambient | Rth(j-a) | 100   | °C/W |

## **Experimental Protocols**

Electrical Characterization: V-I Characteristics, Latching Current, and Holding Current

Objective: To determine the voltage-current (V-I) characteristics of the **JX040** SCR and to measure its latching and holding currents.

#### Equipment:

- Variable DC power supply (for anode-cathode circuit)

- Variable DC power supply (for gate circuit)

- Digital multimeters (2)

- Resistors (as per test conditions)

- JX040 SCR device under test (DUT)

#### Procedure:

- V-I Characteristics:

- Construct the test circuit with the anode and cathode of the SCR connected to the main power supply through a load resistor.

- 2. Connect the gate and cathode to the second power supply through a current-limiting resistor.

- 3. With the gate circuit open, gradually increase the anode-to-cathode voltage (Vak) and measure the anode current (Ia). This will trace the forward blocking region.

- 4. Apply a small gate current (e.g.,  $50~\mu A$ ) and repeat the previous step. Observe the lower breakover voltage.

- 5. Once the SCR is triggered, vary the load resistor to obtain different values of la and measure the corresponding Vak to trace the forward conduction region.

- Latching Current (IL):

- 1. With the SCR in the off-state, apply a gate pulse to turn it on.

- 2. Immediately after triggering, remove the gate signal.

- The minimum anode current required to keep the SCR in the on-state is the latching current.

- · Holding Current (IH):

- With the SCR in the on-state, gradually decrease the anode current by increasing the load resistance.

- 2. The value of the anode current just before the SCR switches to the off-state is the holding current.

## **Thermal Characterization: Transient Thermal Analysis**

Objective: To analyze the transient thermal behavior of the **JX040** under pulsed power conditions.

#### Equipment:

- High-current pulse generator

- Infrared (IR) thermal camera

- Thermocouples

- · Data acquisition system

- Test fixture with appropriate heat sinking for the JX040

#### Procedure:

- Mount the JX040 on the test fixture, ensuring good thermal contact with the heat sink.

- Attach thermocouples to the case of the device to monitor its temperature.

- Position the IR thermal camera to have a clear view of the device package.

- Apply single or repetitive high-current pulses to the SCR.

- Simultaneously record the temperature of the device case using the thermocouples and the temperature distribution on the package surface using the IR camera.

- Analyze the recorded data to determine the transient thermal impedance and the rate of temperature rise under different pulse conditions. This data is crucial for establishing the safe operating area (SOA) of the device.

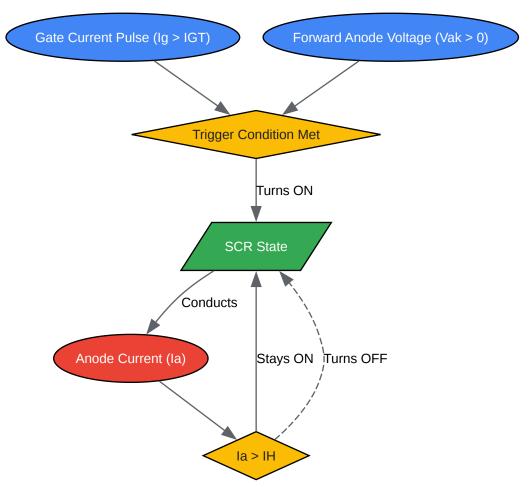

## **Signaling and Control**

The fundamental control mechanism of the **JX040** is the application of a current pulse to the gate terminal. The following diagram illustrates the logical relationship between the gate signal and the state of the SCR.

Figure 2: Logical control diagram for an SCR.

Click to download full resolution via product page

Caption: Logical control diagram for an SCR.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. surgecomponents.com [surgecomponents.com]

- 2. jjm.com [jjm.com]

- 3. jjm.com [jjm.com]

- To cite this document: BenchChem. [An In-depth Technical Guide to the JX040 Sensitive Gate Silicon Controlled Rectifier]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b608285#physical-construction-and-semiconductor-layers-of-the-jx040]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com