TES pentacene

Description

BenchChem offers high-quality TES pentacene suitable for many research applications. Different packaging options are available to accommodate customers' requirements. Please inquire for more information about TES pentacene including the price, delivery time, and more detailed information at info@benchchem.com.

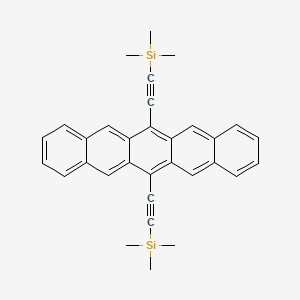

Structure

3D Structure

Properties

IUPAC Name |

trimethyl-[2-[13-(2-trimethylsilylethynyl)pentacen-6-yl]ethynyl]silane | |

|---|---|---|

| Details | Computed by Lexichem TK 2.7.0 (PubChem release 2021.05.07) | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

InChI |

InChI=1S/C32H30Si2/c1-33(2,3)17-15-27-29-19-23-11-7-9-13-25(23)21-31(29)28(16-18-34(4,5)6)32-22-26-14-10-8-12-24(26)20-30(27)32/h7-14,19-22H,1-6H3 | |

| Details | Computed by InChI 1.0.6 (PubChem release 2021.05.07) | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

InChI Key |

MYKQRRZJBVVBMU-UHFFFAOYSA-N | |

| Details | Computed by InChI 1.0.6 (PubChem release 2021.05.07) | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Canonical SMILES |

C[Si](C)(C)C#CC1=C2C=C3C=CC=CC3=CC2=C(C4=CC5=CC=CC=C5C=C41)C#C[Si](C)(C)C | |

| Details | Computed by OEChem 2.3.0 (PubChem release 2021.05.07) | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Molecular Formula |

C32H30Si2 | |

| Details | Computed by PubChem 2.1 (PubChem release 2021.05.07) | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Molecular Weight |

470.7 g/mol | |

| Details | Computed by PubChem 2.1 (PubChem release 2021.05.07) | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

CAS No. |

398128-81-9 | |

| Record name | 398128-81-9 | |

| Source | European Chemicals Agency (ECHA) | |

| URL | https://echa.europa.eu/information-on-chemicals | |

| Description | The European Chemicals Agency (ECHA) is an agency of the European Union which is the driving force among regulatory authorities in implementing the EU's groundbreaking chemicals legislation for the benefit of human health and the environment as well as for innovation and competitiveness. | |

| Explanation | Use of the information, documents and data from the ECHA website is subject to the terms and conditions of this Legal Notice, and subject to other binding limitations provided for under applicable law, the information, documents and data made available on the ECHA website may be reproduced, distributed and/or used, totally or in part, for non-commercial purposes provided that ECHA is acknowledged as the source: "Source: European Chemicals Agency, http://echa.europa.eu/". Such acknowledgement must be included in each copy of the material. ECHA permits and encourages organisations and individuals to create links to the ECHA website under the following cumulative conditions: Links can only be made to webpages that provide a link to the Legal Notice page. | |

Foundational & Exploratory

molecular structure and packing of TES pentacene

An In-Depth Technical Guide to the Molecular Structure and Packing of TES Pentacene

Authored by a Senior Application Scientist

Introduction: Overcoming the Limitations of Pentacene through Silylethynyl Functionalization

Pentacene, a polycyclic aromatic hydrocarbon comprising five linearly-fused benzene rings, has long been a benchmark material in the field of organic electronics.[1][2][3] Its rigid, planar structure and extensive π-conjugation provide excellent charge transport properties, making it a cornerstone for research in organic thin-film transistors (OTFTs). However, pristine pentacene suffers from significant drawbacks that limit its practical application: extremely low solubility in common organic solvents and instability in ambient air and light.[3][4][5] These limitations historically restricted its deposition to expensive and difficult-to-scale vacuum-based techniques.[4][5]

To unlock the potential of pentacene for low-cost, large-area electronics via solution processing, chemical modification has become a critical strategy. Functionalizing the pentacene core with bulky side groups enhances solubility and can improve stability. A particularly successful approach has been the introduction of silylethynyl groups. This guide focuses on 6,13-bis(triethylsilylethynyl)pentacene (TES pentacene), a derivative that offers a compelling balance of solution processability and high performance.[5] We will explore its molecular architecture, the resulting solid-state packing arrangements (polymorphism), and the experimental methodologies used to control and characterize its thin films.

The TES Pentacene Molecule: A Structural Overview

The defining feature of TES pentacene is the covalent attachment of two triethylsilylethynyl ((C2H5)3SiC≡C–) groups at the 6 and 13 positions of the central pentacene ring. These positions are the most reactive on the acene backbone, and their functionalization enhances the molecule's stability.

The TES side groups serve two primary functions. First, the bulky, three-dimensional nature of the triethylsilyl moieties disrupts the strong intermolecular forces that make pristine pentacene insoluble, thereby allowing it to be dissolved in common organic solvents like toluene and chloroform.[7] Second, the ethynyl spacer keeps the bulky silyl groups away from the aromatic core, which allows for favorable π-π stacking between adjacent molecules—a critical interaction for efficient charge transport.[8]

Caption: Chemical structure of 6,13-bis(triethylsilylethynyl)pentacene (TES Pentacene).

Crystalline Polymorphism and Molecular Packing

The way organic semiconductor molecules arrange themselves in the solid state—their crystal packing—profoundly impacts the material's electronic properties.[9][10] Many organic materials, including pentacene and its derivatives, are polymorphic, meaning they can crystallize into multiple distinct structures, or polymorphs.[11][12][13][14] Each polymorph has a unique unit cell and molecular arrangement, leading to different degrees of intermolecular electronic coupling and, consequently, different charge carrier mobilities.[10][11]

Pristine pentacene typically adopts a "herringbone" packing motif.[15] In this arrangement, adjacent molecules are tilted with respect to one another, which is not optimal for charge transport along the stacking direction. The bulky silylethynyl side groups in TES pentacene and its close analog, TIPS pentacene, fundamentally alter this packing. They frustrate the edge-to-face herringbone arrangement and promote a more two-dimensional bricklayer or "slip-stacked" π-stacking motif.[8] This cofacial arrangement significantly increases the orbital overlap between adjacent pentacene cores, creating more efficient pathways for charge transport.

Pentacene thin films are known to exhibit at least two major types of polymorphs: a "thin-film" phase and a "bulk" phase.[12][16][17] The thin-film phase often forms first on the substrate, while the bulk phase, which is thermodynamically more stable, may appear in thicker films or after annealing.[12][14] These phases are distinguished by their interlayer spacing (d(001)-spacing), which can be readily measured using X-ray diffraction.[11][13][18][19]

| Pentacene Polymorph Type | Typical d(001) Spacing (Å) | Notes |

| Thin-Film Phase | ~15.4 | Often observed in the initial layers of vacuum-deposited films.[16][17][18] |

| Bulk Phase (Single Crystal) | ~14.1 - 14.5 | Thermodynamically more stable; found in single crystals and thicker films.[13][18] |

Note: The exact d-spacing values for TES pentacene can vary depending on processing conditions. The values presented are for the parent pentacene compound and serve as a reference.

Caption: Influence of TES functionalization on molecular packing motifs.

Experimental Section: Thin Film Deposition and Characterization

Controlling the crystallization and morphology of TES pentacene films is paramount to achieving high-performance electronic devices. Solution-based methods are particularly attractive for their potential in low-cost, large-area manufacturing.

Thin Film Deposition Protocols

A. Spin Coating

Spin coating is a rapid and widely used technique for producing uniform thin films from solution.[20][21] A solution of the material is dispensed onto a substrate, which is then spun at high speed. Centrifugal force spreads the liquid, and solvent evaporation leaves behind a solid film.[20]

Causality Behind Choices: The final film thickness and morphology are governed by a balance of forces: centrifugal force, which thins the film, and solvent evaporation, which increases viscosity and "freezes" the structure.[21] The choice of solvent is critical; its volatility affects the drying time and thus the time available for molecular self-organization. Higher boiling point solvents (e.g., dichlorobenzene) allow more time for crystallization, often leading to larger crystalline domains.[22]

Self-Validating Protocol: Spin Coating TES Pentacene

-

Solution Preparation: Dissolve TES pentacene in a suitable solvent (e.g., toluene, chloroform) to a concentration of 5-10 mg/mL. Gentle heating (e.g., 60 °C) may be required to ensure complete dissolution.[2] Filter the solution through a 0.2 µm PTFE syringe filter to remove particulates.

-

Substrate Preparation: Use silicon wafers with a thermally grown SiO2 dielectric layer. Clean the substrates sequentially in ultrasonic baths of deionized water, acetone, and isopropanol. Treat the SiO2 surface with a self-assembled monolayer (SAM) like octadecyltrichlorosilane (OTS) to improve surface energy matching and promote ordered molecular growth.[23]

-

Deposition: Place the substrate on the spin coater chuck. Dispense a controlled volume of the TES pentacene solution to cover the center of the substrate.

-

Spinning: Accelerate to a target speed (e.g., 1000-3000 rpm) and hold for a set duration (e.g., 60 seconds).[2][23] The process should ideally be performed in an inert atmosphere (e.g., a nitrogen-filled glovebox) to minimize solvent contamination and oxidation.

-

Annealing: Transfer the coated substrate to a hotplate and anneal at a moderate temperature (e.g., 80-120 °C) for 10-30 minutes to remove residual solvent and improve crystallinity.[2]

B. Solution Shearing

Solution shearing is an advanced deposition technique designed to produce highly crystalline, large-area films with aligned domains.[24][25] A small volume of solution is confined between a stationary heated substrate and a moving "shearing blade." As the blade moves at a constant velocity, a thin film of solution is left behind, and the controlled evaporation at the meniscus leads to directional crystallization.[24]

Causality Behind Choices: This method decouples the coating and drying steps, offering greater control over crystallization dynamics compared to spin coating. The substrate temperature controls the solvent evaporation rate, while the shearing speed influences the fluid dynamics and the resulting film thickness. The lyophobic/lyophilic patterning of the blade and substrate can be used to precisely control nucleation and crystal growth.[24]

Self-Validating Protocol: Solution Shearing of TES Pentacene

-

Solution Preparation: Prepare an 8-10 mg/mL solution of TES pentacene in a high-boiling-point solvent like toluene. Heat to 60-90 °C to ensure full dissolution.[24]

-

Apparatus Setup: Place the prepared substrate on a heated stage set to the desired deposition temperature (e.g., 90 °C). Position a shearing blade (e.g., an OTS-coated silicon wafer) at a small angle (~5-10°) and a fixed gap (~100 µm) above the substrate.[24]

-

Deposition: Inject the hot TES pentacene solution into the gap between the blade and the substrate.

-

Shearing: Move the blade across the substrate at a constant, slow speed (e.g., 0.1-1.0 mm/s) using a motorized stage.

-

Annealing: Allow the film to anneal on the heated stage for 1-2 minutes post-deposition to ensure complete solvent removal.[24]

Structural and Morphological Characterization

Once films are deposited, their structure and surface morphology must be analyzed to correlate the processing conditions with the material properties.

Caption: General experimental workflow for TES Pentacene thin film preparation and analysis.

-

X-Ray Diffraction (XRD): This is the primary technique for identifying crystalline polymorphs. In an out-of-plane measurement, sharp diffraction peaks corresponding to the (00l) lattice planes indicate that the molecules are well-ordered with their c-axis oriented perpendicular to the substrate.[16][26] The position of these peaks allows for the direct calculation of the interlayer d-spacing, enabling differentiation between thin-film and bulk phases.[16][27]

-

Atomic Force Microscopy (AFM): AFM provides high-resolution topographical images of the film's surface.[28] It is used to visualize the size and shape of crystalline grains, identify the presence of grain boundaries, and quantify surface roughness.[29][30] A film with large, well-interconnected grains is desirable, as grain boundaries can act as traps or barriers for charge carriers, impeding device performance.[31][32]

-

Polarized Optical Microscopy (POM): POM is a valuable tool for visualizing crystalline domains over large areas (microns to millimeters).[22][33] Because crystalline organic films are birefringent, they appear bright against a dark background under crossed polarizers. This allows for rapid assessment of crystal size, morphology (e.g., dendritic or ribbon-like), and orientation.[1][34][35]

Conclusion: Linking Structure to Function

The performance of a TES pentacene-based device is a direct consequence of its solid-state structure. The functionalization of the pentacene core with TES groups is a deliberate chemical design choice that enhances solubility and crucially promotes a π-stacked molecular packing arrangement that is favorable for charge transport. Advanced deposition techniques like solution shearing provide the experimental control needed to guide this self-assembly process, yielding highly ordered films with large, aligned crystalline domains.

By employing a suite of characterization techniques—XRD to confirm the desired polymorph, AFM to visualize the grain structure, and POM to assess large-area morphology—researchers can establish clear structure-property relationships. A film characterized by a well-defined π-stacked polymorph, large and well-connected grains, and minimal defects is primed to deliver superior electronic performance. This in-depth understanding of the interplay between molecular design, processing, and solid-state structure is essential for the continued development of high-performance, solution-processable organic electronics.

References

-

ResearchGate. Polarized optical microscopy images of TIPS‐pentacene/PMMA a) and PαMS.... Available at: [Link].

-

Giri, G., Verploegen, E., Mannsfeld, S. C. B., Atahan-Evrenk, S., Kim, D. H., Lee, S. S., ... & Bao, Z. (2014). Selective solution shearing deposition of high performance TIPS-pentacene polymorphs through chemical patterning. Journal of Materials Research, 29(21), 2563-2572. Available at: [Link].

-

ResearchGate. (a) Polarized optical microscopy images of TIPS-pentacene deposits on.... Available at: [Link].

-

Lim, J. A., Lee, W. H., Lee, H. S., Lee, J. H., Park, Y. D., & Cho, K. (2022). Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance. Polymers, 14(6), 1159. Available at: [Link].

-

ResearchGate. Polarized optical microscopy images of a–b pristine TIPS pentacene film.... Available at: [Link].

-

Lim, J. A., Lee, W. H., Lee, H. S., Lee, J. H., Park, Y. D., & Cho, K. (2022). Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance. MDPI. Available at: [Link].

-

ResearchGate. a–c Polarized optical images of TIPS pentacene crystalline films based.... Available at: [Link].

-

Al-Asbahi, B. A., Al-Ghamdi, A. A., Al-Hartomy, O. A., El-Tantawy, F., Yakuphanoglu, F., & Al-Hazmi, F. (2020). Structural and Optical Properties of TIPS Pentacene Thin Film Exposed to Gamma Radiation. Journal of Ovonic Research, 16(5), 265-272. Available at: [Link].

-

Anta, F., El Hdiy, A., Farkhsi, A., Kanimozhi, C., Almogren, A., Harrach, D., ... & Anthopoulos, T. D. (2012). Atomic force microscopy analysis of morphology of thin pentacene films deposited on parylene-C and benzocyclobutene. Applied Surface Science, 258(22), 8882-8888. Available at: [Link].

-

Encyclopedia.pub. (2022). Pentacene and Its Derivatives Deposition Methods. Available at: [Link].

-

ResearchGate. Pentacene Active Channel Layers Prepared by Spin-Coating and Vacuum Evaporation Using Soluble Precursors for OFET Applications. Available at: [Link].

-

ResearchGate. AFM images showing the surface morphology of pentacene/glass and.... Available at: [Link].

-

ResearchGate. Polarized optical images of a–c TIPS pentacene films and d–g TIPS.... Available at: [Link].

-

Chemsrc. TES pentacene | CAS#:398128-81-9. Available at: [Link].

-

Subramanian, V. (2009). Thin Film Formation of a Solution Processed Pentacene. UC Berkeley EECS. Available at: [Link].

-

ResearchGate. Identification of polymorphs of pentacene | Request PDF. Available at: [Link].

-

ResearchGate. Exploring the polymorphism of crystalline pentacene | Request PDF. Available at: [Link].

-

Lirias. Pentacene devices and logic gates fabricated by organic vapor phase deposition. Available at: [Link].

-

R Discovery. Crystal and electronic structures of pentacene thin films from grazing-incidence x-ray diffraction and first-principles calculations. Available at: [Link].

-

ResearchGate. (a) Band structure of the 'bulk' polymorph of pentacene, as reported by.... Available at: [Link].

-

ResearchGate. Pentacene devices and logic gates fabricated by organic vapor phase deposition. Available at: [Link].

-

ResearchGate. Atomic force microscopy topography of a complete coverage of pentacene.... Available at: [Link].

-

Spectroscopy Online. (2009). A Picture of Pentacene. Available at: [Link].

-

ResearchGate. Atomic Force Microscopy (AFM) images of Pentacene evaporated on (a) SU8, (b) PMMA and (c) PVP. (d) A schematic diagram of the memory devices structure.. Available at: [Link].

-

ResearchGate. (PDF) Charge transport mechanism and stability in pentacene thin-film transistors. Available at: [Link].

-

Mattheus, C. C., Dros, A. B., Baas, J., Meetsma, A., de Boer, J. L., & Palstra, T. T. (2001). Polymorphism in pentacene. Acta Crystallographica Section C: Crystal Structure Communications, 57(Pt 8), 939–941. Available at: [Link].

-

Lirias. Growth of pentacene thin films by in-line organic vapor phase deposition. Available at: [Link].

-

Wikipedia. Pentacene. Available at: [Link].

-

ResearchGate. Controlling Polymorphic Transformations of Pentacene Crystal through Solvent Treatments: An Experimental and Theoretical Study | Request PDF. Available at: [Link].

-

ResearchGate. Solution-sheared single-crystalline TIPS-pentacene thin film..... Available at: [Link].

-

ResearchGate. Charge transport and morphology of pentacene films confined in nano-patterned region. Available at: [Link].

-

Mattheus, C. C., Dros, A. B., Baas, J., Meetsma, A., de Boer, J. L., & Palstra, T. T. (2002). Identification of polymorphs of pentacene. arXiv. Available at: [Link].

-

HZB. Pentacene growth on graphene by in situ GISAXS and GIWAXS. Available at: [Link].

-

Girlando, A., Grisanti, L., & Della Valle, R. G. (2012). Raman Identification of Polymorphs in Pentacene Films. Materials, 5(7), 1233-1243. Available at: [Link].

-

ResearchGate. Temperature gradient controlled crystal growth from TIPS pentacene-poly(α-methyl styrene) blends for improving performance of organic thin film transistors | Request PDF. Available at: [Link].

-

ResearchGate. X-ray diffraction pattern of the pentacene thin films fabricated on Si (111) substrate.. Available at: [Link].

-

Stanford Synchrotron Radiation Lightsource. (2009). Structure of Pentacene Monolayers on Amorphous Silicon Oxide and Relation to Charge Transport. Available at: [Link].

-

University of Groningen. (2003). Identification of polymorphs of pentacene. Available at: [Link].

-

Techno Press. A comprehensive study of spin coating as a thin film deposition technique and spin coating equipment. Available at: [Link].

-

Fraboni, B., et al. (2023). Polymorph Screening and Investigation of Charge Transport of ditBuC6-BTBT. Advanced Electronic Materials. Available at: [Link].

-

Beilstein-Institut. The charge transport properties of dicyanomethylene-functionalised violanthrone derivatives. Available at: [Link].

Sources

- 1. researchgate.net [researchgate.net]

- 2. mdpi.com [mdpi.com]

- 3. Pentacene - Wikipedia [en.wikipedia.org]

- 4. Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance - PMC [pmc.ncbi.nlm.nih.gov]

- 5. encyclopedia.pub [encyclopedia.pub]

- 6. TES pentacene | 398128-81-9 [chemicalbook.com]

- 7. ossila.com [ossila.com]

- 8. ossila.com [ossila.com]

- 9. researchgate.net [researchgate.net]

- 10. Polymorph Screening and Investigation of Charge Transport of ditBuC6-BTBT - PMC [pmc.ncbi.nlm.nih.gov]

- 11. researchgate.net [researchgate.net]

- 12. researchgate.net [researchgate.net]

- 13. Polymorphism in pentacene - PubMed [pubmed.ncbi.nlm.nih.gov]

- 14. researchgate.net [researchgate.net]

- 15. Structure of Pentacene Monolayers on Amorphous Silicon Oxide and Relation to Charge Transport | Stanford Synchrotron Radiation Lightsource [www-ssrl.slac.stanford.edu]

- 16. rigaku.com [rigaku.com]

- 17. mdpi.com [mdpi.com]

- 18. [cond-mat/0210228] Identification of polymorphs of pentacene [arxiv.org]

- 19. research.rug.nl [research.rug.nl]

- 20. ossila.com [ossila.com]

- 21. techno-press.org [techno-press.org]

- 22. researchgate.net [researchgate.net]

- 23. BJOC - The charge transport properties of dicyanomethylene-functionalised violanthrone derivatives [beilstein-journals.org]

- 24. Selective solution shearing deposition of high performance TIPS-pentacene polymorphs through chemical patterning | Journal of Materials Research | Cambridge Core [cambridge.org]

- 25. researchgate.net [researchgate.net]

- 26. scielo.br [scielo.br]

- 27. researchgate.net [researchgate.net]

- 28. researchgate.net [researchgate.net]

- 29. researchgate.net [researchgate.net]

- 30. researchgate.net [researchgate.net]

- 31. researchgate.net [researchgate.net]

- 32. researchgate.net [researchgate.net]

- 33. researchgate.net [researchgate.net]

- 34. researchgate.net [researchgate.net]

- 35. researchgate.net [researchgate.net]

A Comprehensive Technical Guide to the Thermal Properties of 6,13-Bis(triisopropylsilylethynyl) Pentacene (TIPS-Pentacene)

For Researchers, Scientists, and Drug Development Professionals

Foreword

6,13-Bis(triisopropylsilylethynyl) pentacene, commonly known as TIPS-pentacene, stands as a benchmark organic semiconductor. Its remarkable combination of high charge carrier mobility, environmental stability, and solution processability has positioned it at the forefront of research in organic electronics. The performance and long-term stability of TIPS-pentacene-based devices are inextricably linked to its thermal properties. This guide provides an in-depth exploration of the thermal behavior of TIPS-pentacene, offering a crucial resource for researchers and engineers working to optimize its application in next-generation electronics.

The Critical Role of Thermal Properties in Organic Electronics

The thermal stability and phase transitions of organic semiconductors are paramount for the operational reliability and performance of devices such as organic field-effect transistors (OFETs) and organic photovoltaics (OPVs). For TIPS-pentacene, understanding its response to thermal stimuli is essential for controlling thin-film morphology, which in turn dictates charge transport characteristics. Key thermal parameters, including decomposition temperature, melting point, glass transition, and polymorphic phase transitions, directly influence manufacturing processes and the ultimate device lifetime.

Thermal Stability Assessment: Thermogravimetric Analysis (TGA)

Thermogravimetric Analysis (TGA) is a fundamental technique used to determine the thermal stability of a material by measuring its mass change as a function of temperature.

Insights from TGA of TIPS-Pentacene

TGA reveals that TIPS-pentacene is a thermally robust organic semiconductor. It exhibits high thermal stability, with decomposition commencing at approximately 412 °C.[1][2] This high decomposition temperature is advantageous for device fabrication, as it allows for a wide processing window for techniques such as thermal annealing without the risk of material degradation. The stability can be attributed to the protective triisopropylsilyl (TIPS) side groups, which shield the pentacene core.[3]

Experimental Protocol: Thermogravimetric Analysis

A standardized TGA protocol for analyzing TIPS-pentacene is outlined below:

-

Sample Preparation: A small quantity of TIPS-pentacene powder (typically 5-10 mg) is placed in a clean, tared TGA crucible (e.g., alumina or platinum).

-

Instrument Setup: The TGA instrument is purged with an inert gas, such as nitrogen, at a constant flow rate (e.g., 20-50 mL/min) to prevent oxidative degradation.

-

Temperature Program: The sample is heated from ambient temperature to a final temperature above the expected decomposition point (e.g., 600 °C) at a controlled heating rate (e.g., 10 °C/min).

-

Data Analysis: The resulting TGA curve, plotting mass percentage versus temperature, is analyzed to determine the onset of decomposition, which is typically defined as the temperature at which a 5% mass loss occurs.

The Interplay of Thermal Annealing, Morphology, and Device Performance

Thermal annealing is a critical post-deposition step in the fabrication of TIPS-pentacene thin-film transistors. The annealing temperature has a significant influence on the crystalline structure and morphology of the film, which in turn dictates the charge transport properties.

Causal Relationship between Annealing and Performance

Annealing TIPS-pentacene films at temperatures above the solid-state phase transition (i.e., > 127 °C) can induce a transformation to a more ordered crystalline polymorph with improved π-π stacking. [4]This enhanced molecular ordering facilitates more efficient charge transport, leading to higher charge carrier mobilities in OFETs. [5][6]However, the choice of annealing temperature is a delicate balance, as excessive temperatures can lead to film dewetting or the formation of defects. The solvent used for film deposition also plays a crucial role, as its boiling point influences the crystallization dynamics during annealing.

Molecular Packing of TIPS-Pentacene

The arrangement of TIPS-pentacene molecules in the solid state is crucial for its electronic properties. The molecules typically adopt a "brickwork" packing motif, which facilitates two-dimensional charge transport. The TIPS side groups play a vital role in mediating the intermolecular spacing and preventing the herringbone packing characteristic of unsubstituted pentacene.

Conclusion and Future Outlook

The thermal properties of TIPS-pentacene are a cornerstone of its utility as a high-performance organic semiconductor. A thorough understanding of its thermal stability, melting behavior, and polymorphic transitions is indispensable for the rational design and fabrication of efficient and reliable organic electronic devices. Future research should focus on in-situ characterization techniques to further elucidate the kinetics of polymorphic transformations during thermal processing. Moreover, a deeper understanding of the interplay between molecular design, thermal properties, and device performance will pave the way for the next generation of solution-processable organic semiconductors.

References

-

Khan, M. A., et al. (2016). Thermal and Optical Properties of 6, 13-Bis (tri-isopropylsilylethynyl) TIPS-pentacene. Journal of Ovonic Research, 12(1), 27-33. [Link]

-

Anthony, J. E. (2006). Functionalized Pentacene: Improved Electronic Properties from Control of Solid-State Order. Chemistry of Materials, 18(3), 517-527. [Link]

-

Diao, Y., et al. (2014). Thermally Induced Solid-State Phase Transition of Bis(triisopropylsilylethynyl) Pentacene Crystals. The Journal of Physical Chemistry B, 118(31), 9473-9481. [Link]

-

Giri, G., et al. (2014). Understanding Polymorphism in Organic Semiconductor Thin Films through Nanoconfinement. Journal of the American Chemical Society, 136(48), 16904-16914. [Link]

-

Khan, M. A., et al. (2017). Structural, Optical, Electrochemical, Thermal and Electrical Properties of 6, 13-Bis (tri-isopropylsilylethynyl) TIPS-pentacene. Chalcogenide Letters, 14(5), 195-204. [Link]

-

Kadri, D. A., et al. (2018). Optimization of 6,13Bis(triisopropylsilylethynyl)pentacene (TIPS-Pentacene) Organic Field Effect Transistor: Annealing Temperature and Solvent Effects. Materials Sciences and Applications, 9(11), 900-912. [Link]

-

Lim, Y. F., et al. (2005). Effect of annealing on the mobility and morphology of thermally activated pentacene thin film transistors. Journal of Applied Physics, 99(9), 094503. [Link]

-

Kadri, D. A., et al. (2018). Optimization of 6,13Bis(triisopropylsilylethynyl)pentacene (TIPS-Pentacene) Organic Field Effect Transistor: Annealing Temperature and Solvent Effects. ResearchGate. [Link]

-

Dull, J. T., et al. (2020). Thermal Properties, Molecular Structure, and Thin-Film Organic Semiconductor Crystallization. Chemistry of Materials, 32(23), 10076-10084. [Link]

-

Lab Manager. (2023). Thermogravimetric Analysis (TGA) vs Differential Scanning Calorimetry (DSC): Comparing Thermal Analysis Techniques. [Link]

-

TA Instruments. (n.d.). Thermal Analysis of Phase Change Materials – Three Organic Waxes using TGA, DSC, and Modulated DSC®. [Link]

-

Kadri, D. A., et al. (2018). Optimization of 6,13Bis(triisopropylsilylethynyl)pentacene (TIPS-Pentacene) Organic Field Effect Transistor: Annealing Temperature and Solvent Effects. Scientific Research Publishing. [Link]

Sources

A Deep Dive into Soluble Pentacene Derivatives: From Discovery to Application

Foreword

Pentacene, a polycyclic aromatic hydrocarbon, has long captivated the attention of the materials science community for its exceptional charge transport properties, holding immense promise for next-generation organic electronics. However, its practical application has been severely hampered by its inherent insolubility and poor stability. This technical guide provides a comprehensive overview of the discovery and historical development of soluble pentacene derivatives, a pivotal breakthrough that has unlocked the potential of this remarkable organic semiconductor. We will explore the chemical strategies employed to overcome the solubility challenge, the evolution of these derivatives, and the profound impact they have had on the field of organic electronics. This guide is intended for researchers, scientists, and professionals in drug development and materials science who seek a deeper understanding of the structure-property relationships that govern the performance of these advanced materials.

The Pentacene Paradox: High Performance, Poor Processability

Pristine pentacene exhibits one of the highest charge carrier mobilities among organic semiconductors, making it a prime candidate for applications in organic thin-film transistors (OTFTs), organic photovoltaics (OPVs), and organic light-emitting diodes (OLEDs). However, its rigid, planar structure leads to strong intermolecular π-π stacking, resulting in a high lattice energy that renders it virtually insoluble in common organic solvents. This insolubility poses a significant challenge for device fabrication, as it precludes the use of cost-effective and scalable solution-based processing techniques like spin-coating, inkjet printing, and roll-to-roll printing. Early efforts to utilize pentacene relied on vacuum deposition methods, which are expensive, require high-vacuum conditions, and are not amenable to large-area device manufacturing.

The Breakthrough: Functionalization for Solubility

The quest for soluble pentacene derivatives began with the understanding that disrupting the strong intermolecular interactions was key. The central strategy that emerged was the covalent attachment of bulky functional groups to the pentacene core. These substituents serve a dual purpose: they increase the steric hindrance between pentacene molecules, thereby reducing the cohesive energy of the solid state, and they enhance the interaction with solvent molecules, promoting dissolution.

The Seminal Work of Anthony and co-workers

A significant breakthrough in this area was achieved by Professor John E. Anthony and his research group at the University of Kentucky. Their pioneering work in the early 2000s demonstrated that the functionalization of pentacene with silyl groups could dramatically enhance its solubility without significantly compromising its desirable electronic properties.

One of the most successful and widely adopted strategies involves the introduction of triisopropylsilylethynyl (TIPS) groups at the 6 and 13 positions of the pentacene core. This modification, yielding 6,13-bis(triisopropylsilylethynyl)pentacene (TIPS-pentacene), proved to be a game-changer. The bulky TIPS groups effectively prevent the close packing of the pentacene molecules, leading to a significant increase in solubility in common organic solvents like toluene, chloroform, and tetrahydrofuran.

Synthesis of TIPS-Pentacene: A Step-by-Step Protocol

The synthesis of TIPS-pentacene is a multi-step process that has been refined over the years. Below is a representative experimental protocol, highlighting the key chemical transformations.

Experimental Protocol: Synthesis of 6,13-Bis(triisopropylsilylethynyl)pentacene (TIPS-Pentacene)

-

Step 1: Synthesis of 6,13-Pentacenequinone. This initial step typically involves the oxidation of pentacene or a related precursor. A common method is the Diels-Alder reaction between 1,4-naphthoquinone and 1,3-cyclohexadiene, followed by aromatization.

-

Step 2: Ethynylation of 6,13-Pentacenequinone. The pentacenequinone is then reacted with an excess of triisopropylsilylacetylene in the presence of a strong base, such as n-butyllithium, in an inert solvent like anhydrous tetrahydrofuran (THF) at low temperatures (e.g., -78 °C). This reaction proceeds via a nucleophilic addition of the acetylide to the carbonyl groups.

-

Step 3: Reductive Aromatization. The resulting diol is then subjected to a reductive aromatization step. A common reagent for this transformation is tin(II) chloride (SnCl₂) in an acidic medium, such as hydrochloric acid in acetic acid. This step regenerates the aromatic pentacene core, now functionalized with the TIPS-ethynyl groups.

-

Step 4: Purification. The crude product is then purified using column chromatography on silica gel, typically with a non-polar eluent like hexane or a mixture of hexane and dichloromethane, to yield the final, highly pure TIPS-pentacene as a crystalline solid.

Causality Behind Experimental Choices:

-

Inert Atmosphere and Anhydrous Solvents: The use of an inert atmosphere (e.g., nitrogen or argon) and anhydrous solvents is crucial in the ethynylation step to prevent the quenching of the highly reactive organolithium reagent by moisture or oxygen.

-

Low-Temperature Reaction: The reaction is conducted at low temperatures to control the reactivity of the organolithium reagent and minimize side reactions.

-

Reductive Aromatization: The choice of SnCl₂ as a reducing agent is effective for the conversion of the diol to the fully aromatic pentacene system.

The Impact of Solubilization on Crystal Packing and Electronic Properties

The introduction of bulky substituents not only enhances solubility but also profoundly influences the solid-state packing of the pentacene derivatives. While pristine pentacene adopts a herringbone packing motif with significant π-orbital overlap, the sterically demanding substituents in soluble derivatives can alter this arrangement.

In the case of TIPS-pentacene, the molecules arrange in a 2D bricklayer motif. This packing structure, while different from pristine pentacene, still allows for significant π-π interactions between adjacent molecules, which is crucial for efficient charge transport. The charge carrier mobility of solution-processed TIPS-pentacene thin films can reach values comparable to or even exceeding that of vacuum-deposited pentacene, demonstrating the success of this molecular design strategy.

Table 1: Comparison of Properties of Pristine Pentacene and TIPS-Pentacene

| Property | Pristine Pentacene | 6,13-Bis(triisopropylsilylethynyl)pentacene (TIPS-Pentacene) |

| Solubility | Insoluble in common organic solvents | Soluble in toluene, chloroform, THF |

| Processing Method | Vacuum deposition | Solution processing (spin-coating, inkjet printing) |

| Crystal Packing | Herringbone | 2D Bricklayer |

| Charge Carrier Mobility | Up to 3 cm²/Vs (vacuum-deposited) | Up to 2 cm²/Vs (solution-processed) |

| Stability | Susceptible to oxidation in air and light | Improved stability due to steric protection by TIPS groups |

Evolution of Soluble Pentacene Derivatives: Beyond TIPS-Pentacene

The success of TIPS-pentacene spurred the development of a vast library of soluble pentacene derivatives with tailored properties. Researchers have explored a wide range of substituents at various positions on the pentacene core to fine-tune its solubility, electronic properties, and stability.

Key areas of exploration include:

-

Varying the Silyl Group: Replacing the triisopropylsilyl group with other silyl groups of different sizes and electronic properties has been investigated to modulate the balance between solubility and charge transport.

-

Functionalization at Different Positions: Attaching substituents at positions other than 6 and 13 has been explored to influence the molecular packing and electronic structure.

-

Introduction of Heteroatoms: Incorporating heteroatoms like nitrogen, sulfur, and oxygen into the pentacene core or the substituents can alter the energy levels (HOMO and LUMO) and improve stability.

-

Asymmetric Functionalization: Synthesizing asymmetrically functionalized pentacene derivatives has been shown to influence their self-assembly and thin-film morphology.

Conclusion and Future Outlook

The discovery and development of soluble pentacene derivatives represent a landmark achievement in the field of organic electronics. The ability to process these high-performance semiconductors from solution has paved the way for the fabrication of low-cost, large-area, and flexible electronic devices. The pioneering work on TIPS-pentacene has laid the foundation for the rational design of a new generation of organic semiconductors with tailored properties.

Future research in this area will likely focus on further enhancing the performance and stability of soluble pentacene derivatives. This includes the development of new synthetic methodologies, the exploration of novel substituent groups, and a deeper understanding of the complex interplay between molecular structure, solid-state packing, and device performance. The continued evolution of soluble pentacene derivatives holds the key to realizing the full potential of organic electronics in a wide range of applications, from flexible displays and wearable sensors to low-cost solar cells and integrated circuits.

References

-

Anthony, J. E., Brooks, J. S., Eaton, D. L., & Parkin, S. R. (2001). Functionalized Pentacene: Improved Electronic Properties from Control of Solid-State Order. Journal of the American Chemical Society, 123(38), 9482–9483. [Link]

-

Payne, M. M., Parkin, S. R., Anthony, J. E., Kuo, C. C., & Jackson, T. N. (2005). Organic Field-Effect Transistors from Solution-Deposited Functionalized Acenes. Journal of the American Chemical Society, 127(14), 4986–4987. [Link]

-

Anthony, J. E. (2006). Functionalized Acenes and Heteroacenes for Organic Electronics. Chemical Reviews, 106(12), 5028–5048. [Link]

Diagrams

Caption: Impact of functionalization on molecular packing.

Methodological & Application

Application Note & Protocol: Fabrication of High-Performance TES Pentacene Thin Films via Spin Coating

Authored by: Dr. Gemini, Senior Application Scientist

Abstract

This document provides a comprehensive guide for the fabrication of high-quality triethylsilylethynyl (TES) pentacene thin films using the spin coating technique. TES pentacene, a solution-processable derivative of pentacene, is a prominent organic semiconductor for applications in organic thin-film transistors (OTFTs) and other electronic devices. The performance of these devices is critically dependent on the morphology and crystalline quality of the semiconductor film. This guide details the underlying principles and provides step-by-step protocols for substrate preparation, solution formulation, spin coating parameter optimization, and post-deposition treatments to achieve highly ordered, crystalline thin films for superior device performance.

Introduction: The Significance of Solution-Processed TES Pentacene

Pentacene has long been a benchmark p-type organic semiconductor due to its high charge carrier mobility. However, its poor solubility has historically limited its application to expensive vacuum deposition methods.[1] The introduction of triethylsilylethynyl (TES) functional groups at the 6 and 13 positions of the pentacene core renders the molecule soluble in common organic solvents, enabling the use of cost-effective, large-area solution-based deposition techniques like spin coating.[2]

The key to high-performance TES pentacene devices lies in controlling the thin-film morphology during the solution-to-solid phase transition. Spin coating offers a simple yet powerful method to produce uniform films, but achieving large, well-interconnected crystalline domains requires careful optimization of multiple interdependent parameters. This guide elucidates the causal relationships between processing choices and the resulting film quality, empowering researchers to fabricate high-performance organic electronic devices.

The Science Behind TES Pentacene Film Formation

The formation of a crystalline TES pentacene film from solution is a complex process governed by solvent evaporation, solute precipitation, and molecular self-assembly. During spin coating, the rapid solvent evaporation concentrates the TES pentacene solution. As the solution becomes supersaturated, nucleation and crystal growth begin. The final morphology is heavily influenced by the solvent's boiling point and its interaction with both the solute and the substrate surface. Solvents with higher boiling points, such as toluene or chlorobenzene, evaporate more slowly, allowing more time for molecular organization and leading to more ordered films.[3]

A critical aspect of many solution-processed organic semiconductors, including pentacene, is the potential formation of a metastable "thin-film" phase during rapid solvent evaporation.[4] This phase can be transformed into a more thermodynamically stable, highly ordered bulk-like phase through post-deposition treatments like solvent or thermal annealing. This phase transition is essential for achieving optimal π-π stacking and high charge carrier mobility.

Experimental Workflow and Protocols

This section details the complete workflow, from substrate preparation to the final film characterization.

Diagram: TES Pentacene Spin Coating Workflow

Caption: Solvent annealing facilitates the transition from a disordered to a crystalline phase.

Protocol: Solvent Vapor Annealing

-

Setup: Place the substrate with the as-spun film into a petri dish or a small, sealable chamber.

-

Solvent Reservoir: In the same chamber, place a small vial containing a few milliliters of a volatile solvent such as dichloromethane (DCM) or toluene. [1][5]DCM is often effective. Do not let the liquid solvent touch the substrate.

-

Sealing: Seal the chamber to create a solvent-saturated atmosphere.

-

Annealing: Leave the setup undisturbed at room temperature for 1 to 12 hours. The solvent molecules interact with the film surface, inducing a solid-solid phase transition without fully dissolving the film. [6]This process increases molecular mobility, allowing for rearrangement into larger, more ordered crystalline domains. [5]5. Drying: After annealing, remove the substrate and allow any residual solvent to evaporate. A gentle thermal bake (e.g., 60°C for 10 minutes) can be performed to ensure all solvent is removed.

Characterization and Expected Results

The quality of the fabricated TES pentacene thin films should be assessed using appropriate characterization techniques:

-

Atomic Force Microscopy (AFM): To visualize the surface morphology, grain size, and crystalline terraces. High-quality films will show large, interconnected crystalline domains.

-

X-ray Diffraction (XRD): To confirm the crystallinity and determine the molecular packing orientation. Well-ordered films will exhibit sharp diffraction peaks corresponding to the (00l) planes, indicating a standing-up orientation of the pentacene molecules, which is favorable for charge transport in a transistor.

-

Polarized Optical Microscopy (POM): To observe the crystalline domains (spherulites) over a large area. The birefringence of the crystalline domains makes them visible under cross-polarized light.

-

Electrical Characterization: Fabricating OTFTs and measuring their transfer and output characteristics will provide the ultimate measure of film quality, yielding key performance metrics like charge carrier mobility and on/off ratio. Mobilities for TES-pentacene can range from 10⁻⁵ to over 0.05 cm²/Vs depending on processing conditions. [1][2]

Troubleshooting

| Problem | Possible Cause(s) | Suggested Solution(s) |

| Dewetting/Poor Film Uniformity | Improper substrate cleaning; Surface is not sufficiently hydrophobic. | Repeat substrate cleaning protocol; Ensure a thorough and complete HMDS treatment. |

| "Coffee Ring" Effect | Solvent evaporation rate is too high at the edges. | Use a solvent with a higher boiling point (e.g., switch from toluene to chlorobenzene); Optimize spin speed and acceleration. |

| Amorphous or Small-Grain Films | Insufficient time for molecular ordering; Ineffective annealing. | Increase solvent annealing time; Try a different annealing solvent; Optimize solution concentration. |

| Low Device Mobility | Poor crystal connectivity; Traps at the dielectric interface; Unfavorable molecular packing. | Optimize annealing to improve grain size and interconnectivity; Ensure high-purity materials and clean processing environment; Confirm hydrophobic surface treatment was successful. |

References

-

Gundlach, D. J., Lin, Y. Y., Jackson, T. N., Nelson, S. F., & Schlom, D. G. (1999). Solvent-induced phase transition in thermally evaporated pentacene films. Applied Physics Letters, 74(22), 3302-3304. [Link]

-

Paul, T., Mondal, S., & Joseph, B. (2023). Diffusion-Induced Thickness Thinning of Spin-Coated Films in Crystalline Grain Boundaries. Advanced Materials Interfaces, 10(2), 2202293. [Link]

-

Zain, M. Z. I. M., & Ahmad, Z. A. (2022). Pentacene and Its Derivatives Deposition Methods. Encyclopedia.pub. [Link]

-

Zain, M. Z. I. M., et al. (2022). Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance. Polymers, 14(6), 1121. [Link]

-

Dadvand, A., et al. (2012). Solvent vapor annealing of an insoluble molecular semiconductor. Journal of Materials Chemistry, 22(44), 23653-23658. [Link]

-

Hagmann, K., Bunk, C., Böhme, F., & von Klitzing, R. (2019). Effects of spin coating technique and rotation speed on film thickness and roughness. ResearchGate. [Link]

-

Kadri, D. A., et al. (2018). Optimization of 6,13-Bis(triisopropylsilylethynyl)pentacene (TIPS-Pentacene) Organic Field Effect Transistor: Annealing Temperature and Solvent Effects. Materials Sciences and Applications, 9(11), 903-915. [Link]

-

Kadri, D. A., et al. (2018). Optimization of 6,13-Bis(triisopropylsilylethynyl)pentacene (TIPS-Pentacene) Organic Field Effect Transistor. ResearchGate. [Link]

-

Nelson, S. (2009). Thin Film Formation of a Solution Processed Pentacene. UC Berkeley EECS. [Link]

-

Salleo, A., & Heremans, P. (2011). 6 - Studies of spin-coated polymer films. ResearchGate. [Link]

-

Lee, W. H., et al. (2014). In-situ monitoring of the spin coating of a TIPS-pentacene/PS blend solution. ResearchGate. [Link]

-

Zain, M. Z. I. M., et al. (2022). Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance. MDPI. [Link]

-

Gundlach, D. J., et al. (1999). Solvent-induced phase transition in thermally evaporated pentacene films. ResearchGate. [Link]

-

Tyona, M. D. (2013). A comprehensive study of spin coating as a thin film deposition technique and spin coating equipment. Techno Press. [Link]

-

Panzer, F., et al. (2024). Reactive spin coating based on real-time in situ feedback for improved control of perovskite thin film fabrication. Journal of Materials Chemistry C. [Link]

-

Tan, J. (2022). What is a good hydrophobic treatment that can obtain a superhydrophobic surface while avoiding the pinning effect caused by the change in CA? ResearchGate. [Link]

-

Chen, Y. C., et al. (2020). Initial growth of pentacene on a Si(111)-sqrt(3) x sqrt(3)-In surface. Physical Chemistry Chemical Physics, 22(26), 14748-14755. [Link]

-

Thierry, C. (2024). Creating Superhydrophobic Surfaces with Plasma Treatment. AZoM. [Link]

-

Wang, Y., et al. (2021). Grain Boundary Control of Organic Semiconductors via Solvent Vapor Annealing for High-Sensitivity NO2 Detection. Sensors (Basel), 21(1), 226. [Link]

Sources

- 1. Review of the Common Deposition Methods of Thin-Film Pentacene, Its Derivatives, and Their Performance - PMC [pmc.ncbi.nlm.nih.gov]

- 2. mdpi.com [mdpi.com]

- 3. Optimization of 6,13Bis(triisopropylsilylethynyl)pentacene (TIPS-Pentacene) Organic Field Effect Transistor: Annealing Temperature and Solvent Effects [scirp.org]

- 4. schlom.mse.cornell.edu [schlom.mse.cornell.edu]

- 5. Grain Boundary Control of Organic Semiconductors via Solvent Vapor Annealing for High-Sensitivity NO2 Detection - PubMed [pubmed.ncbi.nlm.nih.gov]

- 6. Solvent vapor annealing of an insoluble molecular semiconductor - Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

Application Note: Harnessing the Potential of Solution-Processable Pentacene Derivatives for High-Efficiency Organic Photovoltaics

An Application Note and Protocol for the Utilization of TES Pentacene in Organic Photovoltaic Cells

Introduction

Pentacene, a polycyclic aromatic hydrocarbon with five linearly-fused benzene rings, is a benchmark p-type organic semiconductor renowned for its excellent charge transport properties and strong absorption in the visible spectrum.[1][2][3] Its crystalline nature facilitates efficient charge movement, making it a highly promising material for organic electronic devices, including organic field-effect transistors (OFETs) and organic photovoltaic (OPV) cells.[4][5] However, the utility of pristine pentacene is often limited by its poor solubility in common organic solvents, necessitating vacuum deposition techniques for thin-film fabrication.

To overcome this limitation, soluble derivatives of pentacene have been developed. A prominent and highly successful class of these materials involves the functionalization of the pentacene core with trialkylsilylethynyl groups. The most widely studied derivative is 6,13-bis(triisopropylsilylethynyl)pentacene, commonly known as TIPS-pentacene . The bulky triisopropylsilyl (TIPS) groups enhance solubility, enabling the use of cost-effective, large-area solution-based deposition methods like spin coating, drop-casting, and solution shearing.[6][7] This application note focuses on this class of materials, referred to broadly as TES (Tri-Ethyl-Silyl) or, more commonly, TIPS-pentacene, and provides a comprehensive guide to its application as an electron donor material in OPV devices.

The addition of these side chains not only imparts solubility but also influences the material's electronic properties and solid-state packing, which are critical for OPV device performance.[6] When paired with suitable electron acceptor materials, such as fullerenes (e.g., C60, PCBM) or non-fullerene acceptors (NFAs), TIPS-pentacene can form an efficient bulk heterojunction (BHJ) or planar heterojunction active layer for converting solar energy into electricity.[8][9][10]

Part 1: Fundamental Principles and Device Architecture

Mechanism of an Organic Photovoltaic Cell

The operation of a TIPS-pentacene-based OPV device involves several key steps:

-

Light Absorption: Photons from sunlight are absorbed by the donor (TIPS-pentacene) and/or acceptor material, creating tightly bound electron-hole pairs known as excitons.[1]

-

Exciton Diffusion: These excitons migrate through the material. For charge generation to occur, they must reach the interface between the donor and acceptor materials before they recombine.[1][9]

-

Charge Separation: At the donor-acceptor interface, the energy level offset provides the driving force to separate the exciton. The electron is transferred to the acceptor's Lowest Unoccupied Molecular Orbital (LUMO), and the hole remains on the donor's Highest Occupied Molecular Orbital (HOMO).[11]

-

Charge Transport: The separated electrons and holes travel through the acceptor and donor materials, respectively, towards their corresponding electrodes (cathode and anode).

-

Charge Collection: The charges are collected at the electrodes, generating a photocurrent.

Device Architecture and Energy Level Alignment

A typical OPV device using TIPS-pentacene as the donor layer is fabricated in a multi-layered structure. The most common architecture is the "conventional" device stack, though an "inverted" structure is also possible.

Conventional Device Structure:

-

Transparent Anode: Typically Indium Tin Oxide (ITO) on a glass or flexible substrate.

-

Hole Transport Layer (HTL): A layer of poly(3,4-ethylenedioxythiophene) polystyrene sulfonate (PEDOT:PSS) is commonly used to facilitate hole collection by the anode and to smooth the ITO surface.

-

Active Layer: A blend (for BHJ) or bilayer (for planar heterojunction) of TIPS-pentacene (donor) and an electron acceptor, such as Phenyl-C61-butyric acid methyl ester (PCBM).[8]

-

Electron Transport/Hole Blocking Layer (ETL/HBL): A thin layer, such as bathocuproine (BCP) or calcium, is often inserted between the active layer and the cathode to block holes and improve electron collection.[11][12]

-

Metal Cathode: A low work function metal, such as Aluminum (Al) or Calcium/Aluminum (Ca/Al), is deposited on top to collect electrons.

Below is a diagram illustrating the conventional device architecture.

Caption: Conventional device architecture for a TIPS-pentacene based OPV.

Energy Level Alignment: Efficient charge separation and transport are critically dependent on the relative energy levels of the materials used. The HOMO of the donor should be higher than the HOMO of the acceptor to create a barrier for hole transfer to the acceptor, while the LUMO of the donor must be higher than the LUMO of the acceptor to provide the driving force for electron transfer.

| Material | HOMO (eV) | LUMO (eV) |

| TIPS-Pentacene | ~ -5.2 eV | ~ -3.0 eV |

| PCBM (-Phenyl-C61-butyric acid methyl ester) | ~ -6.1 eV | ~ -4.3 eV |

| C60 (Fullerene) | ~ -6.2 eV | ~ -4.5 eV |

| PEDOT:PSS | ~ -5.2 eV | - |

| Aluminum (Al) Work Function | ~ -4.2 eV | ~ -4.2 eV |

| ITO Work Function | ~ -4.7 eV | ~ -4.7 eV |

Note: These values are approximate and can vary based on processing conditions and measurement techniques.[13][14][15]

The energy level diagram below illustrates the charge separation and transport process.

Caption: Energy level diagram for a TIPS-pentacene:PCBM based OPV.

Part 2: Experimental Protocols

This section provides a step-by-step protocol for the fabrication of a solution-processed bulk heterojunction OPV device.

Materials and Equipment

-

Substrates: Pre-patterned ITO-coated glass slides.

-

Chemicals:

-

Equipment:

-

Glovebox with an inert atmosphere (N2 or Ar).

-

Spin coater.

-

Hotplate.

-

Ultrasonic bath.

-

Thermal evaporator.

-

Solar simulator (AM 1.5G, 100 mW/cm²).

-

Source measure unit (SMU) for J-V characterization.

-

Protocol: Device Fabrication

Step 1: Substrate Cleaning (Critical for Performance) Causality: A pristine ITO surface is essential for achieving good film morphology and efficient charge injection. Any organic residue or particulate matter can lead to short circuits and poor device performance.

-

Place ITO substrates in a substrate rack.

-

Sequentially sonicate the substrates in the following baths for 15 minutes each:

-

Detergent solution (e.g., 2% Hellmanex in DI water).

-

DI water (repeat twice).

-

Isopropyl alcohol (IPA).

-

-

Dry the substrates thoroughly with a nitrogen or argon gun.

-

Treat the substrates with UV-Ozone for 15 minutes immediately before use to remove final organic contaminants and increase the work function of the ITO, improving hole collection.[18]

Step 2: Hole Transport Layer (HTL) Deposition Causality: The PEDOT:PSS layer reduces the energy barrier for hole extraction from the active layer to the ITO anode and helps prevent short circuits by planarizing the ITO surface.

-

Transfer the cleaned substrates into a nitrogen-filled glovebox.

-

Filter the PEDOT:PSS solution through a 0.45 µm PVDF syringe filter.

-

Deposit the HTL by spin coating the filtered PEDOT:PSS solution onto the ITO substrates. A typical spin program is a two-step process: 500 rpm for 5 seconds (spread), followed by 4000 rpm for 40 seconds.

-

Anneal the substrates on a hotplate at 140-150°C for 10-15 minutes to remove residual water.

Step 3: Active Layer Solution Preparation Causality: The donor:acceptor ratio and solution concentration are critical parameters that control the film's morphology, which in turn dictates exciton dissociation and charge transport efficiency.

-

Inside the glovebox, prepare a stock solution of TIPS-pentacene and PCBM in a suitable solvent like chlorobenzene or toluene.

-

A common starting point is a total solids concentration of 20 mg/mL with a TIPS-pentacene:PCBM weight ratio of 1:1.

-

Gently heat the solution (e.g., to 50-60°C) and stir overnight to ensure complete dissolution.

-

Before use, cool the solution to room temperature and filter it through a 0.45 µm PTFE syringe filter.

Step 4: Active Layer Deposition Causality: The spin coating speed and subsequent annealing temperature directly influence the film thickness and the degree of molecular ordering (crystallinity) and phase separation in the blend. Slow solvent evaporation during or after deposition can promote the formation of more ordered crystalline domains, which is often beneficial for charge mobility.[7]

-

Allow the PEDOT:PSS-coated substrates to cool to room temperature.

-

Spin coat the active layer solution onto the HTL. A typical spin speed is 1000-2000 rpm for 60 seconds to achieve a film thickness of 80-120 nm.

-

Transfer the substrates to a hotplate for thermal annealing. An annealing temperature of 110-150°C for 10 minutes is a common starting point. This step helps to optimize the nanoscale morphology of the bulk heterojunction.[19]

Step 5: Cathode Deposition Causality: A low work function metal is required to form an ohmic contact for electron collection. A hole-blocking layer (HBL) like BCP can prevent excitons from being quenched at the cathode and block holes from reaching the cathode, reducing leakage currents.[12]

-

Transfer the substrates to a high-vacuum thermal evaporator (<10⁻⁶ Torr).

-

Use a shadow mask to define the cathode areas, creating individual device pixels.

-

(Optional but recommended) Deposit a thin (5-10 nm) layer of BCP as a hole-blocking layer.

-

Deposit the metal cathode, typically 100 nm of Aluminum (Al). The deposition rate should be slow (0.1-0.5 Å/s) initially to prevent damage to the organic layer, then can be increased to 1-2 Å/s.

Part 3: Device Characterization and Performance

Current Density-Voltage (J-V) Characterization

The primary method for evaluating OPV performance is by measuring the J-V curve under simulated sunlight.

-

The device is illuminated using a solar simulator calibrated to the AM 1.5G spectrum at 100 mW/cm².

-

A source measure unit (SMU) is used to sweep the voltage across the device (e.g., from -0.5 V to 1.0 V) and measure the resulting current.

-

Key performance parameters are extracted from the J-V curve:

-

Open-Circuit Voltage (V_oc): The voltage at which the current is zero. It is related to the HOMO of the donor and LUMO of the acceptor.

-

Short-Circuit Current Density (J_sc): The current density at zero voltage. It depends on light absorption, and the efficiency of charge generation, transport, and collection.

-

Fill Factor (FF): A measure of the "squareness" of the J-V curve, calculated as (J_mp * V_mp) / (J_sc * V_oc), where J_mp and V_mp are the current and voltage at the maximum power point.

-

Power Conversion Efficiency (PCE): The overall efficiency of the device, calculated as PCE (%) = (J_sc * V_oc * FF) / P_in, where P_in is the incident light power density (100 mW/cm²).

-

Expected Performance Metrics

The performance of TIPS-pentacene based solar cells can vary significantly based on the choice of acceptor, device architecture, and processing conditions.

| Donor:Acceptor | V_oc (V) | J_sc (mA/cm²) | FF (%) | PCE (%) | Reference |

| TIPS-Pentacene:C60 | 0.90 | ~1-2 | ~40-50 | ~0.8-1.0 | |

| Pentacene:C60 (Planar) | 0.36 | ~8.0 | ~46 | ~1.3 | [9] |

| TIPSAntBT:PCBM | ~0.7 | ~4.5 | ~45 | ~1.4 | [8] |

| P3HT:Cyanopentacene | ~0.6 | ~1.5 | ~48 | ~0.43 | [6] |

Note: The table includes data for closely related pentacene derivatives and architectures to provide a performance context. Power conversion efficiencies for solution-processed small molecule OPVs have advanced significantly, with optimized systems exceeding these early values.

Further Characterization

-

External Quantum Efficiency (EQE): Measures the ratio of collected charge carriers to incident photons at a specific wavelength. The integral of the EQE spectrum over the solar spectrum should correspond to the J_sc.[9]

-

Atomic Force Microscopy (AFM): Used to investigate the surface morphology and roughness of the active layer, providing insights into the degree of phase separation.[20]

-

X-ray Diffraction (XRD): Can be used to assess the crystallinity and molecular orientation within the TIPS-pentacene film.[21]

References

- A dopant free linear acene derivative as a hole transport material for perovskite pigmented solar cells. Energy & Environmental Science (RSC Publishing).

- Photovoltaic cells from a soluble pentacene derivative. ResearchGate.

- High-Performance Solution-Processed Pentacene/Al Schottky Ultraviolet Photodiode With Pseudo Photovoltaic Effect. Semantic Scholar.

- Soluble n-type pentacene derivatives as novel acceptors for organic solar cells. Unknown Source.

- Solution-processed organic photovoltaic cells with anthracene derivatives. PubMed.

- Organic photovoltaic cells with high open circuit voltages based on pentacene derivatives. Chic Geek and Chemistry Freak.

- Efficient thin-film organic solar cells based on pentacene/C >60> heterojunctions. Unknown Source.

- Efficiently Organic: Researchers Use Pentacene To Develop Next-generation Solar Power. Unknown Source.

- Pentacene patterns prove crucial for solar power. Imperial College London.

- Efficient organic solar cells using polycrystalline pentacene films. SPIE, the international society for optics and photonics.

- Efficient thin-film organic solar cells based on pentacene/C60 heterojunctions. KOASAS.

- Growth and Characterization of Centimeter-Scale Pentacene Crystals for Optoelectronic Devices. MDPI.

- (a) HOMO–LUMO energy level diagram of the TIPS-pentacene/Si/PCBM hybrid... ResearchGate.

- Synthesis, characterization of the pentacene and fabrication of pentacene field-effect transistors. ResearchGate.

- TIPS-Pentacene. Ossila.

- Pentacene/fullerene (C 60) heterojunction solar cells: Device performance and degradation mechanisms. ResearchGate.

- Analyses of All Small Molecule-Based Pentacene/C60 Organic Photodiodes Using Vacuum Evaporation Method. MDPI.

- Layer-by-layer fabrication of organic photovoltaic devices: material selection and processing conditions. RSC Publishing.

- Pentacene. Wikipedia.

- Pentacene. Encyclopedia MDPI.

- Functional fullerenes for organic photovoltaics. Journal of Materials Chemistry (RSC Publishing).

- Pentacene/non-fullerene acceptor heterojunction type phototransistors for broadened spectral photoresponsivity and ultralow level light detection. Journal of Materials Chemistry C (RSC Publishing).

- Deciphering the Morphology Change and Performance Enhancement for Perovskite Solar Cells Induced by Surface Modification. Unknown Source.

- Making OLEDs and OPVs: A Quickstart Guide. Ossila.

Sources

- 1. spie.org [spie.org]

- 2. Pentacene - Wikipedia [en.wikipedia.org]

- 3. Pentacene | Encyclopedia MDPI [encyclopedia.pub]

- 4. sciencedaily.com [sciencedaily.com]

- 5. mdpi.com [mdpi.com]

- 6. researchgate.net [researchgate.net]

- 7. ossila.com [ossila.com]

- 8. Solution-processed organic photovoltaic cells with anthracene derivatives - PubMed [pubmed.ncbi.nlm.nih.gov]

- 9. pure.kaist.ac.kr [pure.kaist.ac.kr]

- 10. Pentacene/non-fullerene acceptor heterojunction type phototransistors for broadened spectral photoresponsivity and ultralow level light detection - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 11. koasas.kaist.ac.kr [koasas.kaist.ac.kr]

- 12. Analyses of All Small Molecule-Based Pentacene/C60 Organic Photodiodes Using Vacuum Evaporation Method [mdpi.com]

- 13. A dopant free linear acene derivative as a hole transport material for perovskite pigmented solar cells - Energy & Environmental Science (RSC Publishing) [pubs.rsc.org]

- 14. researchgate.net [researchgate.net]

- 15. Layer-by-layer fabrication of organic photovoltaic devices: material selection and processing conditions - Journal of Materials Chemistry C (RSC Publishing) DOI:10.1039/D0TC04146G [pubs.rsc.org]

- 16. Functional fullerenes for organic photovoltaics - Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- 17. ossila.com [ossila.com]

- 18. researchgate.net [researchgate.net]

- 19. researchgate.net [researchgate.net]

- 20. research.abo.fi [research.abo.fi]

- 21. researchgate.net [researchgate.net]

Application Notes and Protocols for Dissolving TES Pentacene in Organic Solvents

Introduction: The Critical Role of Solution Processing in High-Performance Organic Electronics

6,13-Bis(triisopropylsilylethynyl) pentacene, commonly known as TES pentacene or TIPS-pentacene, is a high-performance p-type organic semiconductor renowned for its excellent charge carrier mobility and environmental stability.[1] The triisopropylsilylethynyl (TIPS) functional groups enhance the solubility of the pentacene core in common organic solvents, making it amenable to solution-based fabrication techniques such as spin coating, drop casting, and inkjet printing.[1][2] These low-cost, large-area compatible methods are pivotal for the advancement of flexible and printed electronics.

The quality of the TES pentacene solution is a critical determinant of the resulting thin film's morphology, crystallinity, and, consequently, the performance of the final electronic device. Inhomogeneous solutions, incomplete dissolution, or the presence of aggregates can lead to defects in the semiconductor layer, resulting in poor device performance and lack of reproducibility. Therefore, a thorough understanding of the principles and protocols for dissolving TES pentacene is paramount for researchers and professionals in the field.

This comprehensive guide provides detailed application notes and protocols for the effective dissolution of TES pentacene in various organic solvents. It is designed to equip researchers, scientists, and drug development professionals with the expertise to prepare high-quality TES pentacene solutions, troubleshoot common issues, and optimize their experimental workflows for the fabrication of high-performance organic electronic devices.

Solvent Selection: A Multifaceted Decision

The choice of solvent is the most critical factor in the preparation of TES pentacene solutions. An ideal solvent should not only exhibit high solubility for TES pentacene but also possess physical properties that are conducive to the desired deposition technique and promote the formation of a well-ordered crystalline thin film.

Hansen Solubility Parameters: A Predictive Framework

The principle of "like dissolves like" is a fundamental concept in solubility. The Hansen Solubility Parameters (HSP) provide a quantitative framework to this principle by deconstructing the total cohesive energy of a substance into three components:

-

δD (Dispersion): Arising from van der Waals forces.

-

δP (Polar): Originating from dipole-dipole interactions.

-

δH (Hydrogen Bonding): Accounting for hydrogen bond formation.

For a solute to dissolve in a solvent, their HSP values should be similar. The "distance" (Ra) between the HSP of the solute and the solvent in the three-dimensional Hansen space can be calculated. A smaller Ra value indicates a higher affinity and, therefore, better solubility.

The following table provides the Hansen Solubility Parameters for several common organic solvents.

| Solvent | δD (MPa½) | δP (MPa½) | δH (MPa½) |

| Toluene | 18.0 | 1.4 | 2.0 |

| Chloroform | 17.8 | 3.1 | 5.7 |

| Chlorobenzene | 19.0 | 4.3 | 2.0 |

| o-Xylene | 17.8 | 1.0 | 3.1 |

| Anisole | 17.8 | 4.4 | 6.9 |

Data sourced from reference[6]

This data aligns with experimental observations that non-polar, aromatic solvents are excellent choices for dissolving TES pentacene.

Quantitative Solubility of TES Pentacene

The following table summarizes the experimentally determined solubility of TES pentacene in various organic solvents at room temperature (23 °C).

| Solvent | Solubility (wt. %) |

| Toluene | 6.57 |

| n-Butylbenzene | 3.43 |

| Anisole | 2.03 |

| Acetone | 0.16 |

Data sourced from reference

This quantitative data underscores the high solubility of TES pentacene in aromatic solvents like toluene and highlights the importance of solvent selection for achieving desired solution concentrations.

The Influence of Solvent Boiling Point on Film Morphology

The boiling point of the solvent plays a crucial role in the thin-film formation process. High-boiling-point solvents evaporate more slowly, allowing more time for the TES pentacene molecules to self-organize into well-ordered crystalline domains.[7] This generally leads to larger crystal grains and improved charge transport properties in the resulting organic thin-film transistors (OTFTs).

-

Low-Boiling-Point Solvents (e.g., Chloroform, Dichloromethane): Rapid evaporation can lead to amorphous or poorly crystalline films.[8]

-

High-Boiling-Point Solvents (e.g., Toluene, Chlorobenzene, Xylene, Anisole): Slower evaporation promotes the growth of larger, more ordered crystals, which is generally desirable for high-performance devices.[7]

The choice of solvent boiling point should be tailored to the specific deposition technique. For instance, in spin coating, a solvent with a moderate evaporation rate is often preferred to achieve a uniform film, while in drop casting, a high-boiling-point solvent is typically used to facilitate slow crystallization.

Protocols for Dissolving TES Pentacene

The following protocols provide detailed, step-by-step methodologies for preparing TES pentacene solutions. Adherence to these protocols is crucial for achieving consistent and reproducible results.

General Considerations and Safety Precautions

-

Purity of TES Pentacene: Start with high-purity TES pentacene (>99%) to minimize the impact of impurities on device performance.

-

Solvent Quality: Use anhydrous, high-purity solvents to prevent unwanted side reactions and the incorporation of water into the thin film. The presence of water can be detrimental to the performance and stability of organic electronic devices.

-

Inert Atmosphere: Whenever possible, prepare TES pentacene solutions in an inert atmosphere (e.g., a glovebox filled with nitrogen or argon). TES pentacene solutions can degrade upon prolonged exposure to air and light.[9]

-

Safety: Always handle organic solvents in a well-ventilated fume hood. Wear appropriate personal protective equipment (PPE), including safety goggles, gloves, and a lab coat. Consult the Safety Data Sheet (SDS) for each chemical before use.

Protocol 1: Standard Dissolution for General Applications

This protocol is suitable for preparing TES pentacene solutions for a variety of applications, including spin coating and drop casting.

Materials and Equipment:

-

High-purity TES pentacene powder

-

Anhydrous organic solvent (e.g., toluene, chlorobenzene, anisole)

-

Glass vial with a PTFE-lined cap

-

Magnetic stirrer and stir bar

-

Hot plate with temperature control

-

Syringe filters (0.2 μm or 0.45 μm, PTFE)

Workflow Diagram:

Caption: General workflow for dissolving TES pentacene.

Step-by-Step Procedure:

-

Weighing: Accurately weigh the desired amount of TES pentacene powder and transfer it to a clean, dry glass vial.

-

Solvent Addition: Add the calculated volume of the chosen anhydrous organic solvent to the vial to achieve the desired concentration (e.g., 1-10 mg/mL).

-

Sealing: Place a clean magnetic stir bar into the vial and securely seal it with a PTFE-lined cap to prevent solvent evaporation.

-

Heating and Stirring: Place the vial on a hot plate with magnetic stirring. Heat the solution to a moderately elevated temperature (e.g., 50-70 °C) while stirring vigorously (e.g., 500-1000 rpm).[8][9] The elevated temperature increases the solubility and dissolution rate. Continue heating and stirring for at least 1 hour or until the TES pentacene is completely dissolved, resulting in a clear, dark blue solution with no visible particulates.

-

Cooling: Turn off the heat and allow the solution to cool down to room temperature while continuing to stir.

-

Filtration: To remove any remaining micro-particles or aggregates, filter the solution through a syringe filter (0.2 μm or 0.45 μm PTFE) into a clean vial. This step is crucial for obtaining high-quality thin films.

-

Storage: Store the filtered solution in a tightly sealed vial, protected from light, in an inert atmosphere (e.g., inside a glovebox). It is recommended to use freshly prepared solutions for optimal results, as they can degrade over time, especially if exposed to ambient conditions for more than 24 hours.[9]

Protocol 2: Preparation of Solutions with Mixed Solvents

The use of a mixed solvent system can be a powerful strategy to fine-tune the evaporation rate and influence the thin-film morphology.

Rationale: