Btqbt

Description

BenchChem offers high-quality Btqbt suitable for many research applications. Different packaging options are available to accommodate customers' requirements. Please inquire for more information about Btqbt including the price, delivery time, and more detailed information at info@benchchem.com.

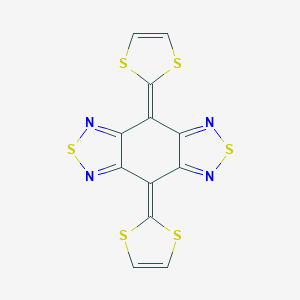

Structure

3D Structure

Properties

IUPAC Name |

4,8-bis(1,3-dithiol-2-ylidene)-[1,2,5]thiadiazolo[3,4-f][2,1,3]benzothiadiazole | |

|---|---|---|

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

InChI |

InChI=1S/C12H4N4S6/c1-2-18-11(17-1)5-7-9(15-21-13-7)6(12-19-3-4-20-12)10-8(5)14-22-16-10/h1-4H | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

InChI Key |

ABMLGFPCLXTCEI-UHFFFAOYSA-N | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Canonical SMILES |

C1=CSC(=C2C3=NSN=C3C(=C4SC=CS4)C5=NSN=C25)S1 | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Molecular Formula |

C12H4N4S6 | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

DSSTOX Substance ID |

DTXSID70567150 | |

| Record name | 4,8-Bis(2H-1,3-dithiol-2-ylidene)-4H,8H-benzo[1,2-c:4,5-c']bis[1,2,5]thiadiazole | |

| Source | EPA DSSTox | |

| URL | https://comptox.epa.gov/dashboard/DTXSID70567150 | |

| Description | DSSTox provides a high quality public chemistry resource for supporting improved predictive toxicology. | |

Molecular Weight |

396.6 g/mol | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

CAS No. |

135704-54-0 | |

| Record name | 4,8-Bis(2H-1,3-dithiol-2-ylidene)-4H,8H-benzo[1,2-c:4,5-c']bis[1,2,5]thiadiazole | |

| Source | EPA DSSTox | |

| URL | https://comptox.epa.gov/dashboard/DTXSID70567150 | |

| Description | DSSTox provides a high quality public chemistry resource for supporting improved predictive toxicology. | |

Foundational & Exploratory

An In-Depth Technical Guide to the Synthesis and Purification of Bis(1,2,5-thiadiazolo)-p-quinobis(1,3-dithiole) (Btqbt)

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides a comprehensive overview of the synthesis and purification methods for Bis(1,2,5-thiadiazolo)-p-quinobis(1,3-dithiole), commonly known as Btqbt. This document details the underlying chemical reactions, experimental protocols, and purification techniques, presenting quantitative data in a clear, tabular format. Furthermore, visual diagrams of the synthesis workflow are provided to facilitate a deeper understanding of the process.

Introduction

Btqbt, with the IUPAC name 4,8-Bis(1,3-dithiol-2-ylidene)-4H,8H-benzo[1,2-c:4,5-c']bisthiadiazole and CAS number 135704-54-0, is a novel organic semiconductor. Its unique molecular structure, characterized by a planar backbone and significant intermolecular sulfur-sulfur interactions, imparts favorable electronic properties. This has led to its investigation in various applications, including organic electronics. This guide focuses on the chemical synthesis and purification of this promising molecule.

Synthesis of Btqbt

The primary method for the synthesis of Btqbt is a Wittig-Horner reaction. This approach involves the reaction of a phosphonate ylide with a ketone to form an alkene. In the case of Btqbt synthesis, the key precursors are a phosphonate-containing dithiole and a specialized dione.

Synthesis of Precursors

The successful synthesis of Btqbt relies on the preparation of two key starting materials:

-

Benzo[1,2-c:4,5-c']bisthiadiazole-4,8-dione (1): This dione serves as the core of the Btqbt molecule.

-

2-Diethylphosphono-1,3-dithiole (2): This phosphonate reagent provides the dithiole units that are coupled to the central core.

The synthesis of these precursors is a critical first step and is outlined in the experimental protocols below.

The Wittig-Horner Reaction

The core of the Btqbt synthesis is the Wittig-Horner olefination reaction. In this step, the phosphonate ylide generated from 2-diethylphosphono-1,3-dithiole (2) reacts with benzo[1,2-c:4,5-c']bisthiadiazole-4,8-dione (1) to form the target molecule, Btqbt. The reaction is typically carried out in the presence of a strong base, such as sodium hydride, in an anhydrous solvent like tetrahydrofuran (THF).

Below is a diagram illustrating the logical workflow of the Btqbt synthesis.

Caption: Logical workflow for the synthesis of Btqbt.

Experimental Protocols

The following are detailed experimental protocols for the synthesis of the precursors and the final Btqbt product.

Synthesis of Benzo[1,2-c:4,5-c']bisthiadiazole-4,8-dione (1)

Synthesis of 2-Diethylphosphono-1,3-dithiole (2)

Synthesis of Btqbt via Wittig-Horner Reaction

Materials and Reagents:

| Reagent | Molar Mass ( g/mol ) | Quantity | Moles |

| Benzo[1,2-c:4,5-c']bisthiadiazole-4,8-dione (1) | 224.23 | [Specify] | [Specify] |

| 2-Diethylphosphono-1,3-dithiole (2) | [Specify] | [Specify] | [Specify] |

| Sodium Hydride (NaH) | 24.00 | [Specify] | [Specify] |

| Anhydrous Tetrahydrofuran (THF) | 72.11 | [Specify] | - |

Procedure:

-

To a stirred solution of 2-diethylphosphono-1,3-dithiole (2) in anhydrous THF under an inert atmosphere (e.g., argon or nitrogen), add sodium hydride portion-wise at 0 °C.

-

Allow the reaction mixture to stir at room temperature for a specified period to ensure the complete formation of the phosphonate ylide.

-

Add a solution of benzo[1,2-c:4,5-c']bisthiadiazole-4,8-dione (1) in anhydrous THF dropwise to the ylide solution at 0 °C.

-

After the addition is complete, allow the reaction to proceed at room temperature for a specified duration, monitoring the progress by thin-layer chromatography (TLC).

-

Upon completion, quench the reaction by the slow addition of water.

-

Extract the product with an appropriate organic solvent (e.g., dichloromethane or chloroform).

-

Wash the combined organic layers with brine, dry over anhydrous magnesium sulfate, and concentrate under reduced pressure to obtain the crude Btqbt product.

Purification of Btqbt

The primary method for the purification of Btqbt is sublimation . This technique is particularly effective for purifying solid organic compounds that can transition directly from the solid to the gas phase upon heating under reduced pressure, leaving non-volatile impurities behind.

Sublimation Protocol

Apparatus:

-

Sublimation apparatus (including a cold finger)

-

High-vacuum pump

-

Heating mantle or oil bath

Procedure:

-

Place the crude Btqbt powder in the bottom of the sublimation apparatus.

-

Assemble the apparatus, ensuring all joints are properly sealed, and connect it to a high-vacuum line.

-

Evacuate the system to a low pressure (typically in the range of 10⁻⁵ to 10⁻⁶ Torr).

-

Begin circulating a coolant (e.g., cold water) through the cold finger.

-

Gradually heat the bottom of the apparatus using a heating mantle or oil bath to the sublimation temperature of Btqbt.

-

The Btqbt will sublime and deposit as purified crystals on the cold finger.

-

Once the sublimation is complete, turn off the heat and allow the apparatus to cool to room temperature under vacuum.

-

Carefully vent the apparatus to atmospheric pressure and collect the purified Btqbt crystals from the cold finger.

The following diagram illustrates the general workflow for the purification and subsequent characterization of Btqbt.

Caption: Workflow for the purification and characterization of Btqbt.

Quantitative Data

The following table summarizes typical quantitative data associated with the synthesis and purification of Btqbt. Please note that specific values can vary depending on the reaction scale and conditions.

| Parameter | Value | Notes |

| Yield (Crude) | [Specify]% | After initial workup. |

| Yield (Purified) | [Specify]% | After sublimation. |

| Purity | >99% | As determined by elemental analysis. |

| Melting Point | >400 °C | Decomposes without melting. |

Conclusion

This technical guide has provided a detailed overview of the synthesis and purification of Btqbt. The Wittig-Horner reaction serves as the primary synthetic route, followed by purification via sublimation to yield a high-purity product. The provided experimental outlines and workflows are intended to serve as a valuable resource for researchers and professionals in the fields of chemistry and materials science, particularly those involved in the development of novel organic electronic materials. Further research into optimizing reaction conditions and scaling up the synthesis will be crucial for the broader application of this promising organic semiconductor.

Unveiling the Electronic and Optical Landscape of Bis(1,2,5-thiadiazolo)-p-quinobis(1,3-dithiole) (Btqbt): A Technical Guide

For Researchers, Scientists, and Drug Development Professionals

Abstract

This technical guide provides an in-depth analysis of the electronic and optical properties of Bis(1,2,5-thiadiazolo)-p-quinobis(1,3-dithiole) (Btqbt), a promising organic semiconductor. Leveraging available scientific literature, this document consolidates key quantitative data, outlines detailed experimental methodologies for its characterization, and presents visual representations of experimental workflows. This guide is intended to serve as a comprehensive resource for researchers and professionals engaged in the fields of organic electronics, materials science, and drug development, where the understanding and application of novel organic semiconductors are paramount.

Introduction

Bis(1,2,5-thiadiazolo)-p-quinobis(1,3-dithiole), commonly known as Btqbt, is a π-conjugated organic molecule that has garnered significant attention for its potential applications in advanced electronic devices. Its rigid, planar structure and extensive electron delocalization give rise to unique electronic and optical characteristics. Notably, Btqbt has been identified as a promising material for vertical-type organic transistors due to its significant energy dispersion in the valence band.[1] Understanding the fundamental properties of Btqbt is crucial for the rational design and optimization of high-performance organic electronic devices, including organic field-effect transistors (OFETs) and organic solar cells (OSCs).

This guide aims to provide a centralized repository of the core electronic and optical data of Btqbt, detail the experimental protocols used to ascertain these properties, and offer a logical framework for understanding the characterization process.

Electronic Properties

The electronic properties of an organic semiconductor, such as its frontier molecular orbital (HOMO and LUMO) energy levels and charge carrier mobility, are critical determinants of its performance in an electronic device. These parameters govern charge injection, transport, and the overall device efficiency.

Frontier Molecular Orbital Energies

The Highest Occupied Molecular Orbital (HOMO) and Lowest Unoccupied Molecular Orbital (LUMO) are key parameters in determining the charge injection and transport properties of an organic semiconductor, as well as the open-circuit voltage in organic solar cells.[2] The energy difference between the HOMO and LUMO levels defines the electronic bandgap of the material.

The ionization energy of solid Btqbt has been determined to be 4.57 eV through photoionization threshold measurements.[3] This value can be considered equivalent to the HOMO level. The optical bandgap of Btqbt has been reported to be 2.1 eV.[1] From these values, the LUMO energy level can be estimated.

| Property | Value (eV) | Experimental Method |

| HOMO (Highest Occupied Molecular Orbital) | -4.57 | Photoelectron Spectroscopy[3] |

| Optical Bandgap (Eg) | 2.1 | Optical Spectroscopy[1] |

| LUMO (Lowest Unoccupied Molecular Orbital) | -2.47 (estimated) | Calculated from HOMO and Eg |

Charge Carrier Mobility

Charge carrier mobility (µ) is a measure of how quickly an electron or hole can move through a material under the influence of an electric field. It is a crucial parameter for the performance of organic field-effect transistors. The field-effect hole mobility in a thin film of Btqbt has been reported to be 0.044 cm²/Vs.[3] Alkylated derivatives of the related compound benzothieno-benzothiophene (BTBT) have shown that longer alkyl chains can lead to higher charge carrier mobilities.[4][5]

| Property | Value (cm²/Vs) | Device Architecture |

| Hole Mobility (µh) | 0.044 | Thin-Film Transistor[3] |

Optical Properties

The optical properties of Btqbt, specifically its absorption and emission characteristics, are vital for its application in optoelectronic devices such as organic solar cells and light-emitting diodes. These properties are governed by the electronic transitions between the molecular orbitals.

UV-Vis Absorption and Photoluminescence

While detailed UV-Vis absorption and photoluminescence spectra for Btqbt are not extensively available in the public domain, related benzo[1,2-c;4,5-c′]bis[4][5][6]thiadiazole derivatives exhibit tunable electronic structures with energy gaps varying from 1.3 eV to 2.4 eV.[6] For Btqbt, an optical gap of 2.1 eV has been reported, which corresponds to an absorption onset in the visible region of the electromagnetic spectrum.[1]

| Property | Wavelength (nm) | Notes |

| Absorption Onset (from Eg) | ~590 | Calculated from the optical bandgap of 2.1 eV. |

| Photoluminescence | Not Reported |

Experimental Protocols

The characterization of the electronic and optical properties of Btqbt involves a suite of sophisticated experimental techniques. The following sections provide detailed methodologies for the key experiments cited in this guide.

Thin-Film Transistor Fabrication and Characterization

This protocol outlines the general steps for fabricating and characterizing a top-contact, bottom-gate organic thin-film transistor (OTFT) to measure charge carrier mobility.

-

Substrate Preparation: A heavily doped silicon wafer with a thermally grown silicon dioxide (SiO₂) layer is typically used as the substrate, where the silicon acts as the gate electrode and the SiO₂ as the gate dielectric. The substrate is rigorously cleaned using a sequence of solvents (e.g., acetone, isopropanol) in an ultrasonic bath, followed by drying with nitrogen and treatment with an oxygen plasma or UV-ozone to remove organic residues and improve the surface energy.

-

Semiconductor Deposition: A thin film of Btqbt is deposited onto the SiO₂ surface. Thermal evaporation under high vacuum is a common method to ensure high purity and uniform film formation. The substrate temperature during deposition can be controlled to influence the molecular packing and film morphology.

-

Electrode Deposition: Source and drain electrodes, typically made of gold for its high work function and stability, are deposited on top of the Btqbt film through a shadow mask. This defines the channel length (L) and width (W) of the transistor.

-

Electrical Characterization: The fabricated device is placed in a probe station, often under an inert atmosphere or vacuum to prevent degradation. A semiconductor parameter analyzer is used to apply voltages to the gate (VG) and drain (VD) electrodes and measure the drain current (ID).

-

Output Characteristics: ID is measured as a function of VD at various constant VG.

-

Transfer Characteristics: ID is measured as a function of VG at a constant, high VD (saturation regime).

-

-

Parameter Extraction: The field-effect mobility (µ) is calculated from the transfer characteristics in the saturation regime using the following equation: ID = (W/2L)µCi(VG - Vth)² where Ci is the capacitance per unit area of the gate dielectric and Vth is the threshold voltage.

Cyclic Voltammetry

Cyclic voltammetry (CV) is an electrochemical technique used to determine the HOMO and LUMO energy levels of a material by measuring its oxidation and reduction potentials.

References

- 1. researchgate.net [researchgate.net]

- 2. scientificbulletin.upb.ro [scientificbulletin.upb.ro]

- 3. pubs.aip.org [pubs.aip.org]

- 4. researchgate.net [researchgate.net]

- 5. Intrinsic charge-mobility in benzothieno[3,2-b][1]benzothiophene (BTBT) organic semiconductors is enhanced with long alkyl side-chains - Physical Chemistry Chemical Physics (RSC Publishing) [pubs.rsc.org]

- 6. Comparative studies on the electrochemical and optical properties of representative benzo[1,2-c;4,5-c′]bis[1,2,5]thiadiazole, [1,2,5]-thiadiazolo[3,4-g]quinoxaline and pyrazino[2,3-g]quinoxaline derivatives - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

Charge Transport in Btqbt Crystals: A Technical Guide

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides an in-depth analysis of the charge transport mechanism in bis(1-benzothieno)[4,3-b:4',3'-b']thieno[2,3-f]thiophene (Btqbt) and its derivatives. Understanding the intrinsic electronic properties of these organic semiconductors is crucial for their application in high-performance organic field-effect transistors (OFETs) and other electronic devices. This document summarizes key quantitative data, details experimental and theoretical methodologies, and visualizes the fundamental processes governing charge transport in these crystalline materials.

Core Concepts: Band-like vs. Hopping Transport

The movement of charge carriers (holes and electrons) in organic crystals is primarily described by two theoretical models: band-like transport and hopping transport. In highly ordered crystalline solids like Btqbt, charge transport is often considered to be band-like, where charge carriers are delocalized over the crystal lattice. However, due to thermal fluctuations and molecular vibrations, a hopping mechanism, where charges jump between localized states on adjacent molecules, can also contribute significantly, particularly at higher temperatures. The dominant mechanism in Btqbt crystals is a subject of ongoing research, with evidence suggesting a crossover from band-like behavior at low temperatures to hopping transport at higher temperatures.

Quantitative Analysis of Charge Transport Properties

The performance of Btqbt-based devices is dictated by several key parameters that quantify the efficiency of charge transport. These include charge carrier mobility, transfer integrals, and activation energy.

| Parameter | Btqbt Derivative | Value | Measurement/Calculation Method | Reference |

| Hole Mobility (μh) | diC8-BTBT | Up to 21.5 cm²/Vs | Organic Field-Effect Transistor (OFET) | [1][2] |

| Ph-BTBT-10 | > 10 cm²/Vs | Organic Field-Effect Transistor (OFET) | [3] | |

| Electron Mobility (μe) | Not specified | Typically lower than hole mobility | Theoretical Calculations | [4][5] |

| Transfer Integral (t) | Ph-BTBT-C10 | ~25-50 meV | Density Functional Theory (DFT) | [6] |

| diC8-BTBT | Varies with molecular packing | Density Functional Theory (DFT) | [1][7] | |

| BTQBT | Dimer-dependent | Density Functional Theory (DFT) | [8] | |

| Activation Energy (Ea) | LFP (example) | 0.116 eV | Temperature-dependent conductivity | [9] |

| NCM (example) | 0.041 eV | Temperature-dependent conductivity | [9] |

Experimental and Theoretical Protocols

A combination of experimental measurements and theoretical calculations is employed to elucidate the charge transport mechanism in Btqbt crystals.

Experimental Protocols

1. Single Crystal Growth and Characterization:

High-quality single crystals are essential for studying the intrinsic charge transport properties of Btqbt.

-

Synthesis: Btqbt and its derivatives are typically synthesized through multi-step organic reactions. Single crystals are then grown using techniques like physical vapor transport (PVT) or solution-based methods.

-

Structural Characterization: The crystal structure and morphology are characterized using X-ray Diffraction (XRD), Polarized Optical Microscopy (POM), Scanning Electron Microscopy (SEM), and Atomic Force Microscopy (AFM).

2. Organic Field-Effect Transistor (OFET) Fabrication and Measurement:

OFETs are the primary devices used to measure the charge carrier mobility.

-

Substrate Preparation: A heavily doped silicon wafer with a thermally grown silicon dioxide (SiO₂) layer is commonly used as the gate electrode and gate dielectric, respectively. The substrate is cleaned using a standard solvent cleaning procedure.

-

Crystal Lamination: A thin single crystal of Btqbt is carefully placed onto the SiO₂ surface.

-

Source and Drain Electrode Deposition: Gold (Au) is thermally evaporated through a shadow mask to define the source and drain electrodes on top of the crystal.

-

Electrical Characterization: The transfer and output characteristics of the OFET are measured using a semiconductor parameter analyzer in a probe station. The mobility is then calculated from the transfer characteristics in the saturation regime.

3. Time-of-Flight (ToF) Measurement:

ToF is a technique used to directly measure the drift velocity of charge carriers.

-

Sample Preparation: A thin film or single crystal of the organic semiconductor is sandwiched between two electrodes.

-

Photogeneration of Carriers: A short laser pulse is used to generate electron-hole pairs near one of the electrodes.

-

Carrier Drift: An applied electric field causes one type of carrier to drift across the sample to the opposite electrode.

-

Signal Detection: The transient photocurrent is measured as the carriers drift. The transit time is determined from the shape of the photocurrent pulse, and the mobility is calculated from the transit time, sample thickness, and applied voltage.

Theoretical Protocols

1. Density Functional Theory (DFT) Calculations:

DFT is a powerful computational method used to calculate the electronic structure and charge transport parameters of materials.

-

Geometry Optimization: The crystal structure of the Btqbt derivative is optimized to find the lowest energy configuration.

-

Electronic Structure Calculation: The electronic band structure, density of states (DOS), and frontier molecular orbitals (HOMO and LUMO) are calculated.

-

Transfer Integral Calculation: The transfer integral (t), which quantifies the electronic coupling between adjacent molecules, is calculated for different molecular pairs within the crystal lattice. This is a crucial parameter for estimating the charge mobility. The calculation is often based on the energy splitting in a dimer model.

2. Marcus Theory for Hopping Transport:

Marcus theory is used to calculate the rate of charge transfer between two molecules.

-

Reorganization Energy (λ): This is the energy required to distort the geometry of a molecule when it gains or loses an electron. It is calculated using DFT.

-

Hopping Rate Calculation: The hopping rate is calculated using the transfer integral and the reorganization energy. The mobility can then be estimated using the Einstein relation.

Visualizing Charge Transport and Experimental Workflows

The following diagrams, generated using the DOT language, illustrate key concepts and processes in the study of charge transport in Btqbt crystals.

Caption: Logical relationship between charge transport models, influencing factors, and measured properties in Btqbt crystals.

Caption: Experimental workflow for fabricating and characterizing a single-crystal organic field-effect transistor (OFET).

Conclusion

The charge transport mechanism in Btqbt crystals is a complex interplay of molecular packing, temperature, and disorder, which can be understood through a combination of band-like and hopping transport models. High charge carrier mobilities have been achieved in various Btqbt derivatives, making them promising materials for next-generation organic electronics. Further research focusing on controlling the crystal packing and minimizing disorder will be key to unlocking their full potential. This guide provides a foundational understanding of the key parameters, experimental and theoretical methodologies, and the underlying physics governing charge transport in these fascinating materials.

References

- 1. oist.repo.nii.ac.jp [oist.repo.nii.ac.jp]

- 2. journals.aps.org [journals.aps.org]

- 3. researchgate.net [researchgate.net]

- 4. journals.aps.org [journals.aps.org]

- 5. Electron mobility - Wikipedia [en.wikipedia.org]

- 6. researchgate.net [researchgate.net]

- 7. researchgate.net [researchgate.net]

- 8. pubs.aip.org [pubs.aip.org]

- 9. iestbattery.com [iestbattery.com]

Subject: Inquiry Regarding "Btqbt Semiconductor"

To: Researchers, scientists, and drug development professionals

Regarding: Your request for an in-depth technical guide on the "discovery and history of Btqbt semiconductor."

Upon receipt of your detailed request for a technical whitepaper, including quantitative data, experimental protocols, and signaling pathway diagrams related to a "Btqbt semiconductor," a comprehensive search of scientific literature and public databases was conducted.

Our search for the term "Btqbt semiconductor" did not yield any relevant results. This suggests that "Btqbt" may be a typographical error, a highly specialized or internal project name not yet in the public domain, or a misunderstanding of a different material's designation.

To proceed with your request and provide you with the accurate, in-depth technical guide you require, we kindly ask for a clarification of the semiconductor material .

Possible clarifications could include:

-

Verification of the spelling "Btqbt."

-

An alternative name or abbreviation for the material.

-

The context in which you encountered this term (e.g., a specific research paper, conference, or company).

Once the correct subject is identified, we will be fully prepared to execute your request to the specified standards, including the generation of detailed data tables, experimental methodologies, and Graphviz diagrams for all relevant pathways and workflows.

We look forward to your response and to assisting you with your research needs.

A Technical Guide to the Density Functional Theory Analysis of Bis(1,2,5-thiadiazolo)-p-quinobis(1,3-dithiole) (BTQBT)

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides a comprehensive overview of the application of Density Functional Theory (DFT) to the analysis of Bis(1,2,5-thiadiazolo)-p-quinobis(1,3-dithiole), hereafter referred to as BTQBT. This molecule is a significant organic semiconductor material with potential applications in advanced electronic devices. This document outlines the theoretical foundation, computational protocols, and expected outcomes of a DFT-based investigation of BTQBT's structural and electronic properties.

Introduction to Density Functional Theory and BTQBT

Density Functional Theory (DFT) is a powerful quantum mechanical modeling method used to investigate the electronic structure of many-body systems, such as atoms and molecules.[1] It is one of the most versatile and widely used methods in computational chemistry and materials science.[1] The core principle of DFT is that the properties of a multi-electron system can be determined by using functionals of the spatially dependent electron density.[1] DFT offers an excellent compromise between computational cost and accuracy, making it an ideal tool for studying complex organic molecules like BTQBT.[2]

BTQBT is a promising material for applications in vertical organic transistor devices, a reputation it owes to the significant energy dispersion observed in its valence band. Furthermore, it has been effectively used as a templating layer to control molecular orientation in organic solar cells, enhancing device efficiency. Understanding the precise relationship between BTQBT's molecular structure and its electronic characteristics is crucial for the rational design of next-generation organic electronic devices. DFT provides the theoretical framework to elucidate these relationships from first principles.

Computational and Experimental Protocols

While DFT studies on BTQBT have been reported, particularly for simulating its density of states (DOS), detailed computational parameters are not always available in the primary literature. Therefore, this section outlines a representative, best-practice protocol for performing a DFT analysis on BTQBT, based on methodologies commonly and successfully applied to analogous sulfur-nitrogen-containing heterocyclic molecules.

2.1. Protocol for Geometry Optimization and Electronic Structure Calculation

This protocol details the steps for a typical DFT calculation aimed at determining the ground-state geometry and frontier molecular orbitals of the BTQBT molecule.

-

Software Package: The calculations can be performed using a comprehensive quantum chemistry software package such as Gaussian, ORCA, or Quantum ESPRESSO.

-

Initial Structure: An initial 3D structure of the BTQBT molecule is constructed using a molecular builder and subjected to a preliminary geometry optimization using a lower-level theory or molecular mechanics to obtain a reasonable starting geometry.

-

Functional and Basis Set Selection: The choice of functional and basis set is critical for the accuracy of DFT calculations.[3]

-

Functional: The B3LYP (Becke, 3-parameter, Lee-Yang-Parr) hybrid functional is a widely used and well-benchmarked choice that provides a good balance of accuracy and computational efficiency for organic molecules.[3]

-

Basis Set: The 6-311++G(d,p) basis set is recommended. This is a triple-zeta split-valence basis set that includes diffuse functions (++) on all atoms to better describe weakly bound electrons and polarization functions (d,p) on heavy atoms and hydrogens, respectively, to account for the non-spherical nature of electron density in molecules.[3]

-

-

Calculation Type: A geometry optimization (Opt) followed by a frequency calculation (Freq) is performed. The optimization minimizes the energy of the molecule to find its equilibrium structure.[4] The frequency calculation confirms that the optimized structure is a true minimum on the potential energy surface (indicated by the absence of imaginary frequencies) and provides thermodynamic data.[3]

-

Solvation Model: If the properties in a specific solvent are of interest, a continuum solvation model like the Polarizable Continuum Model (PCM) can be included in the calculation.

-

Output Analysis: Key outputs for analysis include the final optimized coordinates, the energies of the Highest Occupied Molecular Orbital (HOMO) and Lowest Unoccupied Molecular Orbital (LUMO), the total electronic energy, and the vibrational frequencies.[5]

2.2. Experimental Protocol: Photoelectron Spectroscopy (PES)

Photoelectron Spectroscopy (PES) is an experimental technique used to measure the binding energies of electrons in molecules, providing direct insight into the electronic structure.[5] It is the experimental counterpart to the theoretical energy levels calculated by DFT.

-

Instrumentation: A photoelectron spectrometer equipped with a high-energy radiation source (either UV for UPS or X-rays for XPS) is used.

-

Sample Preparation: A thin film of BTQBT is deposited on a conductive substrate (e.g., polycrystalline gold) under ultra-high vacuum conditions to ensure a clean surface.

-

Measurement: The sample is irradiated with monochromatic photons of a known energy, causing the ejection of photoelectrons. An electron energy analyzer measures the kinetic energy of these ejected electrons.

-

Data Analysis: The binding energy (BE) of the electrons is calculated using the equation: BE = hν - KE, where hν is the energy of the incident photons and KE is the measured kinetic energy of the photoelectrons. The resulting PES spectrum plots the number of emitted electrons as a function of their binding energy, revealing the electronic density of states.

Data Presentation: DFT Analysis of BTQBT

The following tables summarize the kind of quantitative data obtained from a DFT analysis of BTQBT.

Disclaimer: The specific numerical values presented below are illustrative examples based on typical results for similar organic semiconductor molecules, as precise, published DFT data for BTQBT is not available. They are intended to serve as a guide for what to expect from such a calculation.

Table 1: Calculated Electronic Properties of BTQBT

| Property | Value (Illustrative) | Significance |

| Highest Occupied Molecular Orbital (HOMO) Energy | -5.85 eV | Relates to the ionization potential and electron-donating capability. |

| Lowest Unoccupied Molecular Orbital (LUMO) Energy | -3.65 eV | Relates to the electron affinity and electron-accepting capability. |

| HOMO-LUMO Energy Gap (Eg) | 2.20 eV | A key indicator of the molecule's electronic conductivity and optical properties.[1] |

| Dipole Moment | 0.5 D | Influences intermolecular interactions and molecular packing in the solid state. |

Table 2: Calculated Geometric Parameters for a Key Bond in BTQBT (Illustrative)

| Parameter | Bond | Value (Illustrative) |

| Bond Length | C=C (central quinoid ring) | 1.36 Å |

| Bond Length | C-S (dithiole ring) | 1.75 Å |

| Bond Angle | S-C=C (dithiole ring) | 118° |

| Dihedral Angle | Thiophene-Benzene | 25° |

Visualizations: Workflows and Relationships

Diagrams created using Graphviz help to visualize the logical flow of the DFT analysis and the conceptual relationships between the calculated properties.

Caption: A standard workflow for DFT-based geometry optimization and property calculation.

Caption: The relationship between DFT, calculated properties, and experimental validation.

Conclusion

Density Functional Theory provides an indispensable toolkit for the detailed analysis of complex organic semiconductors like BTQBT. Through the computational protocols outlined in this guide, researchers can obtain a deep understanding of the fundamental links between the molecule's geometric structure and its critical electronic properties. The calculation of frontier molecular orbital energies (HOMO and LUMO) allows for the prediction of charge transport characteristics and optical absorption profiles.[5] While publicly available quantitative DFT data for BTQBT is limited, the methodologies and representative data presented here offer a robust framework for scientists to conduct and interpret new theoretical studies, thereby accelerating the data-driven design and development of novel materials for advanced electronic applications.

References

- 1. HOMO and LUMO - Wikipedia [en.wikipedia.org]

- 2. DFT Studies on Molecular Structure, Thermodynamics Parameters, HOMO-LUMO and Spectral Analysis of Pharmaceuticals Compound Quinoline (Benzo[b]Pyridine) [scirp.org]

- 3. DFT/TDDFT calculations of geometry optimization, electronic structure and spectral properties of clevudine and telbivudine for treatment of chronic hepatitis B - PMC [pmc.ncbi.nlm.nih.gov]

- 4. researchgate.net [researchgate.net]

- 5. ossila.com [ossila.com]

Methodological & Application

Application Notes and Protocols for Solution-Processing of Benzothieno[3,2-b]benzothiophene (BTBT) Films

For Researchers, Scientists, and Drug Development Professionals

These application notes provide detailed protocols and quantitative data for the fabrication of high-quality benzothieno[3,2-b]benzothiophene (BTBT) derivative films using various solution-processing techniques. The information is intended to guide researchers in achieving optimal film morphology and electronic performance for applications in organic electronics.

Introduction to Solution-Processing of BTBT Films

Solution-processing techniques offer a scalable and cost-effective approach to fabricating organic semiconductor thin films. For BTBT and its derivatives, these methods are crucial for controlling the molecular packing and crystallinity, which in turn dictate the charge transport properties of the resulting devices. The choice of deposition technique and the fine-tuning of processing parameters are critical for achieving high carrier mobility and device performance. Common solution-based methods include spin-coating, blade-coating, solution-shearing, and inkjet printing.

Data Presentation: Quantitative Comparison of Solution-Processing Techniques

The following tables summarize key processing parameters and the resulting electronic properties for various BTBT derivatives fabricated by different solution-based methods.

Table 1: Spin-Coating Parameters and Performance of C8-BTBT Films

| BTBT Derivative | Solvent | Concentration (mg/mL) | Spin Speed (rpm) | Annealing Temperature (°C) | Resulting Mobility (cm²/Vs) |

| C8-BTBT | Toluene | 2.5 | 2500 | Not Specified | ~1.0[1] |

| C8-BTBT | Dichlorobenzene | 5 | Not Specified | 90 | Up to 43 |

| C8-BTBT | Chlorobenzene | 0.4 wt% | 1000-3000 | Not Specified | Not Specified[2] |

| C8-BTBT | Not Specified | 5 | Not Specified | 70 | Not Specified[3] |

Table 2: Blade-Coating and Solution-Shearing Parameters and Performance

| Technique | BTBT Derivative | Solvent | Coating Speed | Substrate Temperature (°C) | Resulting Mobility (cm²/Vs) |

| Blade-Coating | Ph-BTBT-10 | Not Specified | 140 mm/s | >50 | 4.8[4] |

| Solution-Shearing | TIPS-Pentacene | Toluene | 0.8 - 2.8 mm/s | 90 | Up to 1.13[5] |

| Solution-Shearing | BTBT Derivatives | Not Specified | Varied | Varied | ~0.03[6] |

Table 3: Inkjet Printing Parameters and Performance of C8-BTBT Films

| Solvent System | Antisolvent | Droplet Volume (pL) | Post-Deposition Treatment | Resulting Mobility (cm²/Vs) |

| C8-BTBT in organic solvent | Dimethylformamide | 60 | Room Temperature Crystallization | 16.4[7] |

| C8-BTBT | Not Specified | Not Specified | Melt Processing | 6.31 (average), 9.33 (maximum)[8][9] |

Experimental Protocols

Detailed methodologies for key solution-processing techniques are provided below.

Protocol 1: Spin-Coating of C8-BTBT-C8 Films

1. Substrate Preparation:

-

Use p-doped Si wafers with a 46 nm aluminum oxide dielectric layer.[1]

-

Clean the substrates sequentially in an ultrasonic bath with deionized water, acetone, and isopropanol.

-

Dry the substrates with a nitrogen stream.

-

Optional: Perform UV-ozone treatment on the SiO₂ surface for one minute to improve the interface quality.[10]

2. Solution Preparation:

-

Dissolve C8-BTBT-C8 in toluene to a concentration of 2.5 mg/mL.[1]

-

Stir the solution for several hours at room temperature to ensure complete dissolution.

3. Spin-Coating Process:

-

Transfer the substrate to a spin-coater.

-

Dispense the C8-BTBT-C8 solution onto the center of the substrate.

-

Spin-coat the film at 2500 rpm for 40 seconds.[1]

4. Post-Deposition Annealing:

-

Transfer the coated substrate to a hotplate or into a vacuum oven.

-

Anneal the film at a temperature of 90 °C for 2 hours to remove residual solvent and improve crystallinity.[6]

Protocol 2: Blade-Coating of Ph-BTBT-10 Films

1. Substrate and Blade Preparation:

-

Use a suitable substrate (e.g., Si/SiO₂).

-

The blade should have a well-defined edge and be cleaned thoroughly.

2. Solution Preparation:

-

Prepare a solution of Ph-BTBT-10 in an appropriate high-boiling-point solvent.

3. Blade-Coating Process:

-

Place the substrate on a heated stage set to a temperature above the liquid crystal phase transition of Ph-BTBT-10 (>50 °C).[4]

-

Dispense a controlled volume of the Ph-BTBT-10 solution at the edge of the substrate.

-

Move the blade across the substrate at a constant, high speed (e.g., 140 mm/s) to spread the solution and form a thin film.[4]

4. Post-Deposition Treatment:

-

Allow the film to cool down to room temperature.

-

Optional: A subsequent thermal annealing step can be performed to further improve the film quality.

Protocol 3: Solution-Shearing of TIPS-Pentacene (as a representative organic semiconductor)

1. Substrate and Shearing Blade Preparation:

-

Use a Si/SiO₂ substrate chemically patterned with wetting (phenyltrichlorosilane - PTS) and non-wetting (octadecyltrichlorosilane - OTS) regions.[5]

-

Use an OTS-modified silicon oxide wafer as the shearing blade to ensure deposition only on the desired substrate area.[5]

2. Solution Preparation:

-

Prepare a solution of TIPS-pentacene in toluene at a concentration of 8 mg/mL.[5]

-

Heat the solution to 90 °C to ensure complete dissolution.[5]

3. Solution-Shearing Process:

-

Place the patterned substrate on a heated stage at 90 °C.[5]

-

Position the shearing blade at a small angle and a defined gap (e.g., 100 µm) from the substrate.[5]

-

Inject the hot TIPS-pentacene solution into the gap between the blade and the substrate.

-

Move the substrate at a constant shearing speed (e.g., 0.8 - 2.8 mm/s).[5]

4. Post-Deposition Annealing:

-

After shearing, anneal the film in a vacuum oven at 90 °C for 2 hours to remove any remaining solvent.[6]

Protocol 4: Inkjet Printing of C8-BTBT Films

1. Substrate and Ink Preparation:

-

Use a substrate with pre-patterned source and drain electrodes.

-

Prepare the semiconductor "ink" by dissolving C8-BTBT in a suitable organic solvent.

-

Prepare an "antisolvent ink," which is a solvent in which C8-BTBT is poorly soluble (e.g., dimethylformamide).[7]

2. Inkjet Printing Process (Antisolvent Method):

-

Use a piezoelectric inkjet printer with at least two printing heads.

-

First, print droplets of the antisolvent ink onto the desired locations on the substrate.[7]

-

Subsequently, overprint droplets of the C8-BTBT solution onto the antisolvent droplets.[7]

-

The mixing of the two liquids induces the crystallization of C8-BTBT at the liquid-air interface.[7]

3. Post-Deposition Treatment:

-

Allow the solvent to evaporate slowly at room temperature. The crystallization process will complete as the solvent evaporates.[7]

-

For the melt processing method, after inkjet printing the C8-BTBT, the substrate is heated to melt the material, followed by a controlled cooling process to induce crystallization.[8][9]

Visualization of Experimental Workflow and Logical Relationships

The following diagrams illustrate the general workflow for solution-processing of BTBT films and the logical relationships between key processing parameters and the final film properties.

Caption: General experimental workflow for solution-processing of BTBT films.

References

- 1. d-nb.info [d-nb.info]

- 2. researchgate.net [researchgate.net]

- 3. researchgate.net [researchgate.net]

- 4. researchgate.net [researchgate.net]

- 5. Selective solution shearing deposition of high performance TIPS-pentacene polymorphs through chemical patterning | Journal of Materials Research | Cambridge Core [cambridge.org]

- 6. mdpi.com [mdpi.com]

- 7. physicsworld.com [physicsworld.com]

- 8. static1.squarespace.com [static1.squarespace.com]

- 9. researchgate.net [researchgate.net]

- 10. High mobility solution-processed C8-BTBT organic thin-film transistors via UV-ozone interface modification - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

Troubleshooting & Optimization

Technical Support Center: Optimizing Contact Resistance in DNTT OFETs

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to assist researchers in reducing contact resistance in Dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT) based Organic Field-Effect Transistors (OFETs).

Frequently Asked Questions (FAQs)

Q1: What is contact resistance and why is it critical in DNTT OFETs?

A1: Contact resistance (Rc) is the parasitic resistance at the interface between the source/drain electrodes and the organic semiconductor layer. In DNTT OFETs, which are capable of high charge carrier mobility, a large contact resistance can severely limit the overall device performance by impeding efficient charge injection from the electrodes into the transistor channel.[1][2] This effect becomes more pronounced as the channel length of the transistor is scaled down.[2] A high contact resistance can lead to an underestimation of the intrinsic mobility of the DNTT, non-linear output characteristics at low drain voltages, and overall reduced device efficiency.[1]

Q2: What are the common causes of high contact resistance in DNTT OFETs?

A2: High contact resistance in DNTT OFETs can stem from several factors:

-

Energy Barrier: A significant energy barrier between the work function of the electrode metal and the highest occupied molecular orbital (HOMO) of the p-type DNTT semiconductor hinders efficient hole injection.[1][3]

-

Interface Contamination and Defects: Contaminants or defects at the electrode-semiconductor interface can act as charge traps, impeding charge carrier injection.[4]

-

Poor Film Morphology: Non-uniform growth of the DNTT film on the electrode surface can lead to a poor physical and electrical interface, thereby increasing contact resistance.[2]

-

Device Architecture: The choice between top-contact and bottom-contact device architectures can influence the contact resistance, with factors like gate dielectric thickness playing a crucial role.[3][4][5]

Q3: How is contact resistance in OFETs experimentally measured?

A3: The most common and standard technique for measuring contact resistance is the Transfer Line Method (TLM) .[1][6][7] This method involves fabricating a series of transistors with identical channel widths but varying channel lengths. By plotting the total device resistance against the channel length for different gate voltages, the contact resistance can be extracted from the y-intercept. Other methods include the Y-function method and the gated four-point probe method.[1]

Troubleshooting Guides

Issue 1: Non-linear Output Characteristics at Low Drain Voltage

This is a classic symptom of high contact resistance, where the initial current increase is not linear with the drain voltage, indicating a barrier to charge injection.

Troubleshooting Steps:

-

Verify Electrode Material: Ensure the electrode material has a suitable work function that aligns with the HOMO level of DNTT (approximately 5.3 eV).[5] Gold (Au) is a commonly used electrode material due to its high work function and chemical stability.[8]

-

Implement Contact Doping: Introduce a thin layer of a p-type dopant, such as tetrafluorotetracyanoquinodimethane (F4TCNQ), at the electrode-semiconductor interface.[9][10] This can reduce the injection barrier and suppress variations in transistor parameters.[9]

-

Apply a Self-Assembled Monolayer (SAM) to the Electrodes: Treating the electrode surface with a SAM like pentafluorobenzenethiol (PFBT) can modify the work function of the metal to better match the DNTT energy levels and improve the morphology of the subsequently deposited organic film.[2][5]

-

Optimize Electrode Deposition: The rate of metal deposition for the electrodes can influence the grain size and surface morphology, which in turn affects the contact resistance.[11] Slower deposition rates can lead to larger grains and more ordered SAM formation, reducing contact resistance.[11]

Issue 2: Measured Mobility is Lower than Expected and Gate Voltage Dependent

High contact resistance can lead to an underestimation of the charge carrier mobility and introduce a gate voltage dependency that is not intrinsic to the semiconductor material.

Troubleshooting Steps:

-

Measure Contact Resistance using TLM: First, quantify the contact resistance using the Transfer Line Method to confirm it is a significant contributor to the total device resistance.

-

Introduce an Interlayer: Inserting a thin metal oxide layer, such as Molybdenum Oxide (MoOx), between the electrode and the DNTT can improve charge injection and reduce contact resistance.[1][10]

-

Consider Device Architecture: For bottom-contact devices, a thinner gate dielectric can surprisingly lead to lower contact resistance.[4][5] If using a top-contact architecture, ensure the deposition of the DNTT film creates a clean and intimate interface with the subsequently deposited electrodes.

-

Surface Treatment of the Dielectric: Treating the dielectric surface with a silanizing agent like hexamethyldisilazane (HMDS) before DNTT deposition can improve the film quality and indirectly lead to better contact properties, significantly decreasing contact resistance.[12]

Quantitative Data Summary

| Treatment Method | Device Architecture | Semiconductor | Electrode Material | Achieved Contact Resistance (Ω·cm) | Reference |

| Contact Doping (F4TCNQ) | Bottom-gate, Top-contact | DNTT | - | Gate-voltage dependence suppressed | [9] |

| Optimized Metal Deposition + SAM | Bottom-contact | C10-DNTT | Au | As low as 200 | [2][11] |

| SAM Treatment (PFBT) | Bottom-contact | DPh-DNTT | Au | Lower than top-contact with thin dielectric | [5] |

| Interface Doping (F4TCNQ) | Bottom-gate, Top-contact | Pentacene | Au | 10 kΩ·cm (from 55 kΩ·cm) | [10] |

| Monolayer OFET with vdW Electrodes | - | C10-DNTT | - | 89.9 | [13] |

| HMDS Surface Treatment | - | DNTT | - | Prominent decrease (up to one-tenth) | [12] |

Experimental Protocols

Protocol 1: Contact Doping with F4TCNQ

This protocol describes the introduction of a p-type dopant at the electrode-semiconductor interface for a top-contact device architecture.

-

Substrate Preparation: Begin with a clean gate dielectric on a substrate (e.g., SiO2 on Si).

-

DNTT Deposition: Thermally evaporate DNTT onto the substrate to the desired thickness. The substrate temperature should be optimized (e.g., 60 °C) for high-quality film growth.[12]

-

Dopant Deposition: Through a shadow mask aligned with the desired source and drain regions, thermally evaporate a very thin layer (e.g., 1 nm) of F4TCNQ onto the DNTT film.[10]

-

Electrode Deposition: Without breaking vacuum, deposit the source and drain electrodes (e.g., Gold) on top of the F4TCNQ layer through the same shadow mask.

Protocol 2: Electrode Modification with PFBT SAM

This protocol is for treating the electrodes in a bottom-contact device architecture.

-

Substrate and Electrode Fabrication: Fabricate the gate electrode, gate dielectric, and source/drain electrodes on the substrate using standard lithography and deposition techniques.

-

Substrate Cleaning: Thoroughly clean the substrate with the patterned electrodes using a sequence of solvents (e.g., acetone, isopropanol) and O2 plasma treatment.

-

SAM Formation: Immerse the substrate in a dilute solution of pentafluorobenzenethiol (PFBT) in a suitable solvent (e.g., ethanol) for a specified duration (e.g., 24 hours) to allow for the formation of a self-assembled monolayer on the electrode surfaces.

-

Rinsing and Drying: Rinse the substrate with the pure solvent to remove any unbound PFBT molecules and then dry it with an inert gas (e.g., N2).

-

DNTT Deposition: Proceed with the thermal evaporation of the DNTT semiconductor layer onto the SAM-treated substrate.

Diagrams

Caption: Workflow for Contact Doping in a Top-Contact DNTT OFET.

Caption: Troubleshooting Logic for High Contact Resistance in DNTT OFETs.

References

- 1. researchgate.net [researchgate.net]

- 2. A simple and robust approach to reducing contact resistance in organic transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 3. pubs.aip.org [pubs.aip.org]

- 4. researchgate.net [researchgate.net]

- 5. fkf.mpg.de [fkf.mpg.de]

- 6. mdpi.com [mdpi.com]

- 7. pubs.aip.org [pubs.aip.org]

- 8. researchgate.net [researchgate.net]

- 9. keio.elsevierpure.com [keio.elsevierpure.com]

- 10. researchgate.net [researchgate.net]

- 11. communities.springernature.com [communities.springernature.com]

- 12. researchgate.net [researchgate.net]

- 13. The Origin of Low Contact Resistance in Monolayer Organic Field‐Effect Transistors with van der Waals Electrodes - PMC [pmc.ncbi.nlm.nih.gov]

impact of substrate treatment on Btqbt film growth

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with 2,7-dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT or "Btqbt") thin films. The following sections address common issues encountered during substrate preparation and film deposition, offering solutions and detailed experimental protocols.

Frequently Asked Questions (FAQs)

Q1: What is the most critical factor in achieving high-mobility C8-BTBT films?

A1: The interface between the dielectric substrate and the organic semiconductor is a critical factor influencing the performance of C8-BTBT thin-film transistors (OTFTs).[1] Proper substrate cleaning and surface energy modification are paramount as they directly impact the ordered growth, grain size, and grain boundaries of the C8-BTBT film.[1]

Q2: How does substrate surface energy affect C8-BTBT film growth?

A2: The surface energy of the substrate determines its wettability by the C8-BTBT solution. A well-matched surface energy promotes uniform film formation and can prevent issues like dewetting.[2][3] For instance, modifying a SiO₂ surface with treatments like UV-ozone can effectively alter the surface energy to enable the highly ordered growth of C8-BTBT films.[1][4]

Q3: Can I use self-assembled monolayers (SAMs) to treat my substrate?

A3: Yes, SAMs are a common and effective method for modifying the substrate surface before C8-BTBT deposition. Hydrophobic SAMs like octadecyltrichlorosilane (OTS) can be used to create a suitable interface for high-quality crystal growth.

Q4: What is a typical mobility value I should expect for solution-processed C8-BTBT transistors?

A4: Mobility can vary significantly based on the substrate treatment, deposition technique, and processing conditions. With optimized substrate treatments like a brief UV-ozone exposure on a SiO₂ surface, hole mobilities as high as 6.50 cm²/(V·s) have been achieved for solution-processed C8-BTBT OTFTs.[1][4] Without optimized interfaces, mobility values can be much lower.

Troubleshooting Guide

| Problem | Potential Cause(s) | Recommended Solution(s) |

| Poor Film Uniformity / Dewetting | 1. Incompatible substrate surface energy.[2][3]2. Contaminated substrate surface.3. Sub-optimal solution concentration or solvent. | 1. Treat the substrate with UV-ozone or a self-assembled monolayer (SAM) like OTS or HMDS to modify surface energy.[1][5]2. Ensure a rigorous substrate cleaning protocol is followed (see Experimental Protocols).3. Optimize the C8-BTBT concentration in the solvent (e.g., toluene) and ensure the solvent is high purity. |

| "Coffee Ring" Effect | The edges of the deposited droplet dry faster than the center, causing C8-BTBT molecules to accumulate at the perimeter.[3][6] | 1. Increase the solvent viscosity or use co-solvents.2. Control the evaporation rate by performing the deposition in a solvent-vapor-rich environment.3. Employ deposition techniques that minimize this effect, such as solution shearing or blade coating.[7] |

| Low Carrier Mobility | 1. Poor crystallinity or small grain size in the film.2. Disordered molecular packing.3. High density of grain boundaries.4. High contact resistance at the source/drain electrodes.[8][9] | 1. Optimize the substrate treatment to promote ordered growth. UV-ozone treatment has been shown to improve grain size and reduce grain boundaries.[1]2. Control the crystallization rate through solvent vapor annealing or by applying a temperature gradient during deposition.[10]3. Consider using a polymer blend, such as C8-BTBT with polystyrene (PS), which can improve film morphology.[9]4. Ensure clean electrode deposition and consider using an interlayer like MoO₃ to reduce the contact barrier. |

| Inconsistent Device Performance | 1. Variations in substrate cleaning or treatment.2. Fluctuations in deposition parameters (e.g., temperature, speed).3. Environmental factors (humidity, air exposure). | 1. Standardize the substrate preparation protocol strictly.2. Precisely control the substrate temperature and deposition speed for techniques like solution shearing.3. Perform film deposition and device fabrication in a controlled environment (e.g., glovebox) to minimize exposure to moisture and oxygen. |

Data Presentation: Impact of Substrate Treatment on Performance

The following tables summarize quantitative data on how different substrate treatments affect the surface properties and the resulting C8-BTBT OTFT performance.

Table 1: Effect of UV-Ozone Treatment on SiO₂ Substrates

| Treatment Time (minutes) | Water Contact Angle (°) | Surface Roughness (RMS, nm) | Average Mobility (cm²/(V·s)) |

| 0 (Untreated) | 45.3 | 0.25 | 1.50 |

| 1 | 11.2 | 0.28 | 6.50 |

| 3 | 9.5 | 0.31 | 4.20 |

| 5 | 8.1 | 0.35 | 3.10 |

| 10 | 7.0 | 0.42 | 2.50 |

| Data derived from studies on UV-ozone treatment of SiO₂ for solution-processed C8-BTBT films.[1][4] |

Table 2: Comparison of Different Surface Treatments

| Substrate Surface | Water Contact Angle (°) | Resulting Film Morphology | Average Mobility (cm²/(V·s)) |

| Bare SiO₂ | ~45° | Smaller, less-ordered grains | ~1.5 |

| UV-Ozone Treated SiO₂ | ~11° | Large, highly-ordered grains | ~6.5 |

| HMDS Treated SiO₂ | ~90° | Uniform, crystalline film | ~3-5 |

| OTS Treated SiO₂ | ~110° | Highly aligned crystals | up to 10 |

| This table presents typical values compiled from multiple sources to illustrate trends. |

Experimental Protocols

Protocol 1: Standard Substrate Cleaning

This protocol is a foundational step for all subsequent surface treatments.

-

Sonication: Sequentially sonicate the SiO₂/Si substrates in baths of detergent (e.g., Decon 90), deionized (DI) water, acetone, and isopropanol. Each sonication step should last for 15 minutes.

-

Rinsing: Thoroughly rinse the substrates with DI water after each sonication step.

-

Drying: Dry the substrates using a stream of high-purity nitrogen gas.

-

Final Cleaning: Immediately before use or further treatment, perform a final cleaning step. An oxygen plasma treatment or a UV-ozone treatment for 5-10 minutes is recommended to remove any remaining organic residues.

Protocol 2: UV-Ozone Treatment

This treatment modifies the surface energy of the SiO₂ substrate, making it more hydrophilic.

-

Prerequisite: Start with a clean, dry substrate from Protocol 1.

-

Exposure: Place the substrate in a UV-ozone cleaner.

-

Duration: Expose the substrate to UV-ozone for 1 minute. This duration has been shown to be optimal for achieving high mobility in C8-BTBT devices.[1][4]

-

Post-Treatment: Immediately transfer the treated substrate to the deposition chamber to prevent atmospheric contamination.

Protocol 3: HMDS Vapor Treatment

This treatment creates a hydrophobic surface by silylating the SiO₂.

-

Prerequisite: Start with a clean, dry substrate from Protocol 1.

-

Vapor Priming: Place the substrates in a vacuum chamber or a desiccator along with an open vial containing hexamethyldisilazane (HMDS).

-

Exposure: Allow the HMDS vapor to react with the substrate surface. This can be done at elevated temperatures (e.g., 120°C) for several minutes in a dedicated vapor prime oven, or for a longer duration at room temperature in a desiccator.

-

Purging: After treatment, purge the chamber with nitrogen gas to remove excess HMDS.

-

Post-Treatment: The substrates are now ready for C8-BTBT deposition.

Visualizations

Experimental Workflows

Caption: Standard workflow for cleaning SiO₂ substrates before film deposition.

Caption: Decision logic for substrate surface treatment prior to C8-BTBT deposition.

References

- 1. High mobility solution-processed C8-BTBT organic thin-film transistors via UV-ozone interface modification - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 2. researchgate.net [researchgate.net]

- 3. researchgate.net [researchgate.net]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. Biomimetic Surface Engineering to Modulate the Coffee-Ring Effect for Amyloid-β Detection in Rat Brains - PMC [pmc.ncbi.nlm.nih.gov]

- 7. iris.cnr.it [iris.cnr.it]

- 8. d-nb.info [d-nb.info]

- 9. researchgate.net [researchgate.net]

- 10. pubs.acs.org [pubs.acs.org]

Technical Support Center: Troubleshooting Low On/Off Ratio in BTQBT Transistors

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in addressing the common issue of a low on/off current ratio in bis(1,2,5-thiadiazolo)-p-quinobis(1,3-dithiole) (BTQBT) based organic thin-film transistors (OTFTs).

Frequently Asked Questions (FAQs)

Q1: What is the on/off ratio in a transistor and why is it important?

A1: The on/off ratio is a critical performance metric for a transistor, representing the ratio of the drain current when the transistor is in the "on" state (Ion) to the drain current when it is in the "off" state (Ioff). A high on/off ratio is essential for digital logic applications to distinguish between the '1' and '0' states, ensuring low static power consumption and reliable switching behavior. In sensing applications, a high on/off ratio can contribute to a higher signal-to-noise ratio.

Q2: What is a typical on/off ratio for a high-performance BTQBT transistor?

A2: High-performance BTQBT-based vertical organic transistors have demonstrated on/off ratios exceeding 106.[1] However, achieving such high ratios depends on meticulous control over fabrication processes and materials.

Q3: What are the primary factors that can lead to a low on/off ratio in our BTQBT transistors?

A3: A low on/off ratio in BTQBT transistors can stem from several factors, broadly categorized as:

-

High Off-State Current (Ioff): This is the most common culprit and can be caused by gate leakage current, impurities in the semiconductor, or charge traps at the semiconductor/dielectric interface.

-

Low On-State Current (Ion): While less common as the primary cause for a low ratio, poor charge carrier mobility due to suboptimal morphology of the BTQBT film or high contact resistance can limit the maximum achievable current.

Troubleshooting Guides

This section provides a systematic approach to identifying and resolving the root causes of a low on/off ratio in your BTQBT transistors.

Issue 1: High Off-State Current (Ioff) Observed in Transfer Characteristics

A high off-current is a direct contributor to a reduced on/off ratio. The following steps will help you diagnose and address the potential causes.

Step 1: Investigate Gate Leakage Current (Ig)

A significant gate leakage current can be mistaken for a high channel off-current, artificially lowering the measured on/off ratio.[2][3]

-

Verification: Measure the gate current (Ig) simultaneously with the drain current (Id) during the transfer characteristic measurement. If Ig is comparable in magnitude to Ioff, then gate leakage is a significant contributor.

-

Troubleshooting Workflow:

Troubleshooting high gate leakage current. -

Solutions:

-

Improve Dielectric Integrity: Defects and pinholes in the gate dielectric layer can create leakage pathways.[4] Optimize the deposition parameters of your dielectric material. Consider using alternative high-quality dielectric materials.

-

Measurement Technique: A specialized measurement technique involving a simultaneous sweep of both gate and drain voltages can help to accurately estimate the true channel on/off ratio in the presence of significant gate leakage.[2][3]

-

Step 2: Assess the Semiconductor/Dielectric Interface

The interface between the BTQBT semiconductor and the gate dielectric is crucial for device performance.[5][6] Trapped charges and poor molecular ordering at this interface can increase the off-state current.[7]

-

Verification:

-

Hysteresis Analysis: A large hysteresis in the transfer characteristics can indicate the presence of charge traps at the interface.

-

Surface Characterization: Atomic Force Microscopy (AFM) can be used to assess the roughness of the dielectric surface. A smoother surface generally leads to better semiconductor film growth and a lower trap density.[7]

-

-

Troubleshooting Workflow:

Addressing semiconductor/dielectric interface issues. -

Solutions:

-

Surface Modification: The use of self-assembled monolayers (SAMs) on the dielectric surface can reduce trap states and promote better ordering of the BTQBT molecules.[7]

-

Optimize Deposition: The deposition conditions for the BTQBT layer, such as substrate temperature and deposition rate, should be optimized to achieve a highly crystalline and well-ordered film.

-

Step 3: Evaluate the Purity of the BTQBT Material

Chemical impurities in the organic semiconductor can act as dopants, leading to a higher intrinsic conductivity of the film and consequently a larger off-current.[8]

-

Verification: Material purity can be assessed using techniques like High-Performance Liquid Chromatography (HPLC) or Mass Spectrometry.

-

Solution:

-

Purification: If impurities are detected, purify the BTQBT material using appropriate techniques such as sublimation or recrystallization.

-

Quantitative Data Summary

The following table summarizes key performance parameters from literature for organic thin-film transistors, providing a benchmark for your BTQBT device performance.

| Parameter | Pentacene/PMMA OTFT (with high leakage)[3] | Pentacene/PMMA OTFT (corrected for leakage)[3] | High-Performance Vertical BTQBT Transistor[1] |

| On/Off Ratio | ~102 | ~104 | >106 |

| Subthreshold Slope (V/decade) | 10 | 4.5 | Not Reported |

| Mobility (cm2V-1s-1) | Not Reported | Not Reported | 7.3 |

Key Experimental Protocols

Protocol 1: BTQBT Thin-Film Transistor Fabrication (Illustrative Example)

This protocol describes a general procedure for fabricating a bottom-gate, top-contact BTQBT transistor.

-

Substrate Cleaning:

-

Use heavily n-doped Si wafers with a thermally grown SiO2 layer (e.g., 300 nm) as the substrate, where the Si serves as the gate electrode and SiO2 as the gate dielectric.

-

Clean the substrates sequentially in an ultrasonic bath with acetone, and isopropanol for 15 minutes each.

-

Dry the substrates with a stream of nitrogen gas.

-

-

Dielectric Surface Treatment (Optional but Recommended):

-

Treat the SiO2 surface with a SAM, such as octadecyltrichlorosilane (OTS), to improve the interface properties. This can be done by immersing the substrates in a dilute solution of OTS in an anhydrous solvent like toluene.

-

-

BTQBT Deposition:

-

Deposit a thin film of BTQBT (e.g., 50 nm) onto the substrate via thermal evaporation in a high-vacuum chamber (pressure < 10-6 Torr).

-

Maintain the substrate at an elevated temperature during deposition (e.g., 80-120 °C) to promote crystalline growth. The deposition rate should be kept low and constant (e.g., 0.1-0.2 Å/s).

-

-

Source/Drain Electrode Deposition:

-

Define the source and drain electrodes using a shadow mask.

-

Deposit the source and drain contacts (e.g., 50 nm of Gold) by thermal evaporation. The channel length and width are defined by the shadow mask dimensions.

-

Protocol 2: Electrical Characterization

-

Instrumentation: Use a semiconductor parameter analyzer or a source-measure unit.

-

Environment: Perform all measurements in an inert atmosphere (e.g., a nitrogen-filled glovebox) or in a vacuum to minimize the effects of air and moisture.

-

Transfer Characteristics (Id-Vg):

-

Apply a constant drain-source voltage (Vds), typically in the saturation regime (e.g., -40 V for a p-type device).

-

Sweep the gate-source voltage (Vgs) from a positive value (e.g., +20 V) to a negative value (e.g., -60 V).

-

Simultaneously measure the drain current (Id) and the gate current (Ig).

-

The on/off ratio is calculated as the maximum Id divided by the minimum Id from this sweep.

-

-

Output Characteristics (Id-Vds):

-

Apply a constant Vgs.

-

Sweep Vds from 0 V to a negative value (e.g., -60 V).

-

Repeat for several Vgs values to generate a family of curves.

-

References

- 1. researchgate.net [researchgate.net]

- 2. pubs.aip.org [pubs.aip.org]

- 3. researchgate.net [researchgate.net]

- 4. researchgate.net [researchgate.net]

- 5. Engineering of the dielectric–semiconductor interface in organic field-effect transistors - Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- 6. Semiconductor/dielectric interface in organic field-effect transistors: charge transport, interfacial effects, and perspectives with 2D molecular crystals - ProQuest [proquest.com]

- 7. researchgate.net [researchgate.net]

- 8. d31kydh6n6r5j5.cloudfront.net [d31kydh6n6r5j5.cloudfront.net]

Technical Support Center: Degradation Studies of Heterocyclic Aromatic Compounds

This technical support center provides guidance for researchers, scientists, and drug development professionals investigating the degradation pathways of complex heterocyclic aromatic compounds, such as Btqbt (2,2'-bis(2-(thiophen-2-yl)-1,3-benzothiazole)), under ambient and stressed conditions. Due to the limited specific data on Btqbt, this guide leverages established principles from forced degradation studies of related structures, particularly benzothiazole, to provide a framework for experimental design and troubleshooting.

Frequently Asked Questions (FAQs)

Q1: What are the primary degradation pathways for heterocyclic aromatic compounds like Btqbt under ambient conditions?

A1: While specific pathways for Btqbt are not extensively documented, related benzothiazole compounds are known to degrade via several key mechanisms when exposed to ambient conditions over time. These include:

-

Photodegradation: Exposure to UV or visible light can induce photochemical reactions. For benzothiazole derivatives, this can involve oxidation and the formation of hydroxylated byproducts.[1][2][3] Light can also act as a catalyst for oxidation reactions.[4]

-

Oxidation: Many drug substances undergo autoxidation, which is oxidation under normal storage conditions involving ground-state elemental oxygen.[4] For benzothiazoles, oxidative degradation can be initiated by reactive oxygen species, leading to the formation of various oxidized derivatives.[5][6][7]

-

Hydrolysis: This involves the reaction of the compound with water. The rate of hydrolysis is often pH-dependent. For some benzothiazole derivatives, hydrolysis can occur, particularly at acidic or basic pH, leading to the cleavage of certain bonds.[8][9][10]

-

Thermal Degradation: Elevated temperatures can provide the energy needed to break chemical bonds. The thermal stability of benzothiazole derivatives varies, with decomposition occurring at elevated temperatures.[11]

Q2: Where should I start if there is no existing literature on the degradation of my compound?

A2: When investigating a novel compound like Btqbt, a systematic approach using forced degradation studies is recommended.[12][13] These studies intentionally stress the molecule under more severe conditions than it would typically encounter to rapidly identify potential degradation products and pathways.[12][13] The typical stress conditions to investigate are acid and base hydrolysis, oxidation, photolysis, and thermal stress.[14] These studies are crucial for developing and validating stability-indicating analytical methods.

Q3: What is a "stability-indicating method," and why is it important?

A3: A stability-indicating method is an analytical procedure that can accurately quantify the concentration of the active pharmaceutical ingredient (API) without interference from its degradation products, impurities, or excipients. This is critical for ensuring that the measurements of the API's purity and potency are accurate over time. Forced degradation studies are essential for developing and validating these methods by generating the potential degradation products to ensure they can be separated from the parent compound.

Q4: How much degradation should I aim for in a forced degradation study?

A4: A generally accepted range for degradation in forced degradation studies is 5-20%.[15] Degrading the compound too much can lead to the formation of secondary degradants that may not be relevant to the actual stability of the product under normal storage conditions. Conversely, insufficient degradation may not produce enough of the primary degradation products to be detected and characterized.[15]

Troubleshooting Guides

Issue 1: No degradation is observed under initial stress conditions.

| Possible Cause | Troubleshooting Step |

| Conditions are too mild. | Gradually increase the intensity of the stressor. For thermal studies, increase the temperature. For hydrolysis, increase the concentration of the acid or base and/or the temperature.[13][14] For photolysis, increase the exposure time or light intensity. |

| Compound is highly stable. | For highly stable molecules, more extreme conditions may be necessary. For example, with oxidative stress, if 3% H₂O₂ shows no effect, the concentration can be increased.[15] |

| Poor solubility of the compound in the stress medium. | For aqueous hydrolysis studies of poorly soluble compounds, consider using a co-solvent to increase solubility. Ensure the co-solvent is inert and does not interfere with the analysis.[13][16] |

Issue 2: The compound degrades too quickly or completely.

| Possible Cause | Troubleshooting Step |

| Stress conditions are too harsh. | Reduce the intensity of the stressor. Decrease the temperature, shorten the exposure time, or use a lower concentration of the stress agent (e.g., acid, base, or oxidant).[15] |

| High reactivity of the molecule. | For highly labile compounds, conduct studies at milder conditions, such as lower temperatures or for shorter durations. It may be necessary to analyze samples at multiple early time points.[15] |

Issue 3: Poor mass balance is observed in the analytical results.

| Possible Cause | Troubleshooting Step |

| Formation of non-chromophoric or volatile degradation products. | Use a universal detector like a mass spectrometer (MS) or a charged aerosol detector (CAD) in addition to a UV detector. For volatile products, consider using gas chromatography (GC) with an appropriate sample preparation method. |

| Degradation products are not eluting from the chromatography column. | Modify the chromatographic method. This could involve changing the mobile phase composition, gradient slope, or the type of stationary phase. |

| Inaccurate response factors of degradation products. | If possible, isolate and purify the major degradation products to determine their individual response factors for more accurate quantification. |

Quantitative Data Summary

The following tables present example data for the degradation of benzothiazole (BTH) under various conditions, which can serve as a reference for designing experiments for similar compounds.

Table 1: Thermal Degradation of Benzothiazole (BTH) with Persulfate Activation [7]

| Temperature (°C) | Observed Rate Constant (k_obs) (min⁻¹) |

| 15 | 8.66 x 10⁻⁶ |

| 30 | 0.0011 |

| 40 | 0.0063 |

| 50 | 0.0211 |

| 60 | 0.1020 |

| 70 | 0.1785 |

Table 2: Comparison of BTH Degradation in Different UV-Based Advanced Oxidation Processes [17]

| Process | Degradation Rate Constant (k_obs) (min⁻¹) | % Removal |

| UV only | 0.0044 | - |

| UV/H₂O₂ | 0.0918 | 85% |

| UV/K₂S₂O₈ | 0.1893 | 100% |

Experimental Protocols

Acid/Base Hydrolysis