Silicon carbide

Description

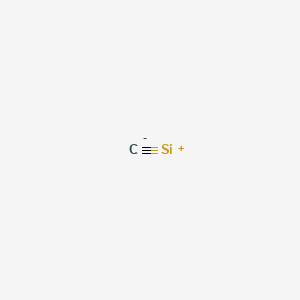

Structure

3D Structure

Properties

IUPAC Name |

methanidylidynesilanylium | |

|---|---|---|

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

InChI |

InChI=1S/CSi/c1-2 | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

InChI Key |

HBMJWWWQQXIZIP-UHFFFAOYSA-N | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Canonical SMILES |

[C-]#[Si+] | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Molecular Formula |

SiC, CSi | |

| Record name | SILICON CARBIDE | |

| Source | CAMEO Chemicals | |

| URL | https://cameochemicals.noaa.gov/chemical/25062 | |

| Description | CAMEO Chemicals is a chemical database designed for people who are involved in hazardous material incident response and planning. CAMEO Chemicals contains a library with thousands of datasheets containing response-related information and recommendations for hazardous materials that are commonly transported, used, or stored in the United States. CAMEO Chemicals was developed by the National Oceanic and Atmospheric Administration's Office of Response and Restoration in partnership with the Environmental Protection Agency's Office of Emergency Management. | |

| Explanation | CAMEO Chemicals and all other CAMEO products are available at no charge to those organizations and individuals (recipients) responsible for the safe handling of chemicals. However, some of the chemical data itself is subject to the copyright restrictions of the companies or organizations that provided the data. | |

| Record name | SILICON CARBIDE (non-fibrous) | |

| Source | ILO-WHO International Chemical Safety Cards (ICSCs) | |

| URL | https://www.ilo.org/dyn/icsc/showcard.display?p_version=2&p_card_id=1061 | |

| Description | The International Chemical Safety Cards (ICSCs) are data sheets intended to provide essential safety and health information on chemicals in a clear and concise way. The primary aim of the Cards is to promote the safe use of chemicals in the workplace. | |

| Explanation | Creative Commons CC BY 4.0 | |

| Record name | silicon carbide | |

| Source | Wikipedia | |

| URL | https://en.wikipedia.org/wiki/Silicon_carbide | |

| Description | Chemical information link to Wikipedia. | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

DSSTOX Substance ID |

DTXSID5052751 | |

| Record name | Silicon carbide | |

| Source | EPA DSSTox | |

| URL | https://comptox.epa.gov/dashboard/DTXSID5052751 | |

| Description | DSSTox provides a high quality public chemistry resource for supporting improved predictive toxicology. | |

Molecular Weight |

40.096 g/mol | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Physical Description |

Silicon carbide appears as yellow to green to bluish-black, iridescent crystals. Sublimes with decomposition at 2700 °C. Density 3.21 g cm-3. Insoluble in water. Soluble in molten alkalis (NaOH, KOH) and molten iron., Dry Powder; Dry Powder, Liquid; Dry Powder, Other Solid; Dry Powder, Pellets or Large Crystals; Other Solid, Yellow to green to bluish-black, iridescent crystals; [NIOSH], YELLOW-TO-GREEN-TO-BLUE-TO-BLACK CRYSTALS, DEPENDING ON PURITY., Yellow to green to bluish-black, iridescent crystals. | |

| Record name | SILICON CARBIDE | |

| Source | CAMEO Chemicals | |

| URL | https://cameochemicals.noaa.gov/chemical/25062 | |

| Description | CAMEO Chemicals is a chemical database designed for people who are involved in hazardous material incident response and planning. CAMEO Chemicals contains a library with thousands of datasheets containing response-related information and recommendations for hazardous materials that are commonly transported, used, or stored in the United States. CAMEO Chemicals was developed by the National Oceanic and Atmospheric Administration's Office of Response and Restoration in partnership with the Environmental Protection Agency's Office of Emergency Management. | |

| Explanation | CAMEO Chemicals and all other CAMEO products are available at no charge to those organizations and individuals (recipients) responsible for the safe handling of chemicals. However, some of the chemical data itself is subject to the copyright restrictions of the companies or organizations that provided the data. | |

| Record name | Silicon carbide (SiC) | |

| Source | EPA Chemicals under the TSCA | |

| URL | https://www.epa.gov/chemicals-under-tsca | |

| Description | EPA Chemicals under the Toxic Substances Control Act (TSCA) collection contains information on chemicals and their regulations under TSCA, including non-confidential content from the TSCA Chemical Substance Inventory and Chemical Data Reporting. | |

| Record name | Silicon carbide | |

| Source | Haz-Map, Information on Hazardous Chemicals and Occupational Diseases | |

| URL | https://haz-map.com/Agents/624 | |

| Description | Haz-Map® is an occupational health database designed for health and safety professionals and for consumers seeking information about the adverse effects of workplace exposures to chemical and biological agents. | |

| Explanation | Copyright (c) 2022 Haz-Map(R). All rights reserved. Unless otherwise indicated, all materials from Haz-Map are copyrighted by Haz-Map(R). No part of these materials, either text or image may be used for any purpose other than for personal use. Therefore, reproduction, modification, storage in a retrieval system or retransmission, in any form or by any means, electronic, mechanical or otherwise, for reasons other than personal use, is strictly prohibited without prior written permission. | |

| Record name | SILICON CARBIDE (non-fibrous) | |

| Source | ILO-WHO International Chemical Safety Cards (ICSCs) | |

| URL | https://www.ilo.org/dyn/icsc/showcard.display?p_version=2&p_card_id=1061 | |

| Description | The International Chemical Safety Cards (ICSCs) are data sheets intended to provide essential safety and health information on chemicals in a clear and concise way. The primary aim of the Cards is to promote the safe use of chemicals in the workplace. | |

| Explanation | Creative Commons CC BY 4.0 | |

| Record name | SILICON CARBIDE | |

| Source | Occupational Safety and Health Administration (OSHA) | |

| URL | https://www.osha.gov/chemicaldata/368 | |

| Description | The OSHA Occupational Chemical Database contains over 800 entries with information such as physical properties, exposure guidelines, etc. | |

| Explanation | Materials created by the federal government are generally part of the public domain and may be used, reproduced and distributed without permission. Therefore, content on this website which is in the public domain may be used without the prior permission of the U.S. Department of Labor (DOL). Warning: Some content - including both images and text - may be the copyrighted property of others and used by the DOL under a license. | |

| Record name | Silicon carbide | |

| Source | The National Institute for Occupational Safety and Health (NIOSH) | |

| URL | https://www.cdc.gov/niosh/npg/npgd0555.html | |

| Description | The NIOSH Pocket Guide to Chemical Hazards is intended as a source of general industrial hygiene information on several hundred chemicals/classes for workers, employers, and occupational health professionals. Read more: https://www.cdc.gov/niosh/npg/ | |

| Explanation | The information provided using CDC Web site is only intended to be general summary information to the public. It is not intended to take the place of either the written law or regulations. | |

Boiling Point |

Sublimes (NIOSH, 2023), sublimes, Sublimes | |

| Record name | SILICON CARBIDE | |

| Source | CAMEO Chemicals | |

| URL | https://cameochemicals.noaa.gov/chemical/25062 | |

| Description | CAMEO Chemicals is a chemical database designed for people who are involved in hazardous material incident response and planning. CAMEO Chemicals contains a library with thousands of datasheets containing response-related information and recommendations for hazardous materials that are commonly transported, used, or stored in the United States. CAMEO Chemicals was developed by the National Oceanic and Atmospheric Administration's Office of Response and Restoration in partnership with the Environmental Protection Agency's Office of Emergency Management. | |

| Explanation | CAMEO Chemicals and all other CAMEO products are available at no charge to those organizations and individuals (recipients) responsible for the safe handling of chemicals. However, some of the chemical data itself is subject to the copyright restrictions of the companies or organizations that provided the data. | |

| Record name | SILICON CARBIDE | |

| Source | Occupational Safety and Health Administration (OSHA) | |

| URL | https://www.osha.gov/chemicaldata/368 | |

| Description | The OSHA Occupational Chemical Database contains over 800 entries with information such as physical properties, exposure guidelines, etc. | |

| Explanation | Materials created by the federal government are generally part of the public domain and may be used, reproduced and distributed without permission. Therefore, content on this website which is in the public domain may be used without the prior permission of the U.S. Department of Labor (DOL). Warning: Some content - including both images and text - may be the copyrighted property of others and used by the DOL under a license. | |

| Record name | Silicon carbide | |

| Source | The National Institute for Occupational Safety and Health (NIOSH) | |

| URL | https://www.cdc.gov/niosh/npg/npgd0555.html | |

| Description | The NIOSH Pocket Guide to Chemical Hazards is intended as a source of general industrial hygiene information on several hundred chemicals/classes for workers, employers, and occupational health professionals. Read more: https://www.cdc.gov/niosh/npg/ | |

| Explanation | The information provided using CDC Web site is only intended to be general summary information to the public. It is not intended to take the place of either the written law or regulations. | |

Solubility |

Insoluble (NIOSH, 2023), INSOL IN COLD WATER, HOT WATER, & ACID; SOL IN FUSED POTASSIUM HYDROXIDE, INSOL IN ALCOHOL; SOL IN MOLTEN IRON, Solubility in water: none, Insoluble | |

| Record name | SILICON CARBIDE | |

| Source | CAMEO Chemicals | |

| URL | https://cameochemicals.noaa.gov/chemical/25062 | |

| Description | CAMEO Chemicals is a chemical database designed for people who are involved in hazardous material incident response and planning. CAMEO Chemicals contains a library with thousands of datasheets containing response-related information and recommendations for hazardous materials that are commonly transported, used, or stored in the United States. CAMEO Chemicals was developed by the National Oceanic and Atmospheric Administration's Office of Response and Restoration in partnership with the Environmental Protection Agency's Office of Emergency Management. | |

| Explanation | CAMEO Chemicals and all other CAMEO products are available at no charge to those organizations and individuals (recipients) responsible for the safe handling of chemicals. However, some of the chemical data itself is subject to the copyright restrictions of the companies or organizations that provided the data. | |

| Record name | SILICON CARBIDE | |

| Source | Hazardous Substances Data Bank (HSDB) | |

| URL | https://pubchem.ncbi.nlm.nih.gov/source/hsdb/681 | |

| Description | The Hazardous Substances Data Bank (HSDB) is a toxicology database that focuses on the toxicology of potentially hazardous chemicals. It provides information on human exposure, industrial hygiene, emergency handling procedures, environmental fate, regulatory requirements, nanomaterials, and related areas. The information in HSDB has been assessed by a Scientific Review Panel. | |

| Record name | SILICON CARBIDE (non-fibrous) | |

| Source | ILO-WHO International Chemical Safety Cards (ICSCs) | |

| URL | https://www.ilo.org/dyn/icsc/showcard.display?p_version=2&p_card_id=1061 | |

| Description | The International Chemical Safety Cards (ICSCs) are data sheets intended to provide essential safety and health information on chemicals in a clear and concise way. The primary aim of the Cards is to promote the safe use of chemicals in the workplace. | |

| Explanation | Creative Commons CC BY 4.0 | |

| Record name | Silicon carbide | |

| Source | The National Institute for Occupational Safety and Health (NIOSH) | |

| URL | https://www.cdc.gov/niosh/npg/npgd0555.html | |

| Description | The NIOSH Pocket Guide to Chemical Hazards is intended as a source of general industrial hygiene information on several hundred chemicals/classes for workers, employers, and occupational health professionals. Read more: https://www.cdc.gov/niosh/npg/ | |

| Explanation | The information provided using CDC Web site is only intended to be general summary information to the public. It is not intended to take the place of either the written law or regulations. | |

Density |

3.23 (NIOSH, 2023) - Denser than water; will sink, 3.23, 3.2 g/cm³ | |

| Record name | SILICON CARBIDE | |

| Source | CAMEO Chemicals | |

| URL | https://cameochemicals.noaa.gov/chemical/25062 | |

| Description | CAMEO Chemicals is a chemical database designed for people who are involved in hazardous material incident response and planning. CAMEO Chemicals contains a library with thousands of datasheets containing response-related information and recommendations for hazardous materials that are commonly transported, used, or stored in the United States. CAMEO Chemicals was developed by the National Oceanic and Atmospheric Administration's Office of Response and Restoration in partnership with the Environmental Protection Agency's Office of Emergency Management. | |

| Explanation | CAMEO Chemicals and all other CAMEO products are available at no charge to those organizations and individuals (recipients) responsible for the safe handling of chemicals. However, some of the chemical data itself is subject to the copyright restrictions of the companies or organizations that provided the data. | |

| Record name | SILICON CARBIDE | |

| Source | Hazardous Substances Data Bank (HSDB) | |

| URL | https://pubchem.ncbi.nlm.nih.gov/source/hsdb/681 | |

| Description | The Hazardous Substances Data Bank (HSDB) is a toxicology database that focuses on the toxicology of potentially hazardous chemicals. It provides information on human exposure, industrial hygiene, emergency handling procedures, environmental fate, regulatory requirements, nanomaterials, and related areas. The information in HSDB has been assessed by a Scientific Review Panel. | |

| Record name | SILICON CARBIDE (non-fibrous) | |

| Source | ILO-WHO International Chemical Safety Cards (ICSCs) | |

| URL | https://www.ilo.org/dyn/icsc/showcard.display?p_version=2&p_card_id=1061 | |

| Description | The International Chemical Safety Cards (ICSCs) are data sheets intended to provide essential safety and health information on chemicals in a clear and concise way. The primary aim of the Cards is to promote the safe use of chemicals in the workplace. | |

| Explanation | Creative Commons CC BY 4.0 | |

| Record name | SILICON CARBIDE | |

| Source | Occupational Safety and Health Administration (OSHA) | |

| URL | https://www.osha.gov/chemicaldata/368 | |

| Description | The OSHA Occupational Chemical Database contains over 800 entries with information such as physical properties, exposure guidelines, etc. | |

| Explanation | Materials created by the federal government are generally part of the public domain and may be used, reproduced and distributed without permission. Therefore, content on this website which is in the public domain may be used without the prior permission of the U.S. Department of Labor (DOL). Warning: Some content - including both images and text - may be the copyrighted property of others and used by the DOL under a license. | |

| Record name | Silicon carbide | |

| Source | The National Institute for Occupational Safety and Health (NIOSH) | |

| URL | https://www.cdc.gov/niosh/npg/npgd0555.html | |

| Description | The NIOSH Pocket Guide to Chemical Hazards is intended as a source of general industrial hygiene information on several hundred chemicals/classes for workers, employers, and occupational health professionals. Read more: https://www.cdc.gov/niosh/npg/ | |

| Explanation | The information provided using CDC Web site is only intended to be general summary information to the public. It is not intended to take the place of either the written law or regulations. | |

Vapor Pressure |

0 mmHg (approx) (NIOSH, 2023), 0 mmHg (approx) | |

| Record name | SILICON CARBIDE | |

| Source | CAMEO Chemicals | |

| URL | https://cameochemicals.noaa.gov/chemical/25062 | |

| Description | CAMEO Chemicals is a chemical database designed for people who are involved in hazardous material incident response and planning. CAMEO Chemicals contains a library with thousands of datasheets containing response-related information and recommendations for hazardous materials that are commonly transported, used, or stored in the United States. CAMEO Chemicals was developed by the National Oceanic and Atmospheric Administration's Office of Response and Restoration in partnership with the Environmental Protection Agency's Office of Emergency Management. | |

| Explanation | CAMEO Chemicals and all other CAMEO products are available at no charge to those organizations and individuals (recipients) responsible for the safe handling of chemicals. However, some of the chemical data itself is subject to the copyright restrictions of the companies or organizations that provided the data. | |

| Record name | SILICON CARBIDE | |

| Source | Occupational Safety and Health Administration (OSHA) | |

| URL | https://www.osha.gov/chemicaldata/368 | |

| Description | The OSHA Occupational Chemical Database contains over 800 entries with information such as physical properties, exposure guidelines, etc. | |

| Explanation | Materials created by the federal government are generally part of the public domain and may be used, reproduced and distributed without permission. Therefore, content on this website which is in the public domain may be used without the prior permission of the U.S. Department of Labor (DOL). Warning: Some content - including both images and text - may be the copyrighted property of others and used by the DOL under a license. | |

| Record name | Silicon carbide | |

| Source | The National Institute for Occupational Safety and Health (NIOSH) | |

| URL | https://www.cdc.gov/niosh/npg/npgd0555.html | |

| Description | The NIOSH Pocket Guide to Chemical Hazards is intended as a source of general industrial hygiene information on several hundred chemicals/classes for workers, employers, and occupational health professionals. Read more: https://www.cdc.gov/niosh/npg/ | |

| Explanation | The information provided using CDC Web site is only intended to be general summary information to the public. It is not intended to take the place of either the written law or regulations. | |

Color/Form |

EXCEEDINGLY HARD, GREEN TO BLUISH-BLACK, IRIDESCENT, SHARP CRYSTALS, HEXAGONAL OR CUBIC, Yellow to green to bluish black, iridescent crystals. | |

CAS No. |

409-21-2 | |

| Record name | SILICON CARBIDE | |

| Source | CAMEO Chemicals | |

| URL | https://cameochemicals.noaa.gov/chemical/25062 | |

| Description | CAMEO Chemicals is a chemical database designed for people who are involved in hazardous material incident response and planning. CAMEO Chemicals contains a library with thousands of datasheets containing response-related information and recommendations for hazardous materials that are commonly transported, used, or stored in the United States. CAMEO Chemicals was developed by the National Oceanic and Atmospheric Administration's Office of Response and Restoration in partnership with the Environmental Protection Agency's Office of Emergency Management. | |

| Explanation | CAMEO Chemicals and all other CAMEO products are available at no charge to those organizations and individuals (recipients) responsible for the safe handling of chemicals. However, some of the chemical data itself is subject to the copyright restrictions of the companies or organizations that provided the data. | |

| Record name | Silicon carbide | |

| Source | ChemIDplus | |

| URL | https://pubchem.ncbi.nlm.nih.gov/substance/?source=chemidplus&sourceid=0000409212 | |

| Description | ChemIDplus is a free, web search system that provides access to the structure and nomenclature authority files used for the identification of chemical substances cited in National Library of Medicine (NLM) databases, including the TOXNET system. | |

| Record name | Silicon carbide (SiC) | |

| Source | EPA Chemicals under the TSCA | |

| URL | https://www.epa.gov/chemicals-under-tsca | |

| Description | EPA Chemicals under the Toxic Substances Control Act (TSCA) collection contains information on chemicals and their regulations under TSCA, including non-confidential content from the TSCA Chemical Substance Inventory and Chemical Data Reporting. | |

| Record name | Silicon carbide | |

| Source | EPA DSSTox | |

| URL | https://comptox.epa.gov/dashboard/DTXSID5052751 | |

| Description | DSSTox provides a high quality public chemistry resource for supporting improved predictive toxicology. | |

| Record name | Silicon carbide | |

| Source | European Chemicals Agency (ECHA) | |

| URL | https://echa.europa.eu/substance-information/-/substanceinfo/100.006.357 | |

| Description | The European Chemicals Agency (ECHA) is an agency of the European Union which is the driving force among regulatory authorities in implementing the EU's groundbreaking chemicals legislation for the benefit of human health and the environment as well as for innovation and competitiveness. | |

| Explanation | Use of the information, documents and data from the ECHA website is subject to the terms and conditions of this Legal Notice, and subject to other binding limitations provided for under applicable law, the information, documents and data made available on the ECHA website may be reproduced, distributed and/or used, totally or in part, for non-commercial purposes provided that ECHA is acknowledged as the source: "Source: European Chemicals Agency, http://echa.europa.eu/". Such acknowledgement must be included in each copy of the material. ECHA permits and encourages organisations and individuals to create links to the ECHA website under the following cumulative conditions: Links can only be made to webpages that provide a link to the Legal Notice page. | |

| Record name | SILICON CARBIDE | |

| Source | Hazardous Substances Data Bank (HSDB) | |

| URL | https://pubchem.ncbi.nlm.nih.gov/source/hsdb/681 | |

| Description | The Hazardous Substances Data Bank (HSDB) is a toxicology database that focuses on the toxicology of potentially hazardous chemicals. It provides information on human exposure, industrial hygiene, emergency handling procedures, environmental fate, regulatory requirements, nanomaterials, and related areas. The information in HSDB has been assessed by a Scientific Review Panel. | |

| Record name | SILICON CARBIDE (non-fibrous) | |

| Source | ILO-WHO International Chemical Safety Cards (ICSCs) | |

| URL | https://www.ilo.org/dyn/icsc/showcard.display?p_version=2&p_card_id=1061 | |

| Description | The International Chemical Safety Cards (ICSCs) are data sheets intended to provide essential safety and health information on chemicals in a clear and concise way. The primary aim of the Cards is to promote the safe use of chemicals in the workplace. | |

| Explanation | Creative Commons CC BY 4.0 | |

| Record name | SILICON CARBIDE | |

| Source | Occupational Safety and Health Administration (OSHA) | |

| URL | https://www.osha.gov/chemicaldata/368 | |

| Description | The OSHA Occupational Chemical Database contains over 800 entries with information such as physical properties, exposure guidelines, etc. | |

| Explanation | Materials created by the federal government are generally part of the public domain and may be used, reproduced and distributed without permission. Therefore, content on this website which is in the public domain may be used without the prior permission of the U.S. Department of Labor (DOL). Warning: Some content - including both images and text - may be the copyrighted property of others and used by the DOL under a license. | |

Melting Point |

4892 °F (Sublimes) (NIOSH, 2023), 2600 °C, 4892 °F (sublimes), 4892 °F (Sublimes) | |

| Record name | SILICON CARBIDE | |

| Source | CAMEO Chemicals | |

| URL | https://cameochemicals.noaa.gov/chemical/25062 | |

| Description | CAMEO Chemicals is a chemical database designed for people who are involved in hazardous material incident response and planning. CAMEO Chemicals contains a library with thousands of datasheets containing response-related information and recommendations for hazardous materials that are commonly transported, used, or stored in the United States. CAMEO Chemicals was developed by the National Oceanic and Atmospheric Administration's Office of Response and Restoration in partnership with the Environmental Protection Agency's Office of Emergency Management. | |

| Explanation | CAMEO Chemicals and all other CAMEO products are available at no charge to those organizations and individuals (recipients) responsible for the safe handling of chemicals. However, some of the chemical data itself is subject to the copyright restrictions of the companies or organizations that provided the data. | |

| Record name | SILICON CARBIDE | |

| Source | Hazardous Substances Data Bank (HSDB) | |

| URL | https://pubchem.ncbi.nlm.nih.gov/source/hsdb/681 | |

| Description | The Hazardous Substances Data Bank (HSDB) is a toxicology database that focuses on the toxicology of potentially hazardous chemicals. It provides information on human exposure, industrial hygiene, emergency handling procedures, environmental fate, regulatory requirements, nanomaterials, and related areas. The information in HSDB has been assessed by a Scientific Review Panel. | |

| Record name | SILICON CARBIDE | |

| Source | Occupational Safety and Health Administration (OSHA) | |

| URL | https://www.osha.gov/chemicaldata/368 | |

| Description | The OSHA Occupational Chemical Database contains over 800 entries with information such as physical properties, exposure guidelines, etc. | |

| Explanation | Materials created by the federal government are generally part of the public domain and may be used, reproduced and distributed without permission. Therefore, content on this website which is in the public domain may be used without the prior permission of the U.S. Department of Labor (DOL). Warning: Some content - including both images and text - may be the copyrighted property of others and used by the DOL under a license. | |

| Record name | Silicon carbide | |

| Source | The National Institute for Occupational Safety and Health (NIOSH) | |

| URL | https://www.cdc.gov/niosh/npg/npgd0555.html | |

| Description | The NIOSH Pocket Guide to Chemical Hazards is intended as a source of general industrial hygiene information on several hundred chemicals/classes for workers, employers, and occupational health professionals. Read more: https://www.cdc.gov/niosh/npg/ | |

| Explanation | The information provided using CDC Web site is only intended to be general summary information to the public. It is not intended to take the place of either the written law or regulations. | |

Foundational & Exploratory

A Technical Guide to the Crystal Structure Differences Between α-SiC and β-SiC

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides an in-depth exploration of the crystallographic distinctions between the two primary polymorphs of silicon carbide (SiC): alpha-silicon carbide (α-SiC) and beta-silicon carbide (β-SiC). Understanding these structural differences is paramount as they fundamentally influence the material's physical, electronic, and thermal properties, thereby dictating its suitability for various advanced applications.

Introduction to this compound Polymorphism

This compound is a compound semiconductor material renowned for its exceptional properties, including high hardness, excellent thermal conductivity, and a wide bandgap.[1][2] It exhibits a phenomenon known as polytypism, where it can exist in more than 250 different crystalline forms, or polytypes, while maintaining the same chemical composition.[3] These polytypes are variations in the stacking sequence of Si-C bilayers along the c-axis.[3][4] Despite this diversity, SiC polytypes are broadly categorized into two main polymorphs: the cubic β-SiC and the hexagonal or rhombohedral α-SiC.[5]

-

β-Silicon Carbide (β-SiC): This is the cubic form of SiC, crystallizing in a zincblende structure similar to diamond.[6] It is considered the low-temperature polymorph, typically formed at temperatures below 1700°C.[7] The most common and only cubic polytype is designated as 3C-SiC.[3]

-

α-Silicon Carbide (α-SiC): This polymorph encompasses all non-cubic, hexagonal, and rhombohedral polytypes.[8] α-SiC is the high-temperature polymorph, forming at temperatures exceeding 1700-2000°C.[7][9] Common α-SiC polytypes include 4H-SiC and 6H-SiC, where 'H' denotes hexagonal symmetry and the numeral indicates the number of Si-C bilayers in the unit cell.[10]

Core Crystallographic Differences

The fundamental distinction between α-SiC and β-SiC lies in the stacking sequence of the silicon-carbon bilayers. These layers can be arranged in three possible positions, denoted as A, B, and C.[3]

-

β-SiC (3C-SiC): Possesses a simple and consistent ABCABC... stacking sequence. This results in a cubic crystal structure with a three-bilayer periodicity.[3][10]

-

α-SiC: Exhibits more complex stacking sequences. For instance:

This variation in stacking leads to different crystal symmetries, unit cell dimensions, and space groups, as detailed in the table below.

Comparative Data of α-SiC and β-SiC

The structural differences between α-SiC and β-SiC give rise to distinct physical and electronic properties. The following tables summarize key quantitative data for the most common polytypes.

| Property | β-SiC (3C-SiC) | α-SiC (4H-SiC) | α-SiC (6H-SiC) |

| Crystal System | Cubic[5] | Hexagonal[7] | Hexagonal[7] |

| Space Group | F-43m (No. 216)[12] | P63mc (No. 186)[10] | P63mc (No. 186)[10] |

| Stacking Sequence | ABC...[3] | ABCB...[3] | ABCACB...[3] |

| Lattice Parameters (Å) | a = 4.35[12] | a = 3.073, c = 10.053 | a = 3.081, c = 15.117 |

| Property | β-SiC (3C-SiC) | α-SiC (4H-SiC) | α-SiC (6H-SiC) |

| Bandgap (eV) at 300K | ~2.3-2.4[3][13] | ~3.2[1] | ~3.0[1] |

| Electron Mobility (cm²/Vs) | High | High | Lower than 4H |

| Hardness (Mohs) | 9.25 - 9.6[14] | ~9 | ~9 |

| Thermal Conductivity (W/mK) at RT | High (~500)[15][16] | ~350-390[16][17] | ~320[16] |

Experimental Protocols for Differentiation

Several analytical techniques can be employed to distinguish between α-SiC and β-SiC. The primary methods include X-ray Diffraction (XRD), Transmission Electron Microscopy (TEM), and Raman Spectroscopy.

X-ray Diffraction (XRD)

XRD is a powerful non-destructive technique for identifying crystal structures. The different stacking sequences of α-SiC and β-SiC result in unique diffraction patterns.

Methodology:

-

Sample Preparation: The SiC sample, either in powder or bulk form, is prepared. For bulk samples, a flat, polished surface is required. Powder samples are typically mounted on a low-background sample holder.

-

Instrumentation: A powder X-ray diffractometer equipped with a Cu Kα radiation source (λ = 1.5406 Å) is commonly used.

-

Data Acquisition: A θ-2θ scan is performed over a range that includes the characteristic peaks of SiC polytypes (e.g., 20° to 80°).

-

Data Analysis: The resulting diffractogram is analyzed by comparing the peak positions (2θ values) and relative intensities with standard diffraction patterns from the Powder Diffraction File (PDF) database.

-

β-SiC (3C-SiC): Exhibits characteristic peaks corresponding to the (111), (200), (220), and (311) crystallographic planes.[3]

-

α-SiC (e.g., 6H-SiC): Shows additional diffraction peaks due to its larger unit cell and lower symmetry. For instance, the (100), (006), and (101) reflections are unique to hexagonal polytypes and absent in the 3C pattern.[3] The presence of peaks at 2θ values such as 34.2°, 38.2°, and 65.8° can indicate the 6H polytype.[3]

-

Transmission Electron Microscopy (TEM)

TEM provides direct visualization of the crystal lattice and can unambiguously determine the stacking sequence.

Methodology:

-

Sample Preparation: This is a critical and destructive step. A thin, electron-transparent sample (typically <100 nm thick) is prepared from the bulk material. This can be achieved through mechanical polishing followed by ion milling or by using a Focused Ion Beam (FIB) instrument to lift out a specific region of interest.[1][7][11]

-

Instrumentation: A High-Resolution Transmission Electron Microscope (HRTEM) is required.

-

Imaging and Diffraction:

-

Selected Area Electron Diffraction (SAED): By inserting a selected area aperture, a diffraction pattern can be obtained from a localized area of the sample.[18][19] The symmetry and spacing of the diffraction spots in the SAED pattern are characteristic of the specific polytype. A single crystal will produce a regular pattern of bright spots.[18]

-

High-Resolution TEM (HRTEM) Imaging: In this mode, the electron beam is used to form a phase-contrast image of the atomic columns.[20] By orienting the crystal along a specific zone axis (e.g., [11-20]), the stacking sequence of the Si-C bilayers can be directly imaged, allowing for the definitive identification of the polytype (e.g., ABC... for 3C, ABCB... for 4H).[6][21]

-

Raman Spectroscopy

Raman spectroscopy is a non-destructive optical technique that probes the vibrational modes of a crystal lattice. Different SiC polytypes have distinct phonon dispersion curves, leading to unique Raman spectra.

Methodology:

-

Sample Preparation: Typically requires minimal preparation. The sample is placed on the microscope stage.

-

Instrumentation: A Raman microscope with a laser excitation source (e.g., 532 nm or 633 nm) is used.

-

Data Acquisition: The laser is focused on the sample, and the scattered light is collected and analyzed by a spectrometer.

-

Data Analysis: The Raman spectrum of SiC exhibits several characteristic peaks. The positions of the folded transverse optical (FTO) and folded longitudinal optical (FLO) modes are particularly sensitive to the polytype.

By comparing the measured Raman shifts to known values for different polytypes, the specific crystal structure can be identified.[8][13]

Visualizing Structural Differences

The following diagrams, generated using the DOT language, illustrate the fundamental structural differences and an experimental workflow for their characterization.

Caption: Stacking sequences of Si-C bilayers for β-SiC (3C) and common α-SiC polytypes (4H and 6H).

References

- 1. pubs.acs.org [pubs.acs.org]

- 2. pubs.aip.org [pubs.aip.org]

- 3. physics.mff.cuni.cz [physics.mff.cuni.cz]

- 4. pubs.aip.org [pubs.aip.org]

- 5. ntrs.nasa.gov [ntrs.nasa.gov]

- 6. researchgate.net [researchgate.net]

- 7. ntrs.nasa.gov [ntrs.nasa.gov]

- 8. spectroscopyonline.com [spectroscopyonline.com]

- 9. Structural and Optical Properties of this compound Powders Synthesized from Organosilane Using High-Temperature High-Pressure Method - PMC [pmc.ncbi.nlm.nih.gov]

- 10. researchgate.net [researchgate.net]

- 11. apps.dtic.mil [apps.dtic.mil]

- 12. tp.physique.usherbrooke.ca [tp.physique.usherbrooke.ca]

- 13. SiC raman spectrum | Raman for life [ramanlife.com]

- 14. researchgate.net [researchgate.net]

- 15. pubs.aip.org [pubs.aip.org]

- 16. ctcms.nist.gov [ctcms.nist.gov]

- 17. researchgate.net [researchgate.net]

- 18. Selected area diffraction - Wikipedia [en.wikipedia.org]

- 19. MyScope [myscope.training]

- 20. High-resolution transmission electron microscopy - Wikipedia [en.wikipedia.org]

- 21. researchgate.net [researchgate.net]

- 22. researchgate.net [researchgate.net]

- 23. researchgate.net [researchgate.net]

Bandgap energy of different silicon carbide polytypes

An In-depth Technical Guide to the Bandgap Energy of Silicon Carbide Polytypes

Introduction to this compound and its Polytypes

This compound (SiC) is a wide-bandgap semiconductor material that has garnered significant attention for its applications in high-power, high-frequency, and high-temperature electronic devices.[1][2][3] Its exceptional physical and electronic properties, such as a high critical breakdown field, high thermal conductivity, and excellent chemical and mechanical stability, make it a superior alternative to conventional semiconductors like silicon in demanding environments.[1][2]

A unique characteristic of this compound is its ability to exist in many different crystal structures, a phenomenon known as polymorphism.[4] SiC exhibits a specific form of polymorphism called polytypism, where different crystal structures, or polytypes, are formed by variations in the stacking sequence of identical Si-C bilayers along a specific crystal axis.[4] While identical in two dimensions, these polytypes differ in the third dimension, leading to a wide range of electronic properties.[4] Over 250 SiC polytypes have been identified, though the most technologically significant and well-studied are 3C-SiC (cubic), 4H-SiC (hexagonal), 6H-SiC (hexagonal), and 15R-SiC (rhombohedral).[2][4][5] The variation in stacking sequence directly influences the material's bandgap energy, a critical parameter for any semiconductor application.[4]

Data Presentation: Bandgap Energies of Common SiC Polytypes

The bandgap energy (Eg) of SiC varies significantly among its different polytypes.[4][6] Generally, the bandgap increases with the degree of hexagonality in the crystal structure.[7] The table below summarizes the experimentally determined and theoretically calculated bandgap energies for several key SiC polytypes at room temperature (unless otherwise specified).

| Polytype | Crystal Structure | Bandgap Energy (Eg) [eV] | Measurement Temperature | Reference |

| 3C-SiC | Cubic (Zincblende) | ~2.3 - 2.4 | Room Temperature | [4][6] |

| 2.36 | 300 K | [8] | ||

| 2.416 | 2 K | [8] | ||

| 6H-SiC | Hexagonal | ~3.0 | Room Temperature | [4][6] |

| 3.02 | Room Temperature | [9] | ||

| 15R-SiC | Rhombohedral | 2.98 | Not Specified | [10] |

| 4H-SiC | Hexagonal | ~3.2 | Room Temperature | [6][11] |

| 3.23 | 300 K | [8] | ||

| 3.26 | Room Temperature | [9] | ||

| 2H-SiC | Hexagonal (Wurtzite) | ~3.3 | Room Temperature | [4] |

| 3.33 | Not Specified | [8] |

Experimental and Theoretical Protocols for Bandgap Determination

Accurate determination of a material's bandgap is crucial for device design and fabrication.[12] A variety of experimental and theoretical methods are employed to measure and calculate the bandgap of SiC polytypes.

Experimental Protocols

1. Optical Absorption Spectroscopy (Tauc Method)

Optical absorption is one of the most common techniques for determining the bandgap of semiconductor materials.[12] The method relies on the principle that a semiconductor will absorb photons with energy greater than or equal to its bandgap energy, causing electrons to be excited from the valence band to the conduction band.

-

Methodology:

-

Sample Preparation: A thin, optically polished sample of the SiC polytype is prepared to allow for the transmission of light. For bulk or powdered samples, diffuse reflectance measurements can be performed and the data can be converted into a pseudo-absorption spectrum.[12]

-

Measurement: The sample is placed in a UV-Visible (UV-Vis) spectrophotometer. The absorbance (or transmittance) of the material is measured over a range of photon wavelengths.

-

Data Analysis (Tauc Plot): The relationship between the absorption coefficient (α), the photon energy (hν), and the optical bandgap (Eg) is given by the Tauc equation: (αhν)1/n = A(hν - Eg) where 'A' is a constant and the exponent 'n' depends on the nature of the electronic transition. For a direct bandgap semiconductor, n = 1/2; for an indirect bandgap semiconductor like SiC, n = 2.

-

Extrapolation: A Tauc plot is generated by plotting (αhν)1/2 versus photon energy (hν). The linear portion of this plot is extrapolated to the energy axis (where (αhν)1/2 = 0). The intercept on the energy axis provides the value of the indirect bandgap, Eg.[12]

-

2. Photoluminescence (PL) Spectroscopy

Photoluminescence is a non-destructive spectroscopic technique that involves measuring the light emitted from a material after it has absorbed photons.

-

Methodology:

-

Excitation: The SiC sample is illuminated with a light source (typically a laser) with a photon energy greater than its bandgap energy. This excites electrons from the valence band to the conduction band, creating electron-hole pairs.

-

Recombination and Emission: These excited electrons and holes will eventually recombine. This recombination can be radiative, resulting in the emission of a photon.

-

Detection: The emitted light is collected and analyzed by a spectrometer. The spectrum of the emitted light reveals a peak corresponding to the energy of the photons emitted during the band-edge recombination.

-

Bandgap Determination: The energy of the emitted photons is approximately equal to the bandgap energy of the semiconductor. The peak energy in the PL spectrum provides a direct measurement of the bandgap. This technique is particularly useful for measuring the excitonic energy gap at low temperatures.[8]

-

Theoretical Protocols

1. Density Functional Theory (DFT) with GW Approximation

First-principles calculations based on Density Functional Theory (DFT) are powerful tools for investigating the electronic band structure of materials.[1][2]

-

Methodology:

-

Structure Definition: The calculation begins with the known crystal structure of the SiC polytype (e.g., 4H-SiC or 2H-SiC), including lattice parameters and atomic positions.

-

DFT Calculation: The electronic ground state of the crystal is calculated using DFT, often within approximations like the Local Density Approximation (LDA) or Generalized Gradient Approximation (GGA). These initial calculations provide a basic band structure but are known to underestimate the bandgap value.[1]

-

Quasiparticle Correction (GW Approximation): To obtain more accurate bandgap values, corrections are applied to the DFT results. The GW approximation (where G stands for the Green's function and W for the screened Coulomb interaction) is a state-of-the-art method for calculating quasiparticle energies.[1][2] This "single-shot" GW (G0W0) calculation, performed on top of the initial DFT result, corrects for the self-energy of the electrons and yields bandgap values that are in excellent agreement with experimental data.[1][2][5]

-

Analysis: The final output provides a detailed electronic band structure, from which the bandgap (the energy difference between the valence band maximum and the conduction band minimum) can be precisely determined.

-

Mandatory Visualizations

Caption: Logical relationship between SiC polytype, hexagonality, and bandgap energy.

Caption: Experimental workflow for determining bandgap energy using UV-Vis spectroscopy.

References

- 1. arxiv.org [arxiv.org]

- 2. icmp.lviv.ua [icmp.lviv.ua]

- 3. en.wikipedia.org [en.wikipedia.org]

- 4. en.wikipedia.org [en.wikipedia.org]

- 5. researchgate.net [researchgate.net]

- 6. sanhuiabrasives.com [sanhuiabrasives.com]

- 7. researchgate.net [researchgate.net]

- 8. NSM Archive - this compound (SiC) - Band structure [ioffe.ru]

- 9. hxnewmaterial.com [hxnewmaterial.com]

- 10. researchgate.net [researchgate.net]

- 11. preciseceramic.com [preciseceramic.com]

- 12. chemgroups.northwestern.edu [chemgroups.northwestern.edu]

The Core Properties of 4H-SiC: A Technical Guide for Power Electronics Advancement

An In-depth Technical Guide for Researchers and Scientists in Materials Science and Semiconductor Device Development.

The emergence of 4H-silicon carbide (4H-SiC) as a premier wide-bandgap semiconductor has catalyzed a paradigm shift in power electronics. Its exceptional material properties enable the fabrication of power devices that are smaller, faster, more efficient, and more reliable than their silicon-based counterparts. This technical guide provides a comprehensive overview of the fundamental properties of 4H-SiC, detailing the quantitative data, experimental methodologies for their characterization, and the intricate relationships that govern its superior performance in high-power applications.

Fundamental Material Properties of 4H-SiC

The superior performance of 4H-SiC in power electronics stems from its unique combination of electronic, thermal, and physical properties. These intrinsic characteristics allow for operation at higher voltages, temperatures, and switching frequencies, pushing the boundaries of power conversion and management.

Electronic Properties

The electronic structure of 4H-SiC provides the foundation for its high-power and high-frequency capabilities. A wide bandgap, high critical electric field, and excellent carrier transport properties are the cornerstones of its advantage over conventional semiconductors.

| Property | Symbol | Value | Units |

| Bandgap Energy | Eg | 3.26[1] | eV |

| Critical Electric Field | Ec | ~2.2 - 3[1][2] | MV/cm |

| Electron Mobility | µn | ≤900[3] | cm²/Vs |

| Hole Mobility | µp | ≤120[3] | cm²/Vs |

| Saturated Electron Velocity | vsat | 2.0 x 107[4] | cm/s |

| Relative Dielectric Constant | εr | 9.7[5] | - |

Thermal Properties

The ability to efficiently dissipate heat is critical for the reliability and longevity of power electronic devices. 4H-SiC's high thermal conductivity allows for better thermal management, enabling higher power densities and operation in demanding thermal environments.

| Property | Symbol | Value | Units |

| Thermal Conductivity | k | ~3.7 - 4.9[1][2][6] | W/cm·K |

Figures of Merit for Power Devices

To quantify the potential performance of a semiconductor material in power device applications, several figures of merit (FOMs) have been established. These FOMs provide a means to compare different materials and guide the development of next-generation power electronics.

Baliga's Figure of Merit (BFOM)

Baliga's Figure of Merit is a key indicator of a material's suitability for low-frequency power switching applications, where conduction losses are dominant. It is defined as:

BFOM = εrμEc³

A higher BFOM indicates lower specific on-resistance for a given breakdown voltage, leading to reduced conduction losses.

Johnson's Figure of Merit (JFOM)

Johnson's Figure of Merit is used to assess a material's performance in high-frequency and high-power applications. It is defined as:

JFOM = (Ecvsat / 2π)²

A higher JFOM suggests that a material can simultaneously handle high voltages and operate at high frequencies.

| Figure of Merit | 4H-SiC (Normalized to Si) |

| Baliga's Figure of Merit (BFOM) | ~200 |

| Johnson's Figure of Merit (JFOM) | ~20 |

Experimental Protocols for Characterization

Accurate characterization of the fundamental properties of 4H-SiC is essential for material development, device design, and process control. The following sections detail the methodologies for key experiments.

Determination of Bandgap Energy (Eg)

Method: Optical Absorption Spectroscopy

-

Sample Preparation: A thin, polished 4H-SiC wafer with a known thickness is prepared. The surface should be clean and free of contaminants.

-

Measurement Setup: A spectrophotometer equipped with a light source (e.g., deuterium and tungsten-halogen lamps), a monochromator, and a detector is used. The sample is placed in the light path.

-

Procedure:

-

A baseline spectrum is recorded without the sample to account for the system's response.

-

The transmission spectrum of the 4H-SiC sample is measured over a range of wavelengths, typically from the ultraviolet to the near-infrared region.

-

The absorption coefficient (α) is calculated from the transmission data using the Beer-Lambert law, taking into account the sample thickness and reflection losses.

-

-

Data Analysis:

-

A Tauc plot is generated by plotting (αhν)n against the photon energy (hν), where 'h' is Planck's constant and 'ν' is the frequency. For an indirect bandgap semiconductor like 4H-SiC, n = 1/2.

-

The linear portion of the Tauc plot is extrapolated to the energy axis. The intercept on the energy axis corresponds to the bandgap energy (Eg).

-

Measurement of Critical Electric Field (Ec)

Method: Avalanche Breakdown in p+-n Junctions

-

Device Fabrication: A p+-n diode structure is fabricated on a 4H-SiC wafer. This involves creating a highly doped p-type region on a moderately doped n-type epitaxial layer. Ohmic contacts are formed on both the p+ and n-type regions.

-

Measurement Setup: A high-voltage power supply, a current-limiting resistor, and a precise voltage and current measurement system (e.g., a semiconductor parameter analyzer) are required. The measurement is typically performed on a probe station to ensure good electrical contact.

-

Procedure:

-

The diode is reverse-biased by applying a negative voltage to the p+ contact with respect to the n-type contact.

-

The reverse voltage is gradually increased while monitoring the reverse leakage current.

-

The breakdown voltage (Vbr) is defined as the voltage at which a sharp, irreversible increase in the reverse current occurs, indicating avalanche breakdown.

-

-

Data Analysis:

-

The critical electric field is determined from the breakdown voltage and the doping concentration of the n-type drift layer. For a one-sided abrupt junction, the maximum electric field at breakdown (Ec) can be calculated using the following equation: Ec = (2qNdVbr / εs)1/2 where 'q' is the elementary charge, 'Nd' is the donor doping concentration, and 'εs' is the permittivity of 4H-SiC.

-

Characterization of Carrier Mobility (µ) and Concentration (n, p)

Method: Hall Effect Measurement

-

Sample Preparation: A van der Pauw or Hall bar geometry is patterned on the 4H-SiC sample. Ohmic contacts are formed at the corners of the sample.

-

Measurement Setup: A constant current source, a high-impedance voltmeter, and a magnetic field source (electromagnet or permanent magnet) are used. The sample is mounted in a cryostat to allow for temperature-dependent measurements.

-

Procedure:

-

A constant current (I) is passed through two adjacent contacts, and the voltage (V) is measured across the other two contacts. This is repeated for different contact configurations to determine the sample resistivity.

-

A magnetic field (B) is applied perpendicular to the sample surface.

-

The Hall voltage (VH) is measured across the contacts perpendicular to the current flow. The measurement is repeated with the magnetic field direction reversed to eliminate thermoelectric effects.

-

-

Data Analysis:

-

The Hall coefficient (RH) is calculated as: RH = (VH · t) / (I · B) where 't' is the thickness of the conductive layer.

-

The carrier concentration (n or p) is determined from the Hall coefficient: n (or p) = 1 / (q · RH)

-

The Hall mobility (µH) is then calculated using the measured resistivity (ρ) and the Hall coefficient: µH = |RH| / ρ

-

Measurement of Thermal Conductivity (k)

Method: Laser Flash Analysis (LFA)

-

Sample Preparation: A small, flat, and opaque sample of 4H-SiC with a known thickness is prepared. The surfaces are often coated with a thin layer of graphite to enhance absorption of the laser pulse and emission of thermal radiation.

-

Measurement Setup: The LFA instrument consists of a high-intensity, short-duration laser pulse source, a sample holder within a furnace for temperature control, and an infrared (IR) detector.

-

Procedure:

-

The front surface of the sample is irradiated with a short laser pulse.

-

The IR detector monitors the temperature rise on the rear surface of the sample as a function of time.

-

-

Data Analysis:

-

The thermal diffusivity (α) is calculated from the time it takes for the rear surface temperature to reach half of its maximum rise (t1/2): α = 0.1388 · L² / t1/2 where 'L' is the sample thickness.

-

The thermal conductivity (k) is then determined using the measured thermal diffusivity, the specific heat capacity (Cp), and the density (ρ) of 4H-SiC: k = α · Cp · ρ The specific heat capacity and density may need to be measured separately or obtained from literature values for the corresponding temperature.

-

Visualizing the Core of 4H-SiC's Performance

The interplay between the fundamental properties of 4H-SiC dictates its performance in power electronic devices. The following diagrams illustrate these relationships and the workflow for material characterization.

Caption: Relationship between 4H-SiC properties and device performance.

Caption: General workflow for 4H-SiC material characterization.

References

An In-depth Technical Guide to Silicon Carbide (SiC)

Authored for Researchers, Scientists, and Drug Development Professionals

This guide provides a comprehensive overview of silicon carbide (SiC), a compound of silicon and carbon with the chemical formula SiC.[1][2][3][4] Also known as carborundum, it is a synthetically produced crystalline compound recognized for its exceptional hardness and thermal stability.[1][3]

Core Properties and Data

This compound is a covalent compound where silicon and carbon atoms are bonded in a 1:1 ratio, forming a tetrahedral crystal structure.[4][5] This strong covalent bonding is responsible for its remarkable hardness, which is comparable to that of a diamond.[5] It is highly inert chemically and begins to sublimate at approximately 2,700°C rather than melting.[1]

| Property | Value |

| Molecular Formula | SiC |

| Molar Mass | 40.10 g/mol |

| Density | 3.21 g/cm³ |

| Hardness (Mohs scale) | 9-9.5 |

| Sublimation Point | ~2700 °C |

| Crystal Structure | Hexagonal (α-SiC), Zinc Blende (β-SiC) |

Crystal Structure and Polytypes

This compound exists in various crystalline forms known as polytypes. The two primary polytypes are alpha-silicon carbide (α-SiC) and beta-silicon carbide (β-SiC).[1][5]

-

Alpha-Silicon Carbide (α-SiC): This is the most common polymorph and is formed at temperatures exceeding 1,700°C.[1] It possesses a hexagonal crystal structure.[1][5]

-

Beta-Silicon Carbide (β-SiC): Formed at temperatures below 1,700°C, this modification has a zinc blende crystal structure.[1][5]

The different stacking sequences of the two-dimensional layers of silicon and carbon atoms distinguish the various polytypes.

Experimental Protocols: Synthesis of this compound

1. Acheson Process: This is the traditional method for the industrial synthesis of SiC.

-

Methodology:

-

A mixture of high-purity silica sand (SiO₂) and finely ground petroleum coke (C) is prepared.

-

This mixture is built up around a carbon conductor within an electrical resistance furnace.

-

An electric current is passed through the conductor, raising the temperature to between 2,200°C and 2,700°C.

-

At these temperatures, the carbon reduces the silica to silicon, which then reacts with the excess carbon to form this compound. The overall chemical reaction is: SiO₂ + 3C → SiC + 2CO.

-

The process continues for several days, after which the furnace is cooled and the SiC crystals are harvested.

-

2. Chemical Vapor Deposition (CVD): This method is employed to produce high-purity, thin films of SiC.

-

Methodology:

-

A substrate is placed in a reaction chamber.

-

Volatile precursor gases containing silicon (e.g., silane, SiH₄) and carbon (e.g., propane, C₃H₈) are introduced into the chamber along with a carrier gas, typically hydrogen.

-

The chamber is heated to high temperatures (typically 1,500-2,000°C).

-

The precursor gases decompose and react on the heated substrate surface, resulting in the deposition of a thin film of SiC.

-

Logical Relationships and Workflows

The synthesis and application of this compound involve a series of logical steps and relationships, from precursor materials to the final product with specific properties.

The diagram above illustrates the two primary synthesis routes for this compound, leading to different forms of the material which, after characterization, are utilized in various high-performance applications.

References

- 1. This compound - Wikipedia [en.wikipedia.org]

- 2. This compound | SiC | CID 9863 - PubChem [pubchem.ncbi.nlm.nih.gov]

- 3. This compound | Discovery & Modern Uses | Britannica [britannica.com]

- 4. This compound | SiC Structure, Physical Appearance & Uses | Study.com [study.com]

- 5. m.youtube.com [m.youtube.com]

Unveiling the Atomic Architecture: A Technical Guide to Crystal Structure and Polytypism in SiC Wafers

For Researchers, Scientists, and Drug Development Professionals

Silicon Carbide (SiC) wafers are at the forefront of semiconductor technology, offering superior performance in high-power and high-frequency applications. A fundamental understanding of their crystalline structure and the phenomenon of polytypism is crucial for harnessing their full potential. This technical guide provides an in-depth exploration of the atomic arrangement within SiC, the origins and characteristics of its various polytypes, and the experimental methodologies used for their characterization.

The Fundamental Crystal Structure of this compound

This compound is a compound semiconductor composed of silicon (Si) and carbon (C) atoms in a 1:1 stoichiometric ratio. Each atom is tetrahedrally bonded to four atoms of the opposite kind, forming a stable and robust crystal lattice. The fundamental building block of the SiC crystal structure is a bilayer of Si and C atoms. The polymorphism in SiC, known as polytypism, arises from the different stacking sequences of these bilayers along the c-axis.

The two most basic stacking sequences give rise to the simplest SiC polytypes:

-

3C-SiC (β-SiC): This polytype has a zincblende crystal structure with a cubic symmetry. The stacking sequence is a continuous repetition of ABCABC... layers.

-

2H-SiC: This polytype possesses a wurtzite crystal structure with hexagonal symmetry and a stacking sequence of ABAB...

All other numerous SiC polytypes are combinations of these fundamental zincblende and wurtzite structures.

The Phenomenon of Polytypism in SiC

The ability of SiC to crystallize into numerous different structures with the same chemical composition is termed polytypism. Over 250 polytypes of SiC have been identified, though only a few are commercially significant. The notation for SiC polytypes consists of a number indicating the periodicity of the stacking sequence along the c-axis and a letter representing the crystal system (C for cubic, H for hexagonal, and R for rhombohedral).

The most common and technologically important SiC polytypes include:

-

3C-SiC: As the only cubic polytype, it exhibits the highest electron mobility among the common polytypes.

-

4H-SiC: A hexagonal polytype with a stacking sequence of ABCB. It is widely used in high-power electronics due to its wide bandgap and high critical electric field.

-

6H-SiC: Another hexagonal polytype with a more complex stacking sequence of ABCACB. It was one of the first commercially available SiC polytypes.

-

15R-SiC: A rhombohedral polytype with a 15-layer stacking sequence.

The choice of polytype significantly influences the electronic and physical properties of the SiC wafer, making polytype control a critical aspect of SiC manufacturing.

Comparative Properties of Common SiC Polytypes

The distinct stacking sequences of SiC polytypes lead to significant differences in their material properties. A summary of the key physical and electronic properties of the most common polytypes is presented in the table below for easy comparison.

| Property | 3C-SiC | 4H-SiC | 6H-SiC |

| Crystal System | Cubic | Hexagonal | Hexagonal |

| Stacking Sequence | ABC | ABCB | ABCACB |

| Bandgap (eV) at 300K | 2.36 | 3.26 | 3.02 |

| Electron Mobility (cm²/Vs) | ~900 | ~800-1000 | ~400-500 |

| Hole Mobility (cm²/Vs) | ~40 | ~115 | ~90 |

| Thermal Conductivity (W/cmK) | 3.6 - 4.9 | 3.6 - 4.9 | 3.6 - 4.9 |

| Breakdown Electric Field (MV/cm) | 1.5 | 3.0 - 4.0 | 2.5 - 3.0 |

| Hardness (Mohs) | 9-9.5 | 9-9.5 | 9-9.5 |

Experimental Protocols for Polytype Characterization

Accurate identification and characterization of SiC polytypes are essential for quality control and device fabrication. The two primary non-destructive techniques employed for this purpose are X-ray Diffraction (XRD) and Raman Spectroscopy.

X-ray Diffraction (XRD)

Principle: XRD is a powerful technique for determining the crystal structure of materials. When a monochromatic X-ray beam is incident on a crystalline sample, the X-rays are diffracted by the crystal planes. The angles and intensities of the diffracted beams are unique to the crystal structure, allowing for the identification of the polytype.

Methodology:

-

Sample Preparation: A SiC wafer is mounted on the goniometer of the diffractometer. Proper alignment of the wafer is crucial for obtaining accurate results.

-

Instrument Setup:

-

X-ray Source: A copper X-ray tube (Cu Kα radiation, λ = 1.5406 Å) is commonly used.

-

Diffractometer: A high-resolution X-ray diffractometer, such as a Bruker D8 Discover or a Panalytical X'Pert, is employed.

-

Scan Type: A θ-2θ scan is typically performed to probe the crystallographic planes parallel to the wafer surface.

-

Scan Parameters: The scan range, step size, and scan speed are optimized to resolve the diffraction peaks of interest. A typical scan might be from 20° to 80° in 2θ with a step size of 0.02°.

-

-

Data Acquisition: The diffractometer software records the intensity of the diffracted X-rays as a function of the 2θ angle.

-

Data Analysis:

-

The resulting diffraction pattern is a plot of intensity versus 2θ.

-

The positions (2θ values) of the diffraction peaks are used to calculate the interplanar spacing (d-spacing) using Bragg's Law (nλ = 2d sinθ).

-

The obtained d-spacings and relative intensities of the peaks are compared with standard diffraction patterns from the International Centre for Diffraction Data (ICDD) database to identify the SiC polytype. Each polytype has a unique set of diffraction peaks. For example, the (0004) reflection for 4H-SiC and the (0006) reflection for 6H-SiC are often used for identification.

-

Raman Spectroscopy

Principle: Raman spectroscopy is a vibrational spectroscopy technique that provides information about the chemical bonds and crystal structure of a material. When monochromatic light (from a laser) interacts with a sample, it can be scattered inelastically, resulting in a shift in the frequency of the scattered light. This frequency shift, known as the Raman shift, is characteristic of the vibrational modes of the material and is unique for each SiC polytype.

Methodology:

-

Sample Preparation: The SiC wafer is placed on the microscope stage of the Raman spectrometer. No special sample preparation is typically required.

-

Instrument Setup:

-

Laser Source: A visible laser, such as a 532 nm (green) or 633 nm (red) laser, is commonly used.

-

Spectrometer: A high-resolution Raman spectrometer equipped with a confocal microscope is used to focus the laser onto the sample and collect the scattered light. A 100x objective lens is often used for high spatial resolution.

-

Grating and Detector: A diffraction grating with a high groove density (e.g., 1800 gr/mm) and a sensitive detector (e.g., a cooled CCD) are used to disperse and detect the Raman scattered light.

-

-

Data Acquisition: The Raman spectrum is recorded as the intensity of the scattered light versus the Raman shift (in units of cm⁻¹).

-

Data Analysis:

-

The Raman spectrum of SiC exhibits several characteristic peaks corresponding to transverse optical (TO) and longitudinal optical (LO) phonon modes.

-

The positions and shapes of these Raman peaks are highly sensitive to the SiC polytype. For instance, the folded transverse optical (FTO) and folded longitudinal optical (FLO) modes have distinct Raman shifts for 3C, 4H, and 6H-SiC.

-

By comparing the measured Raman spectrum to reference spectra of known SiC polytypes, the polytype of the wafer can be unambiguously identified. Raman mapping can also be used to visualize the spatial distribution of different polytypes across the wafer.

-

Visualizing SiC Polytypism and Characterization Workflow

To better illustrate the concepts discussed, the following diagrams have been generated using the DOT language.

Caption: Stacking sequences of common SiC polytypes.

A Technical Guide to the Discovery and History of Silicon Carbide Synthesis

For Researchers, Scientists, and Drug Development Professionals

This in-depth technical guide explores the seminal discoveries and historical evolution of silicon carbide (SiC) synthesis. From its accidental discovery to the development of sophisticated crystal growth techniques for advanced semiconductor applications, this document provides a comprehensive overview of the core methodologies, experimental protocols, and quantitative parameters that have defined the field.

The Dawn of a New Material: The Acheson Process

The story of synthetic this compound begins in 1891 with the American inventor Edward Goodrich Acheson.[1] While attempting to create artificial diamonds by heating a mixture of clay and powdered coke in an iron bowl, he observed the formation of shiny, hexagonal crystals.[2] Mistakenly believing it to be a compound of carbon and corundum (alumina from the clay), he named it "Carborundum."[2] This material, later identified as this compound (SiC), was found to be exceedingly hard, second only to diamond at the time.[3]

The industrial-scale production of SiC was made possible by the development of the Acheson process , a method that, in its fundamental principles, is still in use today for producing metallurgical and abrasive-grade SiC.[4] The process is a carbothermal reduction of silica in a large electric resistance furnace.

Experimental Protocol: The Acheson Process

The Acheson process is a batch process characterized by its high energy consumption and relatively low yield of high-purity SiC.

1. Raw Materials:

-

Silicon Source: High-purity silica (SiO₂) in the form of quartz sand.

-

Carbon Source: Petroleum coke.

-

Additives (optional): Sawdust to increase the porosity of the charge and facilitate the escape of gaseous byproducts; salt to act as a flux.

2. Furnace Setup:

-

A large, open-top refractory-lined furnace is used.

-

A central core of graphite rods or granulated coke is positioned between two carbon electrodes.

-

The reaction mixture of silica and coke is packed around this graphite core.

3. Synthesis Procedure:

-

An electric current is passed through the graphite core, which acts as a resistive heating element.

-

The temperature of the core is raised to over 2500°C, initiating the carbothermal reduction of silica.[5]

-

The high temperature is maintained for an extended period, typically around 36-40 hours.

-

The overall chemical reaction is: SiO₂ + 3C → SiC + 2CO (gas)

-

A more detailed sequence of reactions occurring within the furnace includes:

-

C + SiO₂ → SiO + CO

-

SiO₂ + CO → SiO + CO₂

-

C + CO₂ → 2CO

-

SiO + 2C → SiC + CO[2]

-

-

After the reaction is complete, the furnace is allowed to cool, which can take several days.

4. Product Extraction and Processing:

-

The furnace is dismantled to reveal a cylindrical ingot of SiC.

-

The ingot has a layered structure, with the highest purity, crystalline α-SiC found closest to the graphite core. Outer layers consist of lower-grade SiC, unreacted materials, and graphite.

-

The SiC crude is then crushed, milled, and classified according to size and purity for various applications.

Quantitative Data: Acheson Process

| Parameter | Value |

| Reaction Temperature | 1700 - 2500°C |

| Typical Duration | ~40 hours for heating phase |

| Energy Consumption | 6 - 12 kWh/kg of SiC produced |

| Process Efficiency | 11 - 18% of the total charge is converted to SiC |

| Purity of SiC | Varies by layer; metallurgical grade is lower, while the α-SiC layer is of higher purity. |

The Quest for Purity and Single Crystals: The Lely and Modified Lely (PVT) Methods

For electronic applications, the polycrystalline and often impure SiC produced by the Acheson process was inadequate. The mid-20th century saw the development of methods aimed at producing high-purity, single-crystal SiC.

In 1955, Jan Anthony Lely of Philips Research Laboratories developed a sublimation technique for growing SiC single crystals.[1] The Lely method involves heating a charge of polycrystalline SiC in a sealed graphite crucible. The SiC sublimes and then recrystallizes on cooler parts of the crucible, forming small, high-purity single crystals.

While the Lely method produced high-quality crystals, the nucleation and growth were largely uncontrolled. This led to the development of the Modified Lely method , also known as Physical Vapor Transport (PVT), in the late 1970s. This method introduced a seed crystal into the process, allowing for the growth of large, single-crystal boules of SiC with controlled polytype and orientation.

Experimental Protocol: The Modified Lely (PVT) Method

The Modified Lely method is the dominant technique for the commercial production of SiC wafers for the semiconductor industry.

1. Raw Materials:

-

Source Material: High-purity polycrystalline SiC powder (often produced by an improved Acheson process or other chemical synthesis routes).

-

Seed Crystal: A high-quality single crystal of SiC with a specific polytype (e.g., 4H- or 6H-SiC) and orientation.

2. Furnace Setup:

-

A high-temperature furnace, typically with induction heating.

-

A sealed graphite crucible containing the SiC source powder at the bottom and the seed crystal mounted on the lid.

-

The system is filled with a high-purity inert gas, usually Argon, at a controlled pressure.

3. Synthesis Procedure:

-

The crucible is heated to a high temperature, typically in the range of 2100-2400°C.

-

A precise temperature gradient is established between the source powder (hotter) and the seed crystal (cooler).

-

The SiC source material sublimes into gaseous species (primarily Si, Si₂C, and SiC₂).

-

These gaseous species are transported through the inert gas atmosphere to the cooler seed crystal.

-

The species condense on the seed crystal, leading to the epitaxial growth of a large SiC single crystal (boule).

-

The growth process is carried out for an extended period, often several days, to produce a boule of the desired length.

4. Product Processing:

-

After cooling, the SiC boule is harvested from the crucible.

-

The boule is then sliced into wafers using diamond-wire saws, and the wafers are lapped and polished to a mirror finish.

Quantitative Data: Modified Lely (PVT) Method

| Parameter | Value |

| Source Temperature | 2100 - 2400°C |

| Seed Temperature | Slightly lower than the source temperature |

| Inert Gas Pressure | 1 - 100 Torr (Argon) |

| Typical Growth Rate | 0.5 - 1.5 mm/hour |

| Purity of SiC | Very high, suitable for semiconductor applications. |

Thin Films and Heterostructures: Chemical Vapor Deposition (CVD)

Chemical Vapor Deposition (CVD) is a versatile technique for depositing high-purity, thin films of SiC with excellent control over thickness, composition, and crystal structure. It is widely used to grow epitaxial layers of SiC on SiC substrates for device fabrication.

Experimental Protocol: Chemical Vapor Deposition (CVD) of SiC

1. Precursor Gases:

-

Silicon Source: Typically silane (SiH₄) or chlorosilanes such as dichlorosilane (SiH₂Cl₂) or silicon tetrachloride (SiCl₄).

-

Carbon Source: Typically a hydrocarbon such as propane (C₃H₈), ethylene (C₂H₄), or methane (CH₄).

-

Carrier Gas: High-purity hydrogen (H₂) or argon (Ar).

2. Reactor Setup:

-

A CVD reactor, which can be a hot-wall or cold-wall system.

-

A susceptor (often graphite coated with SiC) to hold the substrate wafers.

-

A heating system (e.g., induction or resistance heating) to heat the susceptor and substrates to the required deposition temperature.

-

A gas delivery system to precisely control the flow rates of the precursor and carrier gases.

-

A vacuum system to control the reactor pressure.

3. Deposition Procedure:

-

The SiC substrates are loaded into the reactor.

-

The reactor is purged with a carrier gas and heated to the deposition temperature, typically between 1400°C and 1800°C for epitaxial growth.

-

The precursor gases are introduced into the reactor at controlled flow rates.

-

The precursor gases decompose and react on the hot substrate surface, leading to the deposition of a SiC film.

-

The deposition is carried out for a specific time to achieve the desired film thickness.

-

After deposition, the precursor gas flow is stopped, and the reactor is cooled down under a flow of carrier gas.

Quantitative Data: Chemical Vapor Deposition (CVD) of SiC

| Parameter | Value |

| Deposition Temperature | 650 - 1800°C (varies with specific process and desired film properties) |

| Reactor Pressure | Can range from low vacuum to atmospheric pressure |

| Typical Growth Rate | 0.5 - 100 µm/hour (highly dependent on process parameters) |

| Purity of SiC | Very high, with excellent control over doping and stoichiometry |

Visualizing the Synthesis Pathways and Workflows

To better understand the relationships and processes involved in this compound synthesis, the following diagrams are provided.

References

Electrical conductivity of n-type vs p-type SiC

An In-depth Technical Guide to the Electrical Conductivity of N-Type vs. P-Type Silicon Carbide

Introduction to this compound and Doping

This compound (SiC) is a wide band-gap semiconductor material that is increasingly utilized in high-power, high-frequency, and high-temperature electronic devices.[1] Its robust crystal structure, high thermal conductivity, and high breakdown electric field make it superior to silicon in many applications.[2][3] Pure, or intrinsic, SiC has a very low intrinsic carrier concentration, making it a poor conductor of electricity.[2] To be useful in electronic devices, its electrical conductivity must be precisely controlled through a process called doping.

Doping is the intentional introduction of impurities into a semiconductor crystal to increase the number of free charge carriers.[1][4] Depending on the impurity used, the doped SiC can be classified as either n-type or p-type.

-