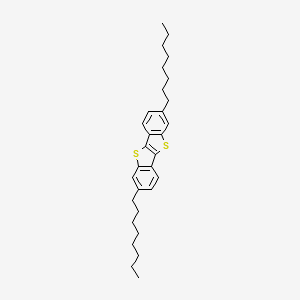

C8-Btbt

Description

Propriétés

IUPAC Name |

2,7-dioctyl-[1]benzothiolo[3,2-b][1]benzothiole | |

|---|---|---|

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

InChI |

InChI=1S/C30H40S2/c1-3-5-7-9-11-13-15-23-17-19-25-27(21-23)31-30-26-20-18-24(22-28(26)32-29(25)30)16-14-12-10-8-6-4-2/h17-22H,3-16H2,1-2H3 | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

InChI Key |

YWIGIVGUASXDPK-UHFFFAOYSA-N | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Canonical SMILES |

CCCCCCCCC1=CC2=C(C=C1)C3=C(S2)C4=C(S3)C=C(C=C4)CCCCCCCC | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Molecular Formula |

C30H40S2 | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

Molecular Weight |

464.8 g/mol | |

| Source | PubChem | |

| URL | https://pubchem.ncbi.nlm.nih.gov | |

| Description | Data deposited in or computed by PubChem | |

An In-depth Technical Guide to 2,7-dioctylbenzothieno[3,2-b]benzothiophene (C8-BTBT): Molecular Structure and Properties

An In-depth Technical Guide to 2,7-dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT): Molecular Structure and Properties

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides a comprehensive overview of the molecular structure and electronic properties of 2,7-dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT), a high-performance organic semiconductor. The information presented herein is intended to support research and development efforts in organic electronics and related fields.

Molecular Structure and Crystallography

C8-BTBT is a crystalline organic small molecule characterized by a planar benzothieno[3,2-b][1]benzothiophene (BTBT) core to which two octyl (C8) chains are attached at the 2 and 7 positions. This molecular design imparts a combination of excellent charge transport characteristics, solution processability, and good air stability.

The molecule adopts a monoclinic crystal structure, with the BTBT cores arranging in a herringbone packing motif.[2] This arrangement is crucial for its electronic properties, as it facilitates two-dimensional charge transport.[2] The octyl chains play a significant role in the molecular packing and solubility of the material.

Crystallographic Data

The crystallographic parameters for C8-BTBT have been determined by single-crystal X-ray diffraction (XRD).

| Parameter | Value |

| Crystal System | Monoclinic |

| Space Group | P2₁/c |

| a | 5.93 Å |

| b | 7.90 Å |

| c | 29.18 Å |

| β | 92.5° |

| Z | 2 |

Note: The specific bond lengths and angles within the C8-BTBT molecule can be found in the Crystallographic Information File (CIF) which is publicly available through crystallographic databases.

Electronic Properties

C8-BTBT is a p-type organic semiconductor, meaning that charge transport is dominated by the movement of holes. Its electronic properties are highly dependent on the molecular packing and orientation in the solid state.

| Property | Value | Measurement Conditions/Notes |

| Highest Occupied Molecular Orbital (HOMO) | -5.45 eV to -5.8 eV | Dependent on film thickness and molecular orientation on the substrate.[1] |

| Lowest Unoccupied Molecular Orbital (LUMO) | Approximately -1.6 eV | Estimated from HOMO level and optical bandgap. |

| Ionization Potential | 5.45 eV to 5.8 eV | Varies with molecular orientation, with lower values for standing-up configurations.[1] |

| Hole Mobility (µ) | Up to 43 cm²/Vs | Solution-processed thin-film transistors.[3] |

The ionization potential of C8-BTBT films shows a significant dependence on the molecular orientation relative to the substrate.[1] Films with molecules oriented perpendicular to the substrate (standing-up) exhibit a lower ionization potential compared to those with a parallel orientation (lying-down).[1]

Experimental Protocols

Synthesis of C8-BTBT

A common synthetic route to C8-BTBT involves a Wolff-Kishner reduction of a diketone precursor. The following is a representative protocol:

Step 1: Synthesis of 2,7-bis(octanoyl)[1]benzothieno[3,2-b][1]benzothiophene

-

This precursor is typically synthesized via a Friedel-Crafts acylation of the BTBT core.

Step 2: Wolff-Kishner Reduction

-

A mixture of 2,7-bis(octanoyl)[1]benzothieno[3,2-b][1]benzothiophene, hydrazine (B178648) hydrate, and potassium hydroxide (B78521) is dissolved in a high-boiling solvent such as diethylene glycol under an inert atmosphere (e.g., Nitrogen).

-

The reaction mixture is heated to approximately 110 °C for 1 hour.

-

The temperature is then raised to around 210 °C and maintained for several hours to drive the reaction to completion.

-

After cooling to room temperature, the reaction is quenched with water, leading to the precipitation of the crude product.

-

The precipitate is collected by vacuum filtration and washed with water and methanol.

-

The crude product is purified by column chromatography on silica (B1680970) gel using a non-polar eluent like hexane (B92381) to yield the final C8-BTBT product as a white solid.

Fabrication of a C8-BTBT-based Organic Field-Effect Transistor (OFET)

The following protocol describes the fabrication of a top-contact, bottom-gate OFET using solution-based methods:

Materials:

-

Heavily doped silicon wafer with a thermally grown silicon dioxide (SiO₂) layer (serves as the gate electrode and gate dielectric).

-

C8-BTBT solution in an organic solvent (e.g., toluene, chloroform).

-

Source and drain electrode material (e.g., gold).

Procedure:

-

Substrate Cleaning: The Si/SiO₂ substrate is thoroughly cleaned by ultrasonication in a series of solvents (e.g., acetone, isopropanol) and then dried. The surface can be further treated with an oxygen plasma or UV-ozone to improve the surface energy and promote uniform film formation.

-

Semiconductor Deposition: A solution of C8-BTBT is deposited onto the SiO₂ surface using a technique such as spin-coating. The spin speed and solution concentration are optimized to achieve the desired film thickness and morphology.

-

Annealing: The substrate with the C8-BTBT film is then annealed at a temperature above the boiling point of the solvent and below the melting point of C8-BTBT to remove residual solvent and improve the crystallinity of the film.

-

Electrode Deposition: Source and drain electrodes are deposited on top of the C8-BTBT film through a shadow mask using thermal evaporation. Gold is a commonly used electrode material due to its high work function and stability.

Visualizations

Molecular Structure of C8-BTBT

Caption: Simplified 2D representation of the C8-BTBT molecule.

Crystal Packing of C8-BTBT

Caption: Schematic of the herringbone packing of BTBT cores in the crystal.

Experimental Workflow for OFET Fabrication

An In-depth Technical Guide to the Charge Transport Mechanism in C8-BTBT Crystals

Prepared for: Researchers, Scientists, and Drug Development Professionals

Abstract

2,7-dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT) is a benchmark organic semiconductor renowned for its exceptional charge carrier mobility and environmental stability. These properties make it a leading candidate for next-generation flexible and low-cost electronics. Understanding the fundamental charge transport mechanism within its crystalline structure is paramount for optimizing device performance. This technical guide provides a comprehensive overview of the charge transport phenomena in C8-BTBT crystals. It delves into the dichotomy between band-like and hopping transport models, presents key quantitative performance data, details essential experimental protocols for crystal growth and device fabrication, and illustrates the critical factors that govern charge mobility.

Introduction

Organic field-effect transistors (OFETs) are foundational components for a host of emerging technologies, including flexible displays, wearable sensors, and radio-frequency identification (RFID) tags.[2] The performance of these devices is largely dictated by the intrinsic charge transport properties of the organic semiconductor used. C8-BTBT has attracted significant attention due to its remarkable hole mobility, which can exceed 40 cm² V⁻¹ s⁻¹ in solution-processed films.[2][3] This high performance is intrinsically linked to its ability to self-organize into highly ordered crystalline structures. The charge transport mechanism in these crystals is a complex interplay of molecular packing, temperature, and electronic coupling, exhibiting characteristics of both delocalized band-like transport and localized hopping transport. This guide aims to elucidate these mechanisms, providing researchers with the foundational knowledge required to harness the full potential of C8-BTBT.

Crystal Structure and Molecular Packing

The superior charge transport properties of C8-BTBT are a direct consequence of its specific solid-state arrangement. C8-BTBT crystallizes in a monoclinic structure, forming a lamella-like packing motif.[4] This structure is characterized by two key features:

-

Herringbone Packing: The rigid, planar benzothienobenzothiophene (BTBT) cores arrange themselves in a herringbone pattern. This configuration is highly favorable for two-dimensional charge transport, as it facilitates significant π-π orbital overlap between adjacent molecules.[4]

-

Lamellar Structure: The long octyl (C8) side chains extend outwards from the BTBT cores. These aliphatic chains direct the layered, or lamellar, stacking of the crystalline sheets and enhance the material's solubility for solution-based processing.[2][3]

This unique molecular assembly minimizes energetic disorder and creates efficient pathways for charge carriers (holes) to move across the crystal plane.

Core Charge Transport Mechanisms

The movement of charge carriers in organic semiconductors is typically described by two primary models: band-like transport and hopping transport. In C8-BTBT crystals, the dominant mechanism is highly dependent on the degree of crystalline order and the operating temperature.[5][6]

Band-like Transport

In highly crystalline, defect-free C8-BTBT, charge carriers can become delocalized over multiple molecules, forming electronic bands, similar to traditional inorganic semiconductors.[7] In this regime, charge transport is coherent, and mobility is limited by scattering with lattice vibrations (phonons).[6]

A key experimental signature of band-like transport is a negative temperature coefficient for mobility; that is, mobility increases as temperature decreases (μ ∝ T⁻ⁿ).[6] This behavior is clearly observed in high-quality monolayer C8-BTBT devices, particularly at temperatures below 150 K, confirming the presence of intrinsic band-like transport.[8][9][10]

Hopping Transport

In less ordered polycrystalline films or at higher temperatures, charge carriers are typically localized on individual molecules due to structural defects and thermal disorder.[6] Transport occurs through a series of discrete "hops" from one molecule to the next. This process is thermally activated, meaning carriers require energy to overcome the potential barrier between localized states.[11]

The signature of hopping transport is a positive temperature coefficient for mobility; mobility decreases as temperature decreases (μ ∝ exp(-Eₐ/kₒT)).[6] While high-quality C8-BTBT crystals are dominated by band-like characteristics, hopping may contribute to or dominate transport in solution-processed films with more grain boundaries and disorder.[5]

The prevailing view is that charge transport in C8-BTBT is a crossover phenomenon. At room temperature, it exists in a regime between pure band-like and pure hopping transport, where carriers are partially delocalized as polarons and their movement is influenced by dynamic molecular vibrations.[11][12]

Quantitative Charge Transport Parameters

The performance of C8-BTBT devices is highly dependent on the fabrication method, device architecture, and interface quality. The following table summarizes key quantitative data from various studies to provide a comparative overview.

| Preparation Method | Device Structure & Dielectric | Mobility (μ) [cm²/Vs] | On/Off Ratio | Contact Resistance (R_c) [Ω·cm] | Reference |

| Van der Waals Epitaxy | Monolayer on Boron Nitride | > 30 (intrinsic average: 24.5) | > 10⁸ | ~100 | [8][9][10] |

| Solution Shearing | Top-Contact / SiO₂ | up to 43 | > 10⁶ | Varies | [2][3] |

| Epitaxial Growth (SVA) | Top-Contact / iPP/SiO₂ | 2.5 (avg), 9.3 (max) | 10⁷ | Not specified | [13][14] |

| Spin-Coating + UV-Ozone | Top-Contact / SiO₂ | 6.50 | > 10⁶ | Not specified | [15][16] |

| Spin-Coating / Al₂O₃ | Top-Contact / PEDOT:PSS Electrodes | 0.6 ± 0.3 | ~3 x 10³ | Lower than Au | [2][3] |

| Iodine Doping | Top-Contact / SiO₂ | 1.4 -> 10.4 | > 10⁶ | Reduced by ~10² | [17][18] |

Key Experimental Protocols

Reproducible fabrication of high-performance C8-BTBT devices requires meticulous control over crystal growth and device assembly.

Thin Film & Crystal Growth Methods

-

Solution Shearing: A solution of C8-BTBT in a high-boiling-point solvent (e.g., chlorobenzene) is prepared. The solution is confined between a sharp blade and a heated substrate (e.g., Si/SiO₂). The blade is moved at a constant, slow speed (e.g., 10 mm/s), leaving behind a thin liquid film. The controlled solvent evaporation from this film promotes the growth of large, highly aligned crystalline domains.

-

Spin Coating: A solution of C8-BTBT (e.g., 10 mg/mL in toluene) is dispensed onto a substrate, which is then rotated at high speed (e.g., 1000-2500 rpm) for a set duration (e.g., 40-60 s).[2][19] This method produces uniform polycrystalline films. The quality of the film is often improved with a post-deposition thermal or solvent vapor annealing step.

-

Solvent Vapor Annealing (SVA): A pre-deposited C8-BTBT film (e.g., by spin-coating) is placed in a sealed chamber containing a reservoir of a solvent (e.g., toluene). The solvent vapor increases the molecular mobility within the film, allowing the molecules to reorganize into a more ordered, crystalline state with larger grain sizes.[20][21]

OFET Device Fabrication and Characterization

A common device architecture is the top-contact, bottom-gate OFET . The following protocol is a representative example.

-

Substrate Preparation: A heavily doped silicon wafer (acting as the gate electrode) with a thermally grown silicon dioxide (SiO₂) layer (acting as the gate dielectric) is used as the substrate. The substrate undergoes rigorous cleaning, typically involving sonication in a sequence of deionized water, acetone, and isopropanol.

-

Dielectric Surface Treatment: The SiO₂ surface is often treated to improve the quality of the semiconductor film. This can involve an O₂-plasma or UV-Ozone treatment to clean the surface and modify its energy, promoting better crystal growth.[15]

-

Semiconductor Deposition: The C8-BTBT active layer is deposited onto the treated dielectric surface using one of the methods described in section 5.1 (e.g., spin coating). The substrate may be heated during this process.

-

Annealing: The film is annealed (e.g., at 90-105 °C) to remove residual solvent and improve crystallinity.[17]

-

Electrode Deposition: Source and drain electrodes (typically Gold (Au) with an adhesion layer like Molybdenum Oxide (MoO₃)) are deposited on top of the C8-BTBT film through a shadow mask via thermal evaporation.[22]

-

Electrical Characterization: The completed device is placed in a probe station. A semiconductor parameter analyzer is used to apply voltages to the gate (V_g), source, and drain (V_d) electrodes and measure the resulting drain current (I_d). Transfer curves (I_d vs. V_g) and output curves (I_d vs. V_d) are measured to extract key parameters like field-effect mobility, threshold voltage, and on/off ratio.

Factors Influencing Charge Transport

Optimizing charge transport in C8-BTBT is a multi-faceted challenge. Device performance is not solely dependent on the molecule itself but is critically influenced by several external and interfacial factors.

-

Crystallinity & Grain Boundaries: Single crystals represent the ideal medium for transport, minimizing defects that can trap charge carriers. In polycrystalline films, grain boundaries act as scattering sites, impeding carrier motion and reducing overall mobility.

-

Dielectric Interface: The interface between the C8-BTBT crystal and the gate dielectric is crucial. Traps and defects at this interface can immobilize charge carriers, degrading mobility and device stability. Surface treatments that create a smooth, clean, and low-energy surface, such as UV-Ozone, can significantly enhance performance by promoting ordered growth and reducing trap density.[15][23]

-

Contact Resistance (R_c): A significant energy barrier can exist at the interface between the metal electrodes and the organic semiconductor, creating a Schottky barrier that impedes charge injection.[10] This contact resistance can dominate the total device resistance, especially in short-channel devices, leading to an underestimation of the intrinsic material mobility.[24] Using appropriate contact metals (e.g., Platinum), inserting buffer layers (e.g., MoO₃), or chemical doping can drastically reduce R_c.[1][22][25]

-

Chemical Doping: Introducing dopants, such as iodine, can increase the charge carrier concentration in the semiconductor. This can fill trap states and reduce the contact barrier, leading to a significant enhancement in measured mobility.[17][18]

References

- 1. g.ruc.edu.cn [g.ruc.edu.cn]

- 2. d-nb.info [d-nb.info]

- 3. refubium.fu-berlin.de [refubium.fu-berlin.de]

- 4. researchgate.net [researchgate.net]

- 5. Dichotomy between the band and hopping transport in organic crystals: insights from experiments - Physical Chemistry Chemical Physics (RSC Publishing) [pubs.rsc.org]

- 6. fiveable.me [fiveable.me]

- 7. academic.oup.com [academic.oup.com]

- 8. researchgate.net [researchgate.net]

- 9. Ultrahigh mobility and efficient charge injection in monolayer organic thin-film transistors on boron nitride - PMC [pmc.ncbi.nlm.nih.gov]

- 10. tandfonline.com [tandfonline.com]

- 11. pubs.aip.org [pubs.aip.org]

- 12. Crossover from Hopping to Band-Like Charge Transport in an Organic Semiconductor Model: Atomistic Nonadiabatic Molecular Dynamics Simulation - PMC [pmc.ncbi.nlm.nih.gov]

- 13. researchgate.net [researchgate.net]

- 14. Preparation of highly oriented single crystal arrays of C8-BTBT by epitaxial growth on oriented isotactic polypropylene - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 15. High mobility solution-processed C8-BTBT organic thin-film transistors via UV-ozone interface modification - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 16. researchgate.net [researchgate.net]

- 17. cris.unibo.it [cris.unibo.it]

- 18. ICMAB - Chemical Doping of the Organic Semiconductor C8-BTBT-C8 Using an Aqueous Iodine Solution for Device Mobility Enhancement [icmab.es]

- 19. pubs.aip.org [pubs.aip.org]

- 20. pure.kaist.ac.kr [pure.kaist.ac.kr]

- 21. pubs.aip.org [pubs.aip.org]

- 22. researchgate.net [researchgate.net]

- 23. High mobility solution-processed C8-BTBT organic thin-film transistors via UV-ozone interface modification | Semantic Scholar [semanticscholar.org]

- 24. researchgate.net [researchgate.net]

- 25. researchgate.net [researchgate.net]

An In-depth Technical Guide to the Electronic Band Structure of C8-BTBT

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides a comprehensive analysis of the electronic band structure of 2,7-dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT), a high-performance organic semiconductor. A thorough understanding of its electronic properties is crucial for its application in advanced electronic devices. This document summarizes key quantitative data, details experimental methodologies, and visualizes fundamental concepts related to its electronic structure and charge transport.

Quantitative Electronic Properties of C8-BTBT

The electronic characteristics of C8-BTBT are highly dependent on factors such as molecular packing, film morphology, and the dielectric interface. The following table summarizes key quantitative data from various experimental and theoretical studies.

| Parameter | Value | Measurement/Calculation Method | Conditions/Substrate | Reference |

| Hole Mobility (μh) | Up to 43 cm²/Vs | Organic Field-Effect Transistor (OFET) | Solution-processed, off-center spin-coating | [2] |

| 18 cm²/Vs | Thin-Film Transistor (TFT) | Solution-processed, varied gate dielectrics | [3] | |

| 15 cm²/Vs | Kelvin Probe Force Microscopy (KPFM) in operating OFETs | Solution-sheared C8-BTBT:PS blend | [2] | |

| 6.50 cm²/Vs | Solution-processed OTFT | UV-ozone treated SiO2 | [4] | |

| 4.36 cm²/Vs | Ultrathin (~320 nm) flexible OTFT | Spin-coated on PVA | [5] | |

| 3.43 cm²/Vs -> 3.04 cm²/Vs | Flexible OTFT | On flat vs. curved surface | [5][6] | |

| 2.39 cm²/Vs | Flexible OTFT with AlOx gate dielectric | Sputtered AlOx | [7] | |

| 0.6 ± 0.3 cm²/Vs | OFET with µ-contact printed electrodes | PEDOT:PSS/MWCNT electrodes | [8] | |

| Band Gap | 3.84 eV | Photoemission Spectroscopy (PES) | C8-BTBT/C60/SiO2 interfaces | [9] |

| Ionization Potential (IP) | Decreases with increasing film thickness | Ultraviolet Photoemission Spectroscopy (UPS) | C8-BTBT on SiO2 | [10] |

| Decreases with increasing molecular tilt angle | Photoemission Spectroscopy (PES) | C8-BTBT on HOPG | [11] | |

| Valence Band (VB) Bandwidth | ~0.84 eV (along a-axis) | Density Functional Theory (DFT) | Theoretical | [12] |

| Highest Occupied Molecular Orbital (HOMO) Level | Shifts downward with increasing film thickness | UPS and X-ray Photoemission Spectroscopy (XPS) | C8-BTBT on SiO2 | [10] |

| 1.77 eV below Fermi level (at 8 nm thickness) | UPS | C8-BTBT on C60/SiO2 | [9] |

Experimental Protocols

Detailed methodologies are essential for reproducing and building upon existing research. The following sections describe the key experimental protocols used to characterize the electronic structure of C8-BTBT.

Density Functional Theory (DFT) Calculations

DFT is a computational quantum mechanical modeling method used to investigate the electronic structure of materials.

Objective: To calculate the electronic band structure, density of states (DOS), and charge transport properties of C8-BTBT.

Methodology:

-

Structural Optimization: The crystal structure of C8-BTBT is first optimized to find the lowest energy configuration. This is typically done using a functional like B3LYP with a basis set such as 6-31G*.

-

Band Structure Calculation: The electronic band structure is then calculated along high-symmetry directions in the Brillouin zone. This reveals the energy of the valence and conduction bands and the band gap.

-

Charge Transport Parameters: Parameters relevant to charge transport, such as intermolecular transfer integrals (related to orbital overlap) and reorganization energies, are calculated. These are used to estimate charge carrier mobility. For instance, hole mobility can be calculated as a function of molecular tilt angle to understand the impact of molecular packing.[13]

-

Software: Quantum chemistry software packages like Gaussian or VASP are commonly used for these calculations.

Photoemission Spectroscopy (PES)

PES techniques, including Angle-Resolved Photoemission Spectroscopy (ARPES), Ultraviolet Photoemission Spectroscopy (UPS), and X-ray Photoemission Spectroscopy (XPS), are powerful tools for directly probing the occupied electronic states of materials.[14]

Objective: To determine the energy levels of the HOMO, work function (WF), ionization potential (IP), and to observe band bending at interfaces.

Methodology:

-

Sample Preparation: Thin films of C8-BTBT are deposited on a substrate (e.g., highly oriented pyrolytic graphite (B72142) (HOPG) or SiO2) in an ultra-high vacuum (UHV) chamber.[11] The film thickness can be controlled and monitored using a quartz crystal microbalance.

-

Photon Source: The sample is irradiated with photons of a specific energy. A He I (21.2 eV) ultraviolet lamp is typically used for UPS, while a monochromatic Al Kα (1486.7 eV) X-ray source is used for XPS.[11]

-

Electron Energy Analysis: The kinetic energy of the photoemitted electrons is measured using a hemispherical energy analyzer.

-

Data Analysis:

-

UPS: The HOMO level is determined from the leading edge of the valence band spectrum. The work function is calculated from the secondary electron cutoff. The ionization potential is the sum of the HOMO binding energy and the work function.

-

XPS: Core-level spectra (e.g., S 2s) are measured to study chemical states and band bending, which is observed as a shift in the core-level binding energies with increasing film thickness.[9][10]

-

ARPES: By measuring the kinetic energy and emission angle of the photoelectrons, the band structure (energy versus momentum, E(k)) can be mapped out.[14][15][16]

-

Organic Field-Effect Transistor (OFET) Fabrication and Mobility Measurement

The charge carrier mobility is a key performance metric for a semiconductor and is often measured using an OFET device structure.

Objective: To fabricate C8-BTBT based OFETs and measure the field-effect hole mobility.

Methodology:

-

Substrate and Gate Electrode: A heavily doped silicon wafer with a thermally grown SiO2 layer is commonly used as the substrate, where the silicon acts as the gate electrode and the SiO2 as the gate dielectric.

-

Dielectric Surface Treatment: The SiO2 surface can be treated, for example with UV-ozone, to improve the interface quality, which influences the growth and performance of the C8-BTBT film.[4]

-

Semiconductor Deposition: A solution of C8-BTBT in a suitable organic solvent is deposited onto the dielectric layer. Techniques like spin-coating or solution-shearing are used to create a thin film.[2][5]

-

Source and Drain Electrode Deposition: Source and drain electrodes (e.g., gold) are deposited on top of the semiconductor film through a shadow mask using thermal evaporation. This creates a top-contact, bottom-gate device architecture.

-

Electrical Characterization: The transfer and output characteristics of the OFET are measured using a semiconductor parameter analyzer.

-

Mobility Extraction: The field-effect mobility (µ) is calculated from the transfer characteristics in the saturation regime using the following equation: IDS = (µCiW)/(2L*) (VGS - Vth)² where IDS is the drain-source current, Ci is the capacitance per unit area of the gate dielectric, W and L are the channel width and length, VGS is the gate-source voltage, and Vth is the threshold voltage.

Visualizations

The following diagrams illustrate key concepts related to the electronic structure and charge transport in C8-BTBT.

References

- 1. researchgate.net [researchgate.net]

- 2. researchgate.net [researchgate.net]

- 3. pubs.acs.org [pubs.acs.org]

- 4. High mobility solution-processed C8-BTBT organic thin-film transistors via UV-ozone interface modification - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 5. 320-nm Flexible Solution-Processed 2,7-dioctyl[1] benzothieno[3,2-b]benzothiophene Transistors [mdpi.com]

- 6. researchgate.net [researchgate.net]

- 7. pubs.aip.org [pubs.aip.org]

- 8. d-nb.info [d-nb.info]

- 9. researchgate.net [researchgate.net]

- 10. The correlations of the electronic structure and film growth of 2,7-diocty[1]benzothieno[3,2-b]benzothiophene (C8-BTBT) on SiO2. | Semantic Scholar [semanticscholar.org]

- 11. pubs.aip.org [pubs.aip.org]

- 12. researchgate.net [researchgate.net]

- 13. researchgate.net [researchgate.net]

- 14. Angle-Resolved Photoemission Spectroscopy (ARPES) Program [als.lbl.gov]

- 15. mdpi.com [mdpi.com]

- 16. ex7.iphy.ac.cn [ex7.iphy.ac.cn]

Polymorphism in C8-BTBT Thin Films: An In-depth Technical Guide

Authored for Researchers, Scientists, and Drug Development Professionals

Abstract

2,7-dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT) is a high-performance organic semiconductor renowned for its excellent charge transport properties, making it a cornerstone material for next-generation flexible electronics. The performance of C8-BTBT-based devices is intrinsically linked to the molecular packing and crystalline order within the thin film, which is governed by a phenomenon known as polymorphism. This technical guide provides a comprehensive overview of the polymorphic behavior of C8-BTBT thin films, detailing the various crystalline structures, their formation through different fabrication protocols, and their characterization. Quantitative data are summarized for comparative analysis, and key experimental methodologies are described. Furthermore, logical and experimental workflows are visualized to elucidate the complex interplay of factors governing polymorphism in this critical material.

Introduction to Polymorphism in C8-BTBT

Polymorphism refers to the ability of a solid material to exist in more than one crystalline form. In the context of organic semiconductors like C8-BTBT, different polymorphs exhibit distinct molecular arrangements, which in turn significantly influence the material's electronic properties, such as charge carrier mobility. The C8-BTBT molecule, with its rigid benzothienobenzothiophene core and flexible octyl side chains, displays a rich polymorphic landscape.[1][2] The orientation and packing of the π-conjugated cores are crucial for efficient charge transport, and controlling the formation of specific polymorphs is a key challenge in device fabrication.[3]

C8-BTBT typically crystallizes in a monoclinic structure, characterized by a lamella-like arrangement where the molecules are organized in a herringbone pattern.[1] This packing is beneficial for two-dimensional charge transport.[1] However, metastable polymorphs and surface-induced phases (SIPs) can also form, depending on the processing conditions.[2][4] For instance, a metastable polymorph has been observed in single-crystalline C8-BTBT rods, which can be influenced by the molecular weight of polymer additives like poly(methyl methacrylate) (PMMA).[2] Furthermore, temperature-induced polymorphic transitions have been reported, highlighting the dynamic nature of the crystalline structure.[5]

Fabrication of Polymorphic C8-BTBT Thin Films

The choice of deposition technique and the precise control of processing parameters are critical in directing the crystallization of C8-BTBT into a desired polymorphic form. Common fabrication methods include solution-based techniques like spin-coating and solution shearing, as well as physical vapor deposition.

Solution-Based Deposition

Spin-Coating: This widely used technique involves depositing a solution of C8-BTBT onto a spinning substrate. The rapid evaporation of the solvent kinetically traps the molecules into a specific arrangement.[6] The spinning speed is a crucial parameter, influencing the film thickness and the solvent evaporation rate, which in turn affects the resulting film morphology and crystal structure.[6] The addition of insulating binder polymers, such as polystyrene (PS), can improve film uniformity.[7]

Solution Shearing (Bar-Assisted Meniscus Shearing - BAMS): This technique allows for the growth of large-area, highly crystalline films.[8] A blade is used to spread the semiconductor solution over the substrate at a controlled speed and temperature. This method can produce highly aligned crystalline domains.

Off-Center Spin Coating: This is a variation of spin-coating where the substrate is placed away from the axis of the spin-coater, which can be used to fabricate highly aligned metastable C8-BTBT films when blended with polymers like polystyrene.[9]

Physical Vapor Deposition (PVD)

PVD is a solvent-free method where C8-BTBT is evaporated in a high vacuum and then condensed onto a substrate. This technique offers excellent control over film thickness and purity. The substrate temperature during deposition is a critical parameter that influences the molecular packing and the resulting polymorph.[4]

Post-Deposition Treatments

Thermal Annealing: Annealing the thin films after deposition can induce phase transitions to more thermodynamically stable polymorphs.[3] The annealing temperature and cooling rate are key parameters to control the final crystalline structure.[10] Directional crystallization can be achieved using a temperature gradient, which can improve the crystalline order of the thin films.[11]

Solvent Vapor Annealing (SVA): Exposing the film to a solvent vapor atmosphere can enhance molecular mobility and promote the formation of highly ordered crystalline domains.[2]

Characterization of C8-BTBT Polymorphs

A suite of characterization techniques is employed to identify the different polymorphs and to correlate their structural features with their electronic properties.

-

Polarized Optical Microscopy (POM): POM is a straightforward technique to visualize the morphology and crystalline domains in the thin film. The birefringence of the crystalline material leads to contrast that reveals the size, shape, and orientation of the crystallites.[2]

-

Atomic Force Microscopy (AFM): AFM provides high-resolution topographical images of the film surface, revealing details about the molecular layering, grain boundaries, and surface roughness.[12]

-

X-ray Diffraction (XRD): XRD is a powerful technique to determine the crystal structure and interlayer spacing of the polymorphs. Specular XRD provides information about the out-of-plane molecular orientation.[12]

-

Grazing Incidence Wide-Angle X-ray Scattering (GIWAXS): GIWAXS is particularly suited for thin-film characterization, providing information about both in-plane and out-of-plane molecular packing.[2][13] It is instrumental in identifying different polymorphs and their orientation with respect to the substrate.[5]

-

Selected Area Electron Diffraction (SAED): SAED, performed in a transmission electron microscope (TEM), can be used to confirm the single-crystalline nature of individual domains.[12]

Quantitative Data Summary

The following tables summarize key quantitative data extracted from the literature, providing a comparative overview of the properties of different C8-BTBT polymorphs and the performance of devices fabricated under various conditions.

Table 1: Structural Parameters of C8-BTBT Polymorphs

| Polymorph/Phase | Crystal System | Key Lattice Parameters | Interlayer Spacing (d-spacing) | Molecular Orientation | Reference |

| Bulk Crystal | Monoclinic | - | ~2.94 nm | Herringbone packing | [1][14] |

| Thin-Film Phase (Metastable) | - | - | ~3.2 nm | Standing-up orientation | [14] |

| Surface-Induced Phase (SIP) | - | - | - | Lamellar arrangement with herringbone packing | [4] |

| High-Temperature Phase (HTP) | - | Enlarged in-plane unit cell | - | Tilted with respect to surface normal | [4][5] |

Table 2: Electronic Properties of C8-BTBT Thin-Film Transistors (OFETs)

| Fabrication Method | Post-Treatment | Mobility (µ) (cm²/Vs) | On/Off Ratio | Substrate/Dielectric | Reference |

| Spin-Coating | - | 0.3 ± 0.2 | 3 x 10³ | Al₂O₃ | [15] |

| Spin-Coating | - | Up to 4.36 | > 10⁶ | PVA | [16] |

| Solution Shearing (BAMS) | Iodine Doping | > 1 (enhanced) | - | SiO₂ | |

| Off-Center Spin Coating (C8-BTBT:PS blend) | - | - | - | PVP:HDA | [9] |

| Vacuum Deposition (with precursor film) | - | > 2 | - | SiO₂/Si | |

| Directional Crystallization | Temperature Gradient | - | - | Glass | [11] |

Experimental Protocols

Protocol for Spin-Coating of C8-BTBT Thin Films

-

Solution Preparation: Dissolve C8-BTBT in a suitable organic solvent (e.g., toluene, chlorobenzene) at a specific concentration (e.g., 2.5 mg/mL).[15] If using a polymer blend, co-dissolve C8-BTBT and the polymer (e.g., polystyrene) in the desired ratio.

-

Substrate Preparation: Clean the substrate (e.g., Si/SiO₂, glass) thoroughly using a sequence of sonication in acetone, and isopropanol, followed by drying with nitrogen. A surface treatment (e.g., UV-ozone or plasma treatment) may be applied to modify the surface energy.

-

Spin-Coating: Dispense the C8-BTBT solution onto the center of the substrate. Spin the substrate at a defined speed (e.g., 2500 rpm) for a specific duration (e.g., 40 s).[15] The spinning speed and time determine the final film thickness.

-

Annealing (Optional): Transfer the coated substrate to a hotplate for thermal annealing at a specific temperature (e.g., 90-130 °C) for a defined time to improve crystallinity.[17]

Protocol for GIWAXS Characterization

-

Sample Mounting: Mount the C8-BTBT thin film sample on a goniometer within the GIWAXS experimental chamber.

-

X-ray Beam Alignment: Align the monochromatic X-ray beam at a shallow grazing incidence angle (typically below the critical angle of the substrate) to maximize the signal from the thin film while minimizing the substrate contribution.

-

Data Acquisition: Expose the sample to the X-ray beam and collect the scattered X-rays on a 2D detector. The acquisition time will depend on the sample's scattering power and the X-ray source intensity.

-

Data Analysis: The resulting 2D scattering pattern is analyzed to extract information about the molecular packing. The positions of the diffraction peaks in the in-plane (qxy) and out-of-plane (qz) directions are used to determine the unit cell parameters and the molecular orientation.[13]

Visualized Workflows and Relationships

The following diagrams, generated using the DOT language, illustrate key experimental workflows and the logical relationships governing polymorphism in C8-BTBT thin films.

Caption: Experimental workflow for fabricating and characterizing C8-BTBT thin films.

Caption: Factors influencing polymorphism and its impact on electronic properties.

Conclusion

The polymorphic behavior of C8-BTBT is a critical aspect that dictates the performance of thin-film devices. This guide has provided a detailed overview of the known polymorphs, the experimental techniques to control their formation, and the methods for their characterization. By understanding and manipulating the delicate interplay between processing conditions and crystalline structure, researchers can unlock the full potential of C8-BTBT for advanced electronic applications. The presented data and workflows serve as a valuable resource for scientists and engineers working to optimize the performance and reliability of organic electronic devices.

References

- 1. researchgate.net [researchgate.net]

- 2. researchgate.net [researchgate.net]

- 3. Polar Polymorphism: A New Intermediate Structure toward the Thin-Film Phase in Asymmetric Benzothieno[3,2-b][1]-benzothiophene Derivatives - PMC [pmc.ncbi.nlm.nih.gov]

- 4. digital.csic.es [digital.csic.es]

- 5. pubs.rsc.org [pubs.rsc.org]

- 6. pubs.aip.org [pubs.aip.org]

- 7. api.repository.cam.ac.uk [api.repository.cam.ac.uk]

- 8. cris.unibo.it [cris.unibo.it]

- 9. researchgate.net [researchgate.net]

- 10. pubs.acs.org [pubs.acs.org]

- 11. Directional crystallization of C8-BTBT-C8 thin films in a temperature gradient - Materials Chemistry Frontiers (RSC Publishing) [pubs.rsc.org]

- 12. researchgate.net [researchgate.net]

- 13. researchgate.net [researchgate.net]

- 14. researchgate.net [researchgate.net]

- 15. d-nb.info [d-nb.info]

- 16. 320-nm Flexible Solution-Processed 2,7-dioctyl[1] benzothieno[3,2-b]benzothiophene Transistors [mdpi.com]

- 17. researchgate.net [researchgate.net]

C8-BTBT highest occupied molecular orbital (HOMO) level

An In-depth Technical Guide to the Highest Occupied Molecular Orbital (HOMO) Level of C8-BTBT

The highest occupied molecular orbital (HOMO) is a critical parameter for organic semiconductor materials like 2,7-dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT). Its energy level dictates the material's ionization potential, air stability, and the efficiency of hole injection from electrodes in electronic devices such as organic field-effect transistors (OFETs). This guide provides a comprehensive overview of the HOMO level of C8-BTBT, detailing experimental and theoretical determination methods, and presenting key quantitative data for researchers and professionals in materials science and drug development.

Data Presentation: HOMO Level of C8-BTBT

The HOMO level of C8-BTBT is not a singular value but is highly dependent on the material's physical state, including film thickness, molecular orientation, and the substrate upon which it is deposited. The following table summarizes experimentally determined values.

| Method | Substrate | Film Thickness / Condition | HOMO Level / Ionization Potential (IP) | Notes |

| UPS | HOPG | Thin film (<2.0 nm, lying-down molecules) | IP: ~5.8 eV | The HOMO edge shows significant downward band bending (~0.4 eV) as thickness increases.[1] |

| UPS | HOPG | Thick film (>2.0 nm, standing-up molecules) | IP: ~5.45 eV | The offset between the C8-BTBT HOMO level and the Fermi level of HOPG is approximately 1.4 eV.[1] |

| UPS | C60 (4nm) / SiO2 | 0.5 nm | 1.56 eV (Binding Energy below E_F) | The HOMO level shifts to higher binding energy with increasing film thickness.[2] |

| UPS | C60 (4nm) / SiO2 | 8.0 nm | 1.77 eV (Binding Energy below E_F) | A total shift of 0.21 eV toward higher binding energy was observed.[2] |

| CV | - | In Solution (for C6-Ph-BTBT) | -5.65 eV | Data for a closely related BTBT derivative provides a good estimate for C8-BTBT in solution.[3] |

| DFT | - | Calculated (for a BTBT derivative) | -5.41 eV | Theoretical values often differ slightly from experimental results but show similar trends.[4] |

Note: Ultraviolet Photoelectron Spectroscopy (UPS) measures the binding energy relative to the sample's Fermi level (E_F) or the ionization potential (the energy required to remove an electron from the HOMO to the vacuum level). Cyclic Voltammetry (CV) in solution provides an estimate of the absolute HOMO energy level in electron volts (eV).

Experimental Protocols

The determination of the HOMO energy level is primarily achieved through two key experimental techniques: Ultraviolet Photoelectron Spectroscopy (UPS) for thin films and Cyclic Voltammetry (CV) for materials in solution.

Ultraviolet Photoelectron Spectroscopy (UPS)

UPS is a surface-sensitive technique used to probe the valence electronic states of a material.[5][6]

Methodology:

-

System & Environment: The experiment is conducted in a multi-chamber ultra-high vacuum (UHV) system to prevent surface contamination.

-

Sample Preparation:

-

The substrate (e.g., Highly Oriented Pyrolytic Graphite - HOPG) is freshly cleaved and degassed in the UHV chamber at elevated temperatures (e.g., 450 °C for 36 hours) to ensure a clean surface.[1]

-

Purified C8-BTBT is thermally evaporated from an effusion cell at approximately 110 °C onto the substrate, which is maintained at room temperature (27 °C).[1]

-

The deposition rate is monitored using a Quartz Crystal Microbalance (QCM) at a slow rate (e.g., 0.1-0.2 nm/min) to ensure controlled growth. Film thickness is controlled by varying the deposition time.[1]

-

-

Measurement:

-

The sample is irradiated with ultraviolet photons from a gas discharge lamp, typically a He I source emitting photons with an energy of 21.2 eV.[1][7]

-

The kinetic energy of the photoemitted electrons is measured using a hemispherical energy analyzer.[1]

-

To determine the work function and the secondary electron cutoff edge, the sample is typically biased with a negative voltage (e.g., -5 V).[1]

-

-

Data Analysis:

-

The UPS spectrum displays the density of valence states.

-

The HOMO onset (E_HOMO) is determined by the linear extrapolation of the leading edge of the spectrum in the low binding energy region.[1][8]

-

The Ionization Potential (IP) is calculated using the formula: IP = hν - (E_cutoff - E_HOMO), where hν is the photon energy, E_cutoff is the secondary electron cutoff, and E_HOMO is the HOMO onset energy.

-

Cyclic Voltammetry (CV)

CV is an electrochemical method used to determine the oxidation and reduction potentials of a molecule in solution, from which the HOMO and LUMO energy levels can be estimated.[9][10]

Methodology:

-

System & Environment:

-

A standard three-electrode electrochemical cell is used, consisting of a working electrode (e.g., glassy carbon or platinum), a reference electrode (e.g., Ag/AgCl), and a counter electrode (e.g., platinum wire).[9]

-

The measurement is performed under an inert atmosphere (e.g., nitrogen or argon) to exclude oxygen and moisture.

-

-

Sample Preparation:

-

The C8-BTBT material is dissolved in a suitable solvent (e.g., anhydrous acetonitrile) containing a supporting electrolyte (e.g., 0.1 M tetrabutylammonium (B224687) hexafluorophosphate (B91526) - TBAPF6) to ensure conductivity.[9]

-

-

Measurement:

-

A potentiostat is used to sweep the potential of the working electrode linearly with time.

-

The potential is scanned from an initial value to a vertex potential and then back, while the resulting current is measured.

-

To accurately calibrate the energy levels, an internal standard with a known redox potential, such as ferrocene (B1249389) (Fc), is added to the solution, and the voltammogram is measured again.[11]

-

-

Data Analysis:

-

The resulting plot of current vs. potential is called a cyclic voltammogram.

-

The onset of the first oxidation peak (E_ox_onset) is determined from the voltammogram.

-

The HOMO energy level is calculated relative to the vacuum level using the potential of the ferrocene/ferrocenium (Fc/Fc+) redox couple as a reference. A common empirical equation is: E_HOMO (eV) = - [E_ox_onset (vs Fc/Fc+) + C] where C is a constant that relates the Fc/Fc+ couple to the vacuum level, typically valued between 4.8 eV and 5.1 eV.[11]

-

Mandatory Visualization

The following diagrams illustrate the logical workflow for determining the HOMO level of C8-BTBT and the relationship between molecular orientation and energy levels.

References

- 1. pubs.aip.org [pubs.aip.org]

- 2. researchgate.net [researchgate.net]

- 3. web.pkusz.edu.cn [web.pkusz.edu.cn]

- 4. mdpi.com [mdpi.com]

- 5. Ultraviolet Photoelectron Spectroscopy:Practical Aspects and Best Practices | Universal Lab Blog [universallab.org]

- 6. researchgate.net [researchgate.net]

- 7. Photoelectron Spectroscopy | Ultraviolet Photoelectron Spectroscopy | Thermo Fisher Scientific - HK [thermofisher.com]

- 8. researchgate.net [researchgate.net]

- 9. scientificbulletin.upb.ro [scientificbulletin.upb.ro]

- 10. researchgate.net [researchgate.net]

- 11. researchgate.net [researchgate.net]

An In-Depth Technical Guide to the Synthesis of C8-BTBT Derivatives

For Researchers, Scientists, and Drug Development Professionals

This technical guide provides a comprehensive overview of the synthetic routes for C8-BTBT ([1]benzothieno[3,2-b][1]benzothiophene) derivatives, a class of organic semiconductors crucial for the development of advanced electronic devices. This document details the synthesis of the core BTBT structure and the subsequent functionalization to introduce C8 alkyl chains and other derivatives, presenting key experimental protocols and quantitative data to aid in research and development.

Synthesis of the Unsubstituted[1]Benzothieno[3,2-b][1]benzothiophene (BTBT) Core

The foundation for all C8-BTBT derivatives is the synthesis of the parent BTBT molecule. A common and efficient method involves a one-step synthesis from commercially available o-chlorobenzaldehyde.[2][3]

One-Step Synthesis from o-Chlorobenzaldehyde

This procedure provides a direct route to the BTBT core.

Experimental Protocol:

A detailed experimental protocol for this one-step synthesis is often proprietary or varies between research groups. However, the general transformation involves the reaction of o-chlorobenzaldehyde with a sulfur source, such as sodium sulfide (B99878) or sodium hydrosulfide, at elevated temperatures.[2][3] The reaction proceeds through a domino sequence of reactions to form the fused thiophene (B33073) rings.

Synthesis of 2,7-Dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT)

The introduction of octyl chains at the 2 and 7 positions of the BTBT core enhances solubility and influences the self-assembly properties of the resulting organic semiconductor. A prevalent strategy involves a two-step process: Friedel-Crafts acylation followed by a Wolff-Kishner reduction.[4]

Route 1: Friedel-Crafts Acylation and Wolff-Kishner Reduction

This classic approach allows for the direct introduction of the octyl chains onto the BTBT core.

Step 1: Friedel-Crafts Acylation of BTBT

This reaction introduces an octanoyl group at the 2 and 7 positions of the BTBT core.

Experimental Protocol:

To a solution of[1]benzothieno[3,2-b][1]benzothiophene in a suitable solvent such as dichloromethane (B109758) or nitrobenzene, a Lewis acid catalyst, typically aluminum chloride (AlCl₃), is added.[5] Octanoyl chloride is then added dropwise at a controlled temperature, usually between 0 °C and room temperature. The reaction is stirred for several hours until completion. The reaction mixture is then quenched with ice water and the product is extracted with an organic solvent. The organic layer is washed, dried, and concentrated to yield 2,7-bis(octan-1-one)[1]benzothieno[3,2-b][1]benzothiophene (C7CO-BTBT).[5]

Step 2: Wolff-Kishner Reduction of C7CO-BTBT

The carbonyl groups of the acylated BTBT are reduced to methylene (B1212753) groups to form the final C8-BTBT product.

Experimental Protocol:

A mixture of 2,7-bis(octan-1-one)[1]benzothieno[3,2-b][1]benzothiophene (C7CO-BTBT), hydrazine (B178648) hydrate, and potassium hydroxide (B78521) is dissolved in a high-boiling solvent like diethylene glycol.[4] The mixture is heated to around 110 °C for an initial period and then the temperature is raised to approximately 210 °C to drive the reaction to completion. After cooling, the product is precipitated by adding water, filtered, and washed to give 2,7-dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT).

Synthesis Route for C8-BTBT

Caption: Friedel-Crafts acylation followed by Wolff-Kishner reduction to yield C8-BTBT.

Synthesis of other C8-BTBT Derivatives via Cross-Coupling Reactions

For the synthesis of a wider range of C8-BTBT derivatives with different functional groups, a common strategy involves the preparation of a di-halogenated BTBT intermediate, followed by cross-coupling reactions such as Suzuki or Stille coupling.

Synthesis of 2,7-Dibromo[1]benzothieno[3,2-b][1]benzothiophene

This dibrominated intermediate is a versatile precursor for various derivatives.

Experimental Protocol:

[1]Benzothieno[3,2-b][1]benzothiophene is dissolved in a suitable solvent like chloroform (B151607) or carbon tetrachloride. A brominating agent, such as N-bromosuccinimide (NBS) or bromine, is added in portions, often in the presence of a catalyst like iron(III) bromide. The reaction is typically carried out at room temperature and monitored until the starting material is consumed. The product, 2,7-dibromo[1]benzothieno[3,2-b][1]benzothiophene, is then isolated by filtration and purified by recrystallization.[3]

Suzuki Coupling for the Synthesis of Aryl- and Thienyl-Substituted BTBT Derivatives

The Suzuki coupling reaction is a powerful tool for forming carbon-carbon bonds between the brominated BTBT core and various boronic acids or esters.

Experimental Protocol:

2,7-dibromo[1]benzothieno[3,2-b][1]benzothiophene, a boronic acid or its pinacol (B44631) ester derivative (e.g., 4,4,5,5-tetramethyl-2-(3-octylthiophen-2-yl)-1,3,2-dioxaborolane), a palladium catalyst such as Pd(PPh₃)₄, and a base (e.g., aqueous sodium carbonate solution) are combined in a solvent mixture, typically toluene (B28343) and ethanol. The mixture is heated under an inert atmosphere for several hours. After completion, the product is extracted, and the organic phase is purified by column chromatography to yield the desired 2,7-disubstituted BTBT derivative.

Suzuki Coupling for BTBT Derivatization

Caption: General scheme for the synthesis of BTBT derivatives via Suzuki coupling.

Modular Synthesis of Unsymmetrical BTBT Derivatives

For the creation of asymmetrically substituted BTBT derivatives, a modular approach utilizing a Pummerer CH–CH-type cross-coupling and a Newman–Kwart rearrangement has been developed.[6] This method allows for the synthesis of a diverse library of materials from readily available starting materials.

Experimental Workflow:

-

Pummerer CH–CH-type Cross-Coupling: A benzothiophene (B83047) S-oxide is coupled with a phenol (B47542) derivative in the presence of an activating agent like trifluoroacetic anhydride (B1165640) (TFAA).[7][8]

-

Newman–Kwart Rearrangement: The resulting O-aryl thiocarbamate undergoes a thermal or palladium-catalyzed rearrangement to an S-aryl thiocarbamate.[9][10][11]

-

Cyclization: The S-aryl thiocarbamate is then cyclized to form the unsymmetrical BTBT core.

Modular Synthesis of Unsymmetrical BTBTs

Caption: Workflow for the modular synthesis of unsymmetrical BTBT derivatives.

Quantitative Data Summary

The following tables summarize the quantitative data for the key synthetic steps described above.

Table 1: Friedel-Crafts Acylation of BTBT

| Reactant | Reagent | Catalyst | Solvent | Temp. (°C) | Time (h) | Yield (%) | Reference |

| BTBT | Octanoyl chloride | AlCl₃ | CH₂Cl₂ | 0 - RT | 2-4 | 60-70 | [5] |

Table 2: Wolff-Kishner Reduction of C7CO-BTBT

| Reactant | Reagents | Solvent | Temp. (°C) | Time (h) | Yield (%) | Reference |

| C7CO-BTBT | Hydrazine hydrate, KOH | Diethylene glycol | 110 then 210 | 1 + 5 | >90 | [4] |

Table 3: Suzuki Coupling of 2,7-Dibromo-BTBT

| Reactant | Boronic Ester | Catalyst | Base | Solvents | Temp. (°C) | Time (h) | Yield (%) | Reference |

| 2,7-Dibromo-BTBT | 3-octylthiophene-2-yl boronic acid pinacol ester | Pd(PPh₃)₄ | Na₂CO₃ (aq) | Toluene, Ethanol | Reflux | 6 | ~60 |

This guide provides a foundational understanding of the primary synthetic routes to C8-BTBT and its derivatives. Researchers are encouraged to consult the cited literature for more detailed experimental procedures and characterization data. The versatility of the BTBT core and the various synthetic methodologies available allow for the creation of a wide array of functional materials for advanced electronic applications.

References

- 1. semanticscholar.org [semanticscholar.org]

- 2. researchgate.net [researchgate.net]

- 3. mdpi.com [mdpi.com]

- 4. pubs.acs.org [pubs.acs.org]

- 5. researchgate.net [researchgate.net]

- 6. Modular synthesis of unsymmetrical [1]benzothieno[3,2-b][1]benzothiophene molecular semiconductors for organic transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- 9. Newman–Kwart rearrangement - Wikipedia [en.wikipedia.org]

- 10. Newman-Kwart Rearrangement [organic-chemistry.org]

- 11. Newman-Kwart Rearrangement | Chem-Station Int. Ed. [en.chem-station.com]

An In-depth Technical Guide to the Thermal Stability Analysis of C8-BTBT

Introduction

2,7-dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT) is a high-performance organic semiconductor that has garnered significant attention for its excellent charge transport properties, solution processability, and environmental stability.[2] These characteristics make it a prime candidate for next-generation electronic applications, including organic field-effect transistors (OFETs) and flexible electronics.[3] The performance and long-term reliability of devices fabricated from C8-BTBT are intrinsically linked to its thermal stability. Understanding its behavior at elevated temperatures is crucial for optimizing device fabrication processes, such as thermal annealing, and for ensuring operational stability.[2] This guide provides a detailed overview of the thermal properties of C8-BTBT, outlines the standard experimental protocols for its analysis, and presents a visual workflow of the analytical process.

Quantitative Thermal Analysis Data

The thermal stability of C8-BTBT is primarily characterized by its decomposition temperature and its phase transition behavior. These properties are typically determined using Thermogravimetric Analysis (TGA) and Differential Scanning Calorimetry (DSC).

| Thermal Property | Value (°C) | Analytical Method | Reference |

| Decomposition Temperature (Td) | > 350 °C | TGA | [4] (Typical for related compounds) |

| Phase Transition: Crystal to Smectic A (SmA) | ~109.5 °C | DSC | [5] (Derived from experimental data) |

| Phase Transition: Smectic A (SmA) to Isotropic Liquid | ~125 °C | DSC | [5] (Derived from experimental data) |

Note: The decomposition temperature represents the onset of significant mass loss, typically defined at 5% weight loss under an inert atmosphere.

C8-BTBT exhibits liquid crystalline behavior, which is critical for processing thin films with high crystalline order.[5][6] Upon heating, the material transitions from a solid crystalline state to a more ordered liquid crystal phase (Smectic A) before melting into an isotropic liquid.[5] This behavior can be leveraged during thermal annealing to produce large, uniform crystalline domains essential for high-performance devices.[7]

Experimental Protocols

Precise and reproducible thermal analysis requires standardized experimental procedures. The following protocols for TGA and DSC are based on established methodologies for organic semiconductor materials.

Thermogravimetric Analysis (TGA)

TGA measures the change in mass of a sample as a function of temperature in a controlled atmosphere.[8] It is the primary method for determining the decomposition temperature.

Objective: To determine the thermal stability and decomposition temperature (Td) of C8-BTBT.

Methodology:

-

Instrumentation: A calibrated thermogravimetric analyzer, such as a Mettler Toledo TGA/SDTA 851e or a TA Instruments TGA 2950, is used.[9]

-

Sample Preparation:

-

Experimental Conditions:

-

The crucible is loaded into the TGA furnace.

-

An inert gas, typically high-purity nitrogen or argon, is purged through the furnace at a constant flow rate (e.g., 30-50 mL/min) to prevent oxidative degradation.[9][10]

-

The sample is subjected to a dynamic heating program, typically a linear ramp from room temperature (e.g., 40 °C) to a final temperature (e.g., 600 °C) at a rate of 10 °C/min.[10]

-

-

Data Analysis:

-

The instrument records the sample mass as a function of temperature.

-

The resulting TGA curve (thermogram) plots the percentage of initial mass versus temperature.

-

The decomposition temperature (Td) is determined as the temperature at which a specific amount of mass loss (commonly 5%) occurs. The onset temperature of the major decomposition step can also be reported.

-

Differential Scanning Calorimetry (DSC)

DSC is a thermoanalytical technique that measures the difference in heat flow required to increase the temperature of a sample and a reference.[11] It is used to detect thermal transitions such as melting, crystallization, and liquid crystal phase changes.[11][12]

Objective: To identify and characterize the phase transition temperatures of C8-BTBT.

Methodology:

-

Instrumentation: A calibrated differential scanning calorimeter, such as a TA Instruments MDSC 2920, is employed.[12]

-

Sample Preparation:

-

A small amount of C8-BTBT (typically 2-5 mg) is weighed into a clean aluminum DSC pan.

-

The pan is hermetically sealed to ensure a controlled atmosphere and prevent sublimation.

-

-

Experimental Conditions:

-

The sealed sample pan and an empty, sealed reference pan are placed into the DSC cell.

-

The cell is purged with an inert gas (e.g., nitrogen) to maintain an inert environment.

-

A temperature program is initiated. A typical program for C8-BTBT involves heating the sample from a low temperature (e.g., -40 °C) to a temperature above its final melting point (e.g., 150 °C) at a controlled rate (e.g., 10-20 °C/min).[12][13] A subsequent cooling and second heating cycle is often performed to observe the behavior on cooling and to erase any prior thermal history.

-

-

Data Analysis:

-

The DSC thermogram plots heat flow versus temperature.

-

Endothermic events (e.g., melting, liquid crystal transitions) appear as peaks, while exothermic events (e.g., crystallization) appear as valleys.[12]

-

The peak temperature or onset temperature of these thermal events is used to identify the phase transition temperatures.

-

Mandatory Visualization

Workflow for Thermal Stability Analysis

The logical flow for a comprehensive thermal analysis of C8-BTBT involves sequential characterization using TGA and DSC, followed by data integration and interpretation.

References

- 1. researchgate.net [researchgate.net]

- 2. researchgate.net [researchgate.net]

- 3. d-nb.info [d-nb.info]

- 4. researchgate.net [researchgate.net]

- 5. Exploring the phase behavior of C8-BTBT-C8 at ambient and high temperatures: insights and challenges from molecular dynamics simulations - Physical Chemistry Chemical Physics (RSC Publishing) DOI:10.1039/D4CP01884B [pubs.rsc.org]

- 6. researchgate.net [researchgate.net]

- 7. Directional crystallization of C8-BTBT-C8 thin films in a temperature gradient - Materials Chemistry Frontiers (RSC Publishing) [pubs.rsc.org]

- 8. A Beginner's Guide to Thermogravimetric Analysis [xrfscientific.com]

- 9. epfl.ch [epfl.ch]

- 10. Thermogravimetric Analysis with ELTRA Elemental Analyzers [eltra.com]

- 11. Differential scanning calorimetry - Wikipedia [en.wikipedia.org]

- 12. cskscientificpress.com [cskscientificpress.com]

- 13. Effect of Heating and Cooling on 6CB Liquid Crystal Using DSC Technique | Engineering And Technology Journal [everant.org]

charge carrier dynamics in C8-BTBT films

An In-depth Technical Guide to Charge Carrier Dynamics in C8-BTBT Films

Abstract

2,7-dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT) is a leading p-type organic semiconductor renowned for its exceptional charge carrier mobility and solution processability, making it a cornerstone material for next-generation flexible and printed electronics.[2][3][4] The performance of C8-BTBT-based devices is intrinsically linked to the dynamics of its charge carriers—holes—as they move through the thin film. These dynamics are governed by a complex interplay of factors including the material's molecular packing, film morphology, interfacial properties, and the presence of electronic trap states.[5][6][7] This technical guide provides a comprehensive overview of the fundamental principles of charge transport in C8-BTBT films, summarizes key quantitative performance metrics, and details the critical experimental protocols used for its characterization. It is intended for researchers and scientists engaged in the development of organic electronic materials and devices.

Fundamentals of Charge Transport in C8-BTBT

Charge transport in C8-BTBT is dominated by the movement of holes through its conjugated core. The mechanism of this transport is not described by a single model but exists in a regime between classic band-like transport, seen in highly ordered single crystals, and hopping transport, which occurs between localized states in disordered regions.[5] Recent studies suggest a "transient localization" or "flickering polaron" model, where charge carriers are delocalized over several molecules (10-20) but are subject to constant changes in shape and extension due to thermal vibrations.[6][8]

The efficiency of charge transport is critically dependent on the supramolecular organization within the film. Strong π-π interactions between the planar BTBT cores of adjacent molecules create pathways for efficient charge delocalization.[4] Consequently, the degree of crystallinity, the size of crystalline domains, and the orientation of the molecules relative to the direction of current flow are paramount in achieving high charge carrier mobility.[4][6]

Key Parameters of Charge Carrier Dynamics

The performance of C8-BTBT as a semiconductor is quantified by several key parameters. Charge carrier mobility (μ) measures the velocity of charge carriers in response to an electric field. Trap density (Nt) quantifies the concentration of localized electronic states that can immobilize charge carriers, and contact resistance (Rc) represents the impedance to charge injection from the electrodes into the semiconductor.

Quantitative Data Summary

| Parameter | Reported Value | Film Preparation / Device Configuration | Reference |

| Hole Mobility (μ) | Up to 43 cm²/Vs | Optimized solution-processed devices | [2][3] |

| > 30 cm²/Vs (intrinsic) | Monolayer film on boron nitride | [9] | |

| 23.5 cm²/Vs (max) | Marangoni effect-controlled growth | [4] | |

| 6.31 cm²/Vs (avg) | Patterned liquid crystal films | [10] | |

| 7.0 cm²/Vs | Iodine-doped films | [10] | |

| 6.50 cm²/Vs | Solution-processed on UV-ozone treated SiO₂ | [7] | |

| Contact Resistance (Rc) | 100 Ω·cm | Monolayer on boron nitride with Au contacts | [9] |

| 8.8 kΩ·cm | FeCl₃ doping at contact interface (reduced from 200 kΩ·cm) | [10] | |

| Almost Ohmic | Iodine solution treatment | [11] | |

| Interfacial Trap Density (Nt) | ~2.3 x 10¹² eV⁻¹cm⁻² | Pristine C8-BTBT-C8 film | [12] |

| ~1.3 x 10¹² eV⁻¹cm⁻² | After iodine solution treatment | [12] |

Factors Influencing Charge Carrier Dynamics

The charge transport properties of C8-BTBT films are not solely an intrinsic property of the molecule but are heavily influenced by the film's physical and chemical environment.

-

Film Morphology and Crystallinity : The method of film deposition—such as spin-coating, dip-coating, or zone-casting—and subsequent treatments like solvent or thermal annealing, profoundly impact the film's crystalline structure.[7][13][14] Highly ordered, large-grain crystalline films with low defect density provide superior pathways for charge transport.[4]

-

Dielectric Interface : The interface between the C8-BTBT film and the gate dielectric is a critical region where charge transport occurs. A high-quality interface with minimal trap states is essential for high mobility.[7] Surface treatments of the dielectric, such as with UV-ozone, can clean the surface and modify its energy to promote better molecular ordering during film deposition.[7]

-

Chemical Doping : Intentionally introducing chemical dopants, such as iodine or iron(III) chloride (FeCl₃), can significantly enhance device performance.[10][11] Doping can improve charge injection by reducing the contact resistance and increase mobility by filling electronic trap states at the grain boundaries or the dielectric interface, making them electronically inactive.[11][12]

Experimental Protocols for Characterization

A variety of techniques are employed to measure and understand the .

Organic Field-Effect Transistor (OFET) Characterization

This is the most common method for evaluating the performance of C8-BTBT, yielding the field-effect mobility.

Methodology:

-

Substrate Preparation : A heavily doped silicon (p++ Si) wafer, acting as the gate electrode, with a thermally grown silicon dioxide (SiO₂) or other dielectric layer is cleaned using sonication in solvents like acetone (B3395972) and isopropanol.

-

Surface Treatment (Optional) : The dielectric surface may be treated, for example with UV-ozone, to improve the interface quality.[7]

-

Semiconductor Deposition : A solution of C8-BTBT in a solvent like toluene (B28343) is deposited onto the substrate via spin-coating or another solution-processing technique.[2] The film is often annealed to improve crystallinity.

-

Electrode Deposition : Source and drain electrodes (e.g., Gold) are deposited on top of the C8-BTBT film through a shadow mask using thermal evaporation, completing the top-contact, bottom-gate device architecture.

-

Electrical Measurement : The device is placed in a probe station. A source-measure unit is used to apply a gate voltage (Vg) and sweep the source-drain voltage (Vds), while measuring the source-drain current (Ids). This is repeated for various gate voltages to obtain the output and transfer characteristics.

-

Parameter Extraction : The field-effect mobility (μ) is typically calculated from the slope of the √Ids vs. Vg plot in the saturation regime.

Space-Charge-Limited Current (SCLC) Measurement

SCLC is a technique used to determine the bulk charge carrier mobility in a material by analyzing the current-voltage (I-V) characteristics of a single-carrier device.[15]

Methodology:

-

Device Fabrication : A diode-like structure is fabricated by sandwiching the C8-BTBT film between two electrodes. For measuring hole mobility, the electrodes must have work functions that allow for efficient hole injection and electron blocking.

-

Measurement : A voltage is applied across the device, and the resulting current is measured.

-

Analysis : At low voltages, the current is typically ohmic. As the voltage increases, the injected charge carrier density exceeds the intrinsic carrier density, and the current becomes limited by the buildup of space charge.[16][17] In this trap-free SCLC regime, the current density (J) is described by the Mott-Gurney law: J = (9/8)ε₀εᵣμ(V²/L³), where ε₀εᵣ is the permittivity of the material, V is the applied voltage, and L is the film thickness.[15]

-

Mobility Calculation : The mobility (μ) can be extracted by fitting the J vs. V² plot in the SCLC region.

Time-Resolved Microwave Conductivity (TRMC)

TRMC is a powerful contactless technique to probe the intrinsic mobility and charge carrier lifetime of semiconductor materials.[18][19]

Methodology:

-

Sample Placement : The C8-BTBT film on a substrate is placed in a resonant microwave cavity.

-

Photoexcitation : The sample is illuminated with a short, high-energy laser pulse (pump), which generates mobile charge carriers (electrons and holes) within the C8-BTBT film.[18]

-

Microwave Probe : The change in the microwave power reflected or transmitted by the cavity is monitored over time (probe). The mobile charge carriers absorb microwave energy, causing a transient change in the cavity's conductivity.[19]

-

Signal Detection : A fast detector measures this change in microwave power (ΔP) as a function of time after the laser pulse. The signal is proportional to the product of the number of photogenerated carriers (N) and their mobility (μ).

-

Data Analysis : The peak of the TRMC signal is proportional to the product of the charge carrier generation yield and the sum of electron and hole mobilities (φΣμ). By quantifying the number of absorbed photons, one can determine the intrinsic charge carrier mobility. The decay of the signal over time provides information about the charge carrier recombination dynamics and lifetime.[19]

Conclusion

The are a key determinant of its high performance in electronic devices. Achieving optimal hole mobility requires careful control over the film's morphology, crystallinity, and interfacial properties. Solution-processing techniques, combined with post-deposition treatments and strategic chemical doping, provide a versatile toolkit for tuning these characteristics. A thorough understanding and application of characterization methods such as OFET, SCLC, and TRMC measurements are essential for rational material design and the continued advancement of C8-BTBT-based organic electronics.

References

- 1. Measurement Methods for Charge Carrier Mobility in Organic Semiconductors [manu56.magtech.com.cn]

- 2. d-nb.info [d-nb.info]

- 3. mdpi.com [mdpi.com]

- 4. researchgate.net [researchgate.net]

- 5. pubs.acs.org [pubs.acs.org]

- 6. Impact of Nanoscale Morphology on Charge Carrier Delocalization and Mobility in an Organic Semiconductor - PMC [pmc.ncbi.nlm.nih.gov]

- 7. High mobility solution-processed C8-BTBT organic thin-film transistors via UV-ozone interface modification - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 8. discovery.ucl.ac.uk [discovery.ucl.ac.uk]

- 9. Ultrahigh mobility and efficient charge injection in monolayer organic thin-film transistors on boron nitride - PMC [pmc.ncbi.nlm.nih.gov]

- 10. researchgate.net [researchgate.net]

- 11. ICMAB - Chemical Doping of the Organic Semiconductor C8-BTBT-C8 Using an Aqueous Iodine Solution for Device Mobility Enhancement [icmab.es]

- 12. researchgate.net [researchgate.net]

- 13. pure.kaist.ac.kr [pure.kaist.ac.kr]

- 14. Directional crystallization of C8-BTBT-C8 thin films in a temperature gradient - Materials Chemistry Frontiers (RSC Publishing) [pubs.rsc.org]

- 15. Space Charge Limited Current (SCLC) for Mobility in Organic & Perovskite Semiconductors — Fluxim [fluxim.com]

- 16. researchgate.net [researchgate.net]

- 17. Space charge - Wikipedia [en.wikipedia.org]

- 18. Time resolved microwave conductivity - Wikipedia [en.wikipedia.org]

- 19. redalyc.org [redalyc.org]

Environmental Stability of C8-BTBT Films: A Technical Guide

An In-depth Technical Guide for Researchers, Scientists, and Drug Development Professionals

The organic semiconductor 2,7-dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT) has emerged as a frontrunner in the field of organic electronics due to its exceptional charge transport properties and solution processability. However, the long-term environmental stability of C8-BTBT thin-film transistors (OTFTs) remains a critical factor for their commercial viability. This technical guide provides a comprehensive overview of the environmental stability of C8-BTBT films, focusing on the effects of ambient air, humidity, and light. It includes a compilation of quantitative data, detailed experimental protocols, and visualizations of key degradation pathways and experimental workflows.

Impact of Environmental Stressors on C8-BTBT OTFT Performance

The electrical performance of C8-BTBT OTFTs is susceptible to degradation when exposed to various environmental factors. The primary mechanisms of degradation involve the interaction of the semiconductor film with ambient species such as oxygen and water, as well as exposure to light.

Influence of Ambient Air and Humidity

Exposure to ambient air, which contains both oxygen and moisture, can have a complex effect on the performance of C8-BTBT devices. Initially, a short exposure to air can sometimes lead to an improvement in device performance, potentially due to the passivation of trap states by moisture. However, prolonged exposure typically results in a degradation of key transistor parameters.

One study systematically investigated the effects of different ambient gases on solution-processed C8-BTBT OTFTs.[1] Devices exposed to air for two hours exhibited significantly better electrical properties compared to those kept in high vacuum, oxygen, or nitrogen. The average carrier mobility of air-exposed devices was 4.82 cm²/V·s, compared to 2.76 cm²/V·s for devices in a high vacuum.[1] This initial improvement is thought to be related to the interaction of moisture with the C8-BTBT film.

However, long-term exposure to air leads to performance degradation. The same study monitored the carrier mobility of a C8-BTBT device exposed to air for approximately one week (9120 minutes). The mobility initially increased from 1.97 cm²/V·s to a peak of 3.08 cm²/V·s after 2 to 4 hours of exposure, after which it began to decrease.[1] This degradation is attributed to the continuous absorption and interaction of moisture, leading to increased transistor instability.[1]