# troubleshooting poor performance in Ptcdi-C8 based OFETs

Author: BenchChem Technical Support Team. Date: December 2025

# Technical Support Center: Ptcdi-C8 Based OFETs

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with N,N'-dioctyl-3,4,9,10-perylenedicarboximide (**Ptcdi-C8**) based Organic Field-Effect Transistors (OFETs).

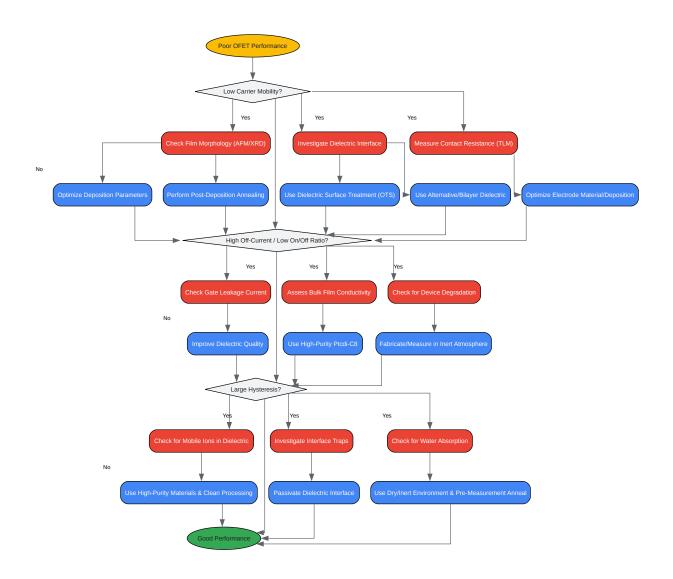

# **Troubleshooting Guides**

This section addresses common problems encountered during the fabrication and characterization of **Ptcdi-C8** OFETs, offering potential causes and solutions.

## **Issue 1: Low Carrier Mobility**

Q: My **Ptcdi-C8** OFET exhibits significantly lower electron mobility than expected. What are the potential causes and how can I improve it?

A: Low carrier mobility in **Ptcdi-C8** OFETs is a frequent issue that can stem from several factors related to the quality of the organic semiconductor film, the dielectric interface, and the device architecture.

Possible Causes and Solutions:

- Poor Film Crystallinity and Morphology: The degree of molecular ordering and the size of crystalline grains in the Ptcdi-C8 film are critical for efficient charge transport.[1][2]

- Solution: Optimize the deposition parameters. For thermal evaporation, adjust the substrate temperature and deposition rate. A slow deposition rate (e.g., 0.05 nm/s) can promote better molecular ordering.[3][4] For solution-based methods, experiment with different solvents and concentrations.

- Solution: Implement post-deposition annealing. Both thermal annealing and solvent vapor annealing can significantly improve film crystallinity.[5][6] However, excessive annealing temperatures or times can also degrade performance.[7]

- Interface Traps: Traps at the semiconductor/dielectric interface can hinder charge carrier movement. The presence of hydroxyl (-OH) groups on the dielectric surface is a common source of electron traps.[8]

- Solution: Utilize a hydrophobic dielectric surface. Treatment of the SiO2 surface with materials like octadecyltrichlorosilane (OTS) can reduce trap states.

- Solution: Employ a bilayer dielectric, such as Al2O3/SiO2, which has been shown to reduce interfacial trap states and improve mobility.[3]

- High Contact Resistance: A large resistance at the source/drain electrode and organic semiconductor interface can impede charge injection and lead to an underestimation of the intrinsic mobility.

- Solution: Select appropriate electrode materials. While gold (Au) is commonly used, its work function may not be perfectly aligned with the LUMO of **Ptcdi-C8**.

- Solution: Optimize the electrode deposition process to ensure a clean interface.

## Issue 2: High "Off" Current and Low On/Off Ratio

Q: My device shows a high drain current even when the gate voltage is supposed to turn it "off," resulting in a poor on/off ratio. What could be the problem?

A: A high off-state current can be detrimental to the performance of a transistor, particularly for switching applications. This issue is often related to charge carriers not being effectively depleted from the channel or alternative current leakage paths.

#### Possible Causes and Solutions:

- Gate Leakage Current: A significant current flowing from the gate electrode through the dielectric to the channel can contribute to the off-current.

- Solution: Improve the quality of the gate dielectric. Ensure the dielectric layer is pinholefree and has a high breakdown field. For thermally grown SiO2, ensure a high-quality growth process. For polymer dielectrics, optimize the spin-coating and curing conditions.

- Bulk Conductivity of the Organic Film: If the **Ptcdi-C8** film has a high intrinsic conductivity or is unintentionally doped, it can lead to a current that is not modulated by the gate field.

- Solution: Ensure the purity of the **Ptcdi-C8** source material. Use high-purity materials to minimize the presence of dopants.

- Device Degradation: Exposure to ambient conditions, particularly oxygen and moisture, can lead to the degradation of the **Ptcdi-C8** film and an increase in off-current.[9]

- Solution: Fabricate and characterize the devices in an inert atmosphere (e.g., a glovebox).

If working in air, minimize exposure time.

## **Issue 3: Large Hysteresis in Transfer Characteristics**

Q: I observe a significant difference in the transfer curve when sweeping the gate voltage from positive to negative and back. What causes this hysteresis?

A: Hysteresis in the transfer characteristics is a common sign of charge trapping within the device.

## Possible Causes and Solutions:

Mobile Ions in the Dielectric: The presence of mobile ions (e.g., Na+) in the gate dielectric

can drift under the applied gate field, leading to a shift in the threshold voltage and

hysteresis.

- Solution: Use high-purity dielectric materials and ensure clean processing conditions.

- Charge Trapping at the Interface: As with low mobility, traps at the semiconductor/dielectric interface can capture and slowly release charge carriers, causing hysteresis. The presence of hydroxyl groups on the dielectric surface is a known contributor.[8]

- Solution: Employ surface treatments (e.g., OTS) or alternative dielectrics to passivate the interface.

- Water Molecules: Water molecules absorbed into the dielectric or at the interface can act as charge traps.

- Solution: Perform fabrication and measurements in a dry, inert environment. Annealing the device before measurement can also help to drive out absorbed water.

# Frequently Asked Questions (FAQs)

Q1: What are typical performance metrics for Ptcdi-C8 based OFETs?

A1: The performance of **Ptcdi-C8** OFETs can vary significantly depending on the device architecture, fabrication conditions, and choice of materials. The following table summarizes some reported performance metrics.

| Dielectric                   | Mobility<br>(cm²/Vs) | On/Off Ratio | Threshold<br>Voltage (V) | Reference |

|------------------------------|----------------------|--------------|--------------------------|-----------|

| SiO2                         | ~0.03 - 0.43         | > 10^5       | 5.6 to -20               | [3][8]    |

| Al2O3/SiO2                   | ~0.26                | > 10^6       | ~1.46                    | [3]       |

| PMMA/PAA/PM<br>MA            | ~0.23 - 0.69         | > 10^5       | -                        | [8]       |

| Solution-<br>processed wires | up to 2.2            | > 10^5       | -                        | [10]      |

Q2: How do I calculate the charge carrier mobility?

A2: The field-effect mobility ( $\mu$ ) is typically calculated from the transfer characteristics in the saturation regime using the following equation:

IDS =

$$(W / 2L) * Ci * \mu * (VGS - Vth)^2$$

#### Where:

- IDS is the drain-source current

- W is the channel width

- L is the channel length

- Ci is the capacitance per unit area of the gate dielectric

- VGS is the gate-source voltage

- · Vth is the threshold voltage

By plotting the square root of IDS versus VGS, the mobility can be extracted from the slope of the linear portion of the curve. It's important to note that this is an idealized equation and the calculated mobility can be affected by factors like contact resistance.[11][12]

Q3: How can I measure and minimize contact resistance?

A3: High contact resistance (Rc) can significantly limit device performance. The Transmission Line Method (TLM) is a common technique to extract Rc. This involves fabricating transistors with identical widths but varying channel lengths. By plotting the total device resistance against the channel length for different gate voltages, the contact resistance can be extrapolated as the y-intercept.[13][14] Other single-transistor methods like the Direct Contact Resistance Extrapolation (DICRE) method have also been proposed.[1]

#### To minimize contact resistance:

- Use electrode materials with work functions that align well with the LUMO of Ptcdi-C8.

- Employ a thin interlayer of a material that facilitates charge injection.

• Optimize the deposition of the organic semiconductor to ensure good morphological contact with the electrodes.

Q4: What is the effect of thermal annealing on Ptcdi-C8 OFETs?

A4: Thermal annealing is a crucial step to improve the crystallinity of the **Ptcdi-C8** film and, consequently, the device performance. Annealing at temperatures around 100-150°C can promote the formation of larger, more ordered crystalline domains, leading to higher mobility. [15][16] However, annealing at excessively high temperatures can lead to film dewetting and degradation of the device.[7] The optimal annealing temperature and duration should be determined experimentally for a specific device structure and substrate.

Q5: How does solvent vapor annealing work and what are its advantages?

A5: Solvent vapor annealing involves exposing the **Ptcdi-C8** film to a solvent vapor atmosphere. The solvent molecules plasticize the organic film, allowing the **Ptcdi-C8** molecules to reorganize into a more crystalline structure.[6] This technique can be particularly effective for solution-processed films. One of the main advantages is that it can be performed at or near room temperature, avoiding potential damage from high-temperature thermal annealing. The choice of solvent is critical; a solvent that is a good solvent for **Ptcdi-C8** is typically used. The annealing time is also a key parameter to optimize.[5]

# **Experimental Protocols**

# Protocol 1: Fabrication of Bottom-Gate, Top-Contact Ptcdi-C8 OFETs by Thermal Evaporation

- Substrate Cleaning:

- Start with a heavily doped Si wafer with a thermally grown SiO2 layer (e.g., 300 nm).

- Sonication in a sequence of deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrate with a stream of nitrogen gas.

- (Optional but recommended) Treat the substrate with an oxygen plasma or a piranha solution to remove organic residues and create a hydrophilic surface.

- (Optional) For a hydrophobic surface, treat the SiO2 with a self-assembled monolayer

(SAM) such as octadecyltrichlorosilane (OTS).

### Ptcdi-C8 Deposition:

- Place the cleaned substrate in a high-vacuum thermal evaporator (base pressure < 10-6 Torr).

- Deposit a 30-50 nm thick film of Ptcdi-C8.

- Maintain a low deposition rate (e.g., 0.05 0.1 nm/s) to promote ordered film growth.[3]

The substrate can be held at room temperature or slightly elevated temperatures.

## Electrode Deposition:

- Without breaking vacuum, deposit the source and drain electrodes through a shadow mask.

- A common electrode material is gold (Au) with a thickness of 40-50 nm. An adhesion layer of chromium (Cr) or titanium (Ti) (2-5 nm) can be deposited first.

### Annealing:

Post-deposition annealing can be performed in a vacuum or inert atmosphere. A typical annealing temperature is 120-150°C for 30-60 minutes.

## **Protocol 2: Electrical Characterization**

- Setup:

- Place the fabricated OFET on the chuck of a probe station.

- Use micromanipulators to make contact with the source, drain, and gate electrodes.

- Perform measurements in an inert atmosphere (e.g., nitrogen or argon) to minimize degradation.

- Output Characteristics (IDS vs. VDS):

- Apply a constant gate voltage (VGS).

- Sweep the drain-source voltage (VDS) from 0 V to a desired positive voltage (e.g., 60 V) and measure the drain-source current (IDS).

- Repeat the VDS sweep for several different VGS values.

- Transfer Characteristics (IDS vs. VGS):

- Apply a constant, low VDS (linear regime, e.g., 1-5 V) and a high VDS (saturation regime, e.g., 60 V).

- Sweep the VGS from a negative voltage (e.g., -20 V) to a positive voltage (e.g., 80 V) and measure IDS.

## **Visualizations**

Click to download full resolution via product page

## **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. pubs.aip.org [pubs.aip.org]

- 2. pubs.aip.org [pubs.aip.org]

- 3. 유연인쇄전자학술지(Journal of Flexible and Printed Electronics) [e-jfpe.org]

- 4. ims.tsukuba.ac.jp [ims.tsukuba.ac.jp]

- 5. Synergistic Effect of Solvent Vapor Annealing and Chemical Doping for Achieving High-Performance Organic Field-Effect Transistors with Ideal Electrical Characteristics - PMC [pmc.ncbi.nlm.nih.gov]

- 6. Electron-to Hole Transport Change Induced by Solvent Vapor Annealing of Naphthalene Diimide Doped with Poly(3-Hexylthiophene) PMC [pmc.ncbi.nlm.nih.gov]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- 9. Role of time-dependent foreign molecules bonding in the degradation mechanism of polymer field-effect transistors in ambient conditions - PMC [pmc.ncbi.nlm.nih.gov]

- 10. researchgate.net [researchgate.net]

- 11. pubs.aip.org [pubs.aip.org]

- 12. On the methodology of the determination of charge concentration dependent mobility from organic field-effect transistor characteristics Physical Chemistry Chemical Physics (RSC Publishing) [pubs.rsc.org]

- 13. Study and Analysis of Simple and Precise of Contact Resistance Single-Transistor Extracting Method for Accurate Analytical Modeling of OTFTs Current-Voltage Characteristics: Application to Different Organic Semiconductors [mdpi.com]

- 14. researchgate.net [researchgate.net]

- 15. mdpi.com [mdpi.com]

- 16. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [troubleshooting poor performance in Ptcdi-C8 based OFETs]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1588815#troubleshooting-poor-performance-in-ptcdi-c8-based-ofets]

## **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com