Check Availability & Pricing

# troubleshooting poor device performance of "tribromo-8,16-Pyranthrenedione" transistors

Author: BenchChem Technical Support Team. Date: December 2025

Compound of Interest

Compound Name: 8,16-Pyranthrenedione, tribromo

Cat. No.: B072587

Get Quote

## Technical Support Center: Tribromo-8,16-Pyranthrenedione and Pyrene-Based Transistors

Disclaimer: Direct experimental data on the transistor performance of "tribromo-8,16-Pyranthrenedione" is not currently available in published literature. The following troubleshooting guide is based on common issues and best practices for organic thin-film transistors (OTFTs), with a focus on pyrene-based and similar polycyclic aromatic hydrocarbon semiconductors.

## **Frequently Asked Questions (FAQs)**

Q1: What are the expected performance characteristics of transistors based on novel pyrenebased semiconductors?

A1: The performance of OTFTs is highly dependent on the specific molecular structure, device architecture, and fabrication conditions. For well-designed, high-performance pyrene-based materials, one might expect to see carrier mobilities in the range of 0.1 to over 2.0 cm²/Vs, ON/OFF current ratios of 10^5 to 10^8, and threshold voltages within a few volts of zero. However, for a new, uncharacterized material like tribromo-8,16-Pyranthrenedione, initial performance may be lower, and optimization is key.

Q2: What are the most common reasons for poor device performance in pyrene-based OTFTs?

#### A2: Common issues include:

- Low Carrier Mobility: Often due to poor molecular ordering in the thin film, impurities, or trapping states at the semiconductor-dielectric interface.

- High OFF-Current: Can be caused by a high charge carrier concentration in the "off" state, leakage currents through the gate dielectric, or impurities in the semiconductor layer.

- Device Instability: Performance degradation over time, often accelerated by exposure to air (oxygen and moisture), light, and prolonged electrical stress.[1][2][3]

- Poor Contact Resistance: A large resistance at the interface between the source/drain electrodes and the organic semiconductor layer can limit the overall device performance.[4]

Q3: How critical is the substrate and dielectric surface treatment for pyrene-based transistor performance?

A3: Extremely critical. The interface between the gate dielectric and the organic semiconductor is where charge transport occurs. A smooth, clean, and chemically compatible surface is essential for achieving high mobility and low trapping. Surface treatments with self-assembled monolayers (SAMs) like octadecyltrichlorosilane (OTS) or hexamethyldisilazane (HMDS) are often used to reduce surface energy and promote better molecular ordering of the deposited organic semiconductor.

Q4: What are the typical fabrication methods for transistors with new pyrene-based materials?

A4: Solution-based techniques are common for initial testing of new organic semiconductors due to their versatility and low material consumption. These include spin-coating, drop-casting, and inkjet printing.[1] For materials with sufficient thermal stability, vacuum deposition can also be used to create highly ordered thin films.[1]

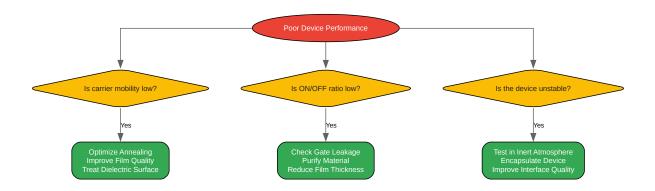

# Troubleshooting Guides Issue 1: Low Carrier Mobility

Q: My device is functional, but the calculated carrier mobility is significantly lower than expected. What are the potential causes and how can I improve it?

A: Low carrier mobility is a frequent challenge. Here's a step-by-step troubleshooting approach:

- Optimize the Annealing Process:

- Have you annealed the semiconductor film after deposition? Thermal annealing can improve the crystallinity and molecular ordering of the organic film, leading to better charge transport.

- Action: Experiment with different annealing temperatures and times. Start with a

temperature below the material's decomposition point and anneal for 30-60 minutes.

Characterize the film morphology with Atomic Force Microscopy (AFM) to correlate with

mobility changes.

- Improve the Semiconductor Film Quality:

- Is the film uniform? Non-uniform films with cracks or large, disconnected crystalline grains will have poor charge transport.

- Action: Adjust the solution concentration and spin-coating/drop-casting parameters.

Slower solvent evaporation can sometimes lead to larger, more ordered crystalline domains.

- Check the Dielectric Surface:

- Was the dielectric surface properly treated? A high-energy surface can lead to disordered film growth.

- Action: Ensure the substrate is scrupulously clean. Implement a surface treatment with an appropriate SAM (e.g., OTS for SiO<sub>2</sub>) to create a more favorable surface for molecular packing.

## Issue 2: High OFF-Current and Low ON/OFF Ratio

Q: My transistor shows a very high current in the "off" state, resulting in a poor ON/OFF ratio. What could be the problem?

A: A high OFF-current can stem from several sources:

### · Gate Leakage:

- Is the gate dielectric intact? Pinholes or defects in the dielectric layer can cause a significant leakage current from the gate to the channel.

- Action: Measure the gate current (Ig) during device operation. If it is comparable to the drain current (Id) in the off state, your dielectric is likely compromised. Use a thicker or higher-quality dielectric layer.

#### Impurity Doping:

- Is the semiconductor material pure? Impurities can act as dopants, increasing the intrinsic carrier concentration and leading to a high off-current.

- Action: Purify the tribromo-8,16-Pyranthrenedione material, for instance, by temperature gradient sublimation.

#### Bulk Conduction:

- Is the semiconductor film too thick? In thick films, conduction can occur through the bulk of the material, which is not effectively modulated by the gate field.

- Action: Reduce the thickness of the semiconductor layer. Films are typically in the range of 30-100 nm.

## **Issue 3: Device Instability and Hysteresis**

Q: The transistor characteristics change with repeated measurements or after exposure to air. What causes this instability?

A: Instability is a common problem for organic semiconductors, often related to environmental factors and charge trapping.

## Environmental Degradation:

Are you testing in an inert environment? Oxygen and moisture can act as charge traps or dopants in many organic semiconductors, leading to a shift in threshold voltage and a decrease in mobility.[2][3]

- Action: Perform all fabrication and characterization steps in a nitrogen-filled glovebox. If testing in air is unavoidable, consider encapsulating the device.

- Charge Trapping at the Interface:

- Is there significant hysteresis in the transfer characteristics? A large difference between the forward and reverse voltage sweeps is indicative of slow charge trapping and detrapping at the semiconductor-dielectric interface.

- Action: Improve the quality of the dielectric interface. This can involve using a different dielectric material or optimizing the surface treatment. Annealing the device may also reduce the number of trap states.

## **Quantitative Data Summary**

The table below presents typical performance metrics for a high-mobility, p-type pyrene-based OTFT as a reference. These values were achieved under optimized conditions and can serve as a benchmark for your experiments.

| Parameter               | Value            | Conditions                                         |

|-------------------------|------------------|----------------------------------------------------|

| Carrier Mobility (μ)    | ~2.1 cm²/Vs      | Substrate at optimal temperature during deposition |

| ON/OFF Current Ratio    | > 10^6           | Top-contact, bottom-gate architecture              |

| Threshold Voltage (Vth) | -5 to 5 V        | With SAM-treated dielectric surface                |

| Substrate               | Si/SiO2 with SAM | Solution-processed semiconductor                   |

Note: This data is for a different pyrene derivative and serves as an example of high performance in this class of materials.

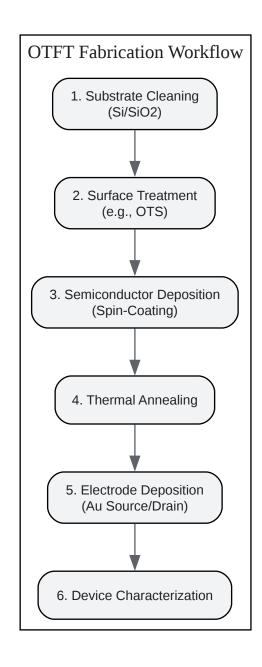

## **Experimental Protocols**

General Protocol for Solution-Processed, Top-Contact/Bottom-Gate OTFT Fabrication

### • Substrate Cleaning:

- Sequentially sonicate the heavily n-doped Si wafers with a thermally grown SiO<sub>2</sub> layer (gate dielectric) in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrates with a stream of nitrogen gas.

- Treat the substrates with an oxygen plasma or a piranha solution to create a hydrophilic surface.

- Dielectric Surface Modification (Optional but Recommended):

- For a hydrophobic surface, immerse the cleaned substrates in a 10 mM solution of octadecyltrichlorosilane (OTS) in toluene for 30 minutes.

- Rinse with fresh toluene and isopropanol, then bake at 120°C for 10 minutes to form a self-assembled monolayer.

## Semiconductor Deposition:

- Prepare a solution of tribromo-8,16-Pyranthrenedione in a suitable organic solvent (e.g., chloroform, chlorobenzene) at a concentration of 1-10 mg/mL.

- Spin-coat the solution onto the substrate at 1000-4000 RPM for 60 seconds.

- Anneal the film at a temperature optimized for improving crystallinity (e.g., 100-150°C) for 30-60 minutes in an inert atmosphere.

#### Electrode Deposition:

Using a shadow mask, thermally evaporate 50-100 nm of Gold (Au) for the source and drain electrodes. The channel length and width are defined by the mask.

#### Characterization:

Measure the output and transfer characteristics of the transistor using a semiconductor parameter analyzer in an inert environment (glovebox or vacuum probe station).

Calculate the carrier mobility in the saturation regime, the ON/OFF ratio, and the threshold voltage from the transfer curve.

## **Visualizations**

Click to download full resolution via product page

### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. PubChemLite 8,16-pyranthrenedione, tribromo- (C30H11Br3O2) [pubchemlite.lcsb.uni.lu]

- 2. 3,4,5,12-Tetrabromo-8,16-pyranthrenedione [chemicalbook.com]

- 3. Substance Registry Services | US EPA [cdxapps.epa.gov]

- 4. high-mobility-pyrene-based-semiconductor-for-organic-thin-film-transistors Ask this paper | Bohrium [bohrium.com]

- To cite this document: BenchChem. [troubleshooting poor device performance of "tribromo-8,16-Pyranthrenedione" transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b072587#troubleshooting-poor-device-performance-of-tribromo-8-16-pyranthrenedione-transistors]

## **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com