## troubleshooting low current in Tpt-ttf transistors

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |         |           |

|----------------------|---------|-----------|

| Compound Name:       | Tpt-ttf |           |

| Cat. No.:            | B034665 | Get Quote |

## **Technical Support Center: TPT-TTF Transistors**

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with **TPT-TTF** (tetraphenoxy-tetrathiafulvalene) transistors. The information is presented in a question-and-answer format to directly address common issues encountered during experimentation.

# Troubleshooting Low Current in TPT-TTF Transistors

Low current is a frequent challenge in the fabrication and characterization of **TPT-TTF** transistors. This guide provides a systematic approach to identifying and resolving the root causes of diminished current output.

Frequently Asked Questions (FAQs)

Q1: What are the expected electrical performance characteristics for TPT-TTF transistors?

A1: The performance of **TPT-TTF** transistors can vary based on fabrication parameters. However, typical values found in literature provide a benchmark for well-performing devices.

| Parameter               | Typical Value | Unit   |

|-------------------------|---------------|--------|

| Hole Mobility (μ)       | 0.1 - 1.0     | cm²/Vs |

| On/Off Current Ratio    | > 10^5        | -      |

| Threshold Voltage (Vth) | -10 to 0      | V      |

Q2: My fabricated **TPT-TTF** transistor shows significantly lower ON current than expected. What are the potential causes?

A2: Low ON current can stem from several factors throughout the fabrication and measurement process. The primary areas to investigate are the quality of the semiconductor film, the integrity of the dielectric layer, and the electrical contacts.

Q3: How can I improve the morphology of my solution-processed **TPT-TTF** film to increase current?

A3: The morphology of the organic semiconductor film is critical for efficient charge transport.[1] [2] For solution-processed **TPT-TTF** films, consider the following optimization steps:

- Solvent System: The choice of solvent and the use of solvent additives can significantly influence film crystallinity and molecular packing.

- Deposition Technique: Techniques like solution shearing can promote the formation of highly ordered crystalline films, leading to improved mobility and higher current.

- Annealing Temperature: Post-deposition annealing can enhance the crystallinity of the TPT-TTF film. However, the temperature must be carefully optimized to avoid desorption or degradation of the organic material.[3]

Q4: I suspect high contact resistance is limiting the current in my device. How can I diagnose and mitigate this issue?

A4: High contact resistance at the source and drain electrodes is a common cause of reduced current in organic transistors.

• Diagnosis: The Transmission Line Method (TLM) is a standard technique to quantify contact resistance. This involves fabricating transistors with varying channel lengths and measuring their resistance.

#### · Mitigation:

- Electrode Material: Ensure the work function of the electrode material is well-matched with the HOMO level of the TPT-TTF for efficient hole injection. Gold (Au) is a commonly used electrode material.

- Surface Treatment: Treating the electrode surface with a self-assembled monolayer (SAM), such as pentafluorobenzenethiol (PFBT), can reduce the injection barrier and improve contact.

- Deposition Conditions: The rate of metal deposition for the electrodes can impact the interface quality.

Q5: Could the gate dielectric be the source of the low current problem?

A5: Yes, the gate dielectric plays a crucial role in transistor performance.

- Dielectric Quality: A poor-quality dielectric with pinholes or a high density of trap states can lead to significant gate leakage current and a low ON/OFF ratio.

- Surface Chemistry: The interface between the dielectric and the TPT-TTF layer is critical.

Surface treatments on the dielectric, for instance with silanizing agents like octadecyltrichlorosilane (OTS), can promote better ordering of the TPT-TTF molecules and reduce charge trapping.

## **Experimental Protocols**

Fabrication of a Bottom-Gate, Top-Contact **TPT-TTF** Transistor (Solution-Shearing)

- Substrate Cleaning:

- Begin with a heavily n-doped silicon wafer with a thermally grown silicon dioxide (SiO<sub>2</sub>)

layer (typically 300 nm) acting as the gate dielectric.

- Clean the substrate sequentially in an ultrasonic bath with acetone, and isopropanol for 15 minutes each.

- o Dry the substrate with a stream of nitrogen gas.

- Treat the substrate with an oxygen plasma or a Piranha solution to create a hydrophilic surface.

- Dielectric Surface Treatment (Optional but Recommended):

- To improve the performance, treat the SiO<sub>2</sub> surface with a self-assembled monolayer (SAM) like octadecyltrichlorosilane (OTS). This is typically done by immersing the substrate in a dilute solution of OTS in an anhydrous solvent like toluene or hexane for a specified time, followed by rinsing and annealing.

- TPT-TTF Film Deposition (Solution-Shearing):

- Prepare a solution of TPT-TTF in a suitable organic solvent (e.g., chloroform, chlorobenzene) at a specific concentration.

- Place the substrate on a heated stage set to a desired temperature.

- Position a shearing blade (e.g., a glass slide) at a small angle and a set gap above the substrate.

- Dispense a small volume of the TPT-TTF solution in the gap between the blade and the substrate.

- Move the blade at a constant, slow speed across the substrate to deposit a uniform thin film.

- Anneal the film on a hotplate at a carefully controlled temperature to promote solvent evaporation and improve crystallinity.

- Source and Drain Electrode Deposition:

- Use a shadow mask to define the source and drain electrodes.

Deposit a thin adhesion layer of chromium or titanium (e.g., 5 nm) followed by a layer of gold (e.g., 50 nm) via thermal evaporation or e-beam evaporation.

#### **Electrical Characterization**

- Setup: Place the fabricated transistor on a probe station in a dark, electrically shielded environment.

- Connections: Connect the source, drain, and gate terminals to a semiconductor parameter analyzer.

- Output Characteristics:

- Apply a constant gate voltage (V\_G), starting from 0 V and stepping to more negative values (e.g., -20 V, -40 V, -60 V).

- For each V\_G, sweep the drain voltage (V\_D) from 0 V to a negative value (e.g., -60 V)

and measure the drain current (I\_D).

- Plot I D vs. V D for each V G.

- Transfer Characteristics:

- Apply a constant, high drain voltage (e.g., V\_D = -60 V) to operate the transistor in the saturation regime.

- Sweep the gate voltage (V\_G) from a positive value (e.g., +20 V) to a negative value (e.g., -60 V) and measure the drain current (I D).

- Plot I\_D and the square root of I\_D vs. V\_G. The mobility can be extracted from the slope

of the (I\_D)^1/2 vs. V\_G plot in the saturation region. The on/off ratio is the ratio of the

maximum to the minimum drain current.

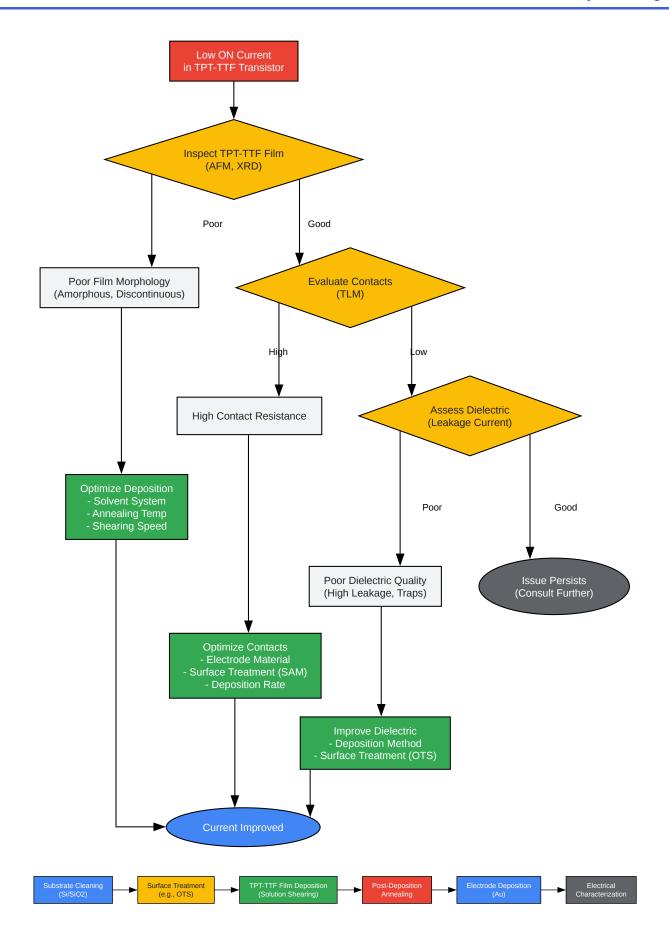

### **Visualizing Troubleshooting and Workflows**

Troubleshooting Flowchart for Low Current

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. researchgate.net [researchgate.net]

- 2. accessengineeringlibrary.com [accessengineeringlibrary.com]

- 3. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [troubleshooting low current in Tpt-ttf transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b034665#troubleshooting-low-current-in-tpt-ttf-transistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com