# troubleshooting low charge mobility in f8 transistors

Author: BenchChem Technical Support Team. Date: December 2025

Compound of Interest

POLY(9 9-DI-N-

Compound Name: OCTYLFLUORENYL-2 7-DIYL)

Cat. No.: B1173580

Get Quote

# **Technical Support Center: F8 Transistors**

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to help researchers, scientists, and drug development professionals address challenges encountered during experiments with F8 (poly(9,9-di-n-octylfluorene-alt-bithiophene)) transistors, with a specific focus on resolving issues related to low charge mobility.

# **Troubleshooting Guide**

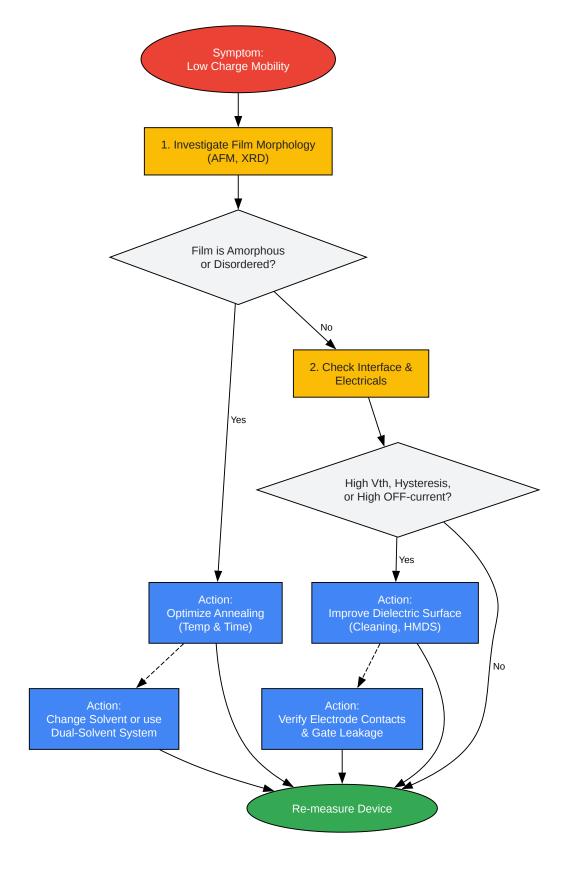

Q1: My F8 transistor exhibits very low charge carrier mobility. What are the primary factors I should investigate?

Low charge mobility in F8 transistors is typically rooted in issues related to the quality of the semiconductor film, the device architecture, or the processing conditions. The most critical factors to investigate are:

- Thin-Film Morphology: The arrangement and ordering of the polymer chains are paramount for efficient charge transport. Disordered, amorphous films or the presence of significant grain boundaries can severely limit mobility.[1][2]

- Processing Conditions: Parameters such as the choice of solvent, solution concentration,

spin-coating speed, and particularly the annealing temperature and duration have a profound

## Troubleshooting & Optimization

impact on the final film structure and, consequently, its electrical performance.[2][3]

- Interface Quality: The interface between the F8 semiconductor and the dielectric layer is crucial. Traps or defects at this interface can hinder charge transport and lead to non-ideal transistor behavior, such as high threshold voltages or voltage shifts.[4][5]

- Material Purity and Degradation: Impurities in the F8 polymer or degradation due to exposure to air, moisture, or light can introduce charge traps and reduce performance.

- Contact Resistance: Poor contact between the source/drain electrodes and the organic semiconductor can impede charge injection, leading to an underestimation of the intrinsic mobility.[5]

Q2: How can I improve the thin-film morphology of the F8 active layer?

Optimizing the morphology from a disordered state to a more ordered, crystalline or liquidcrystalline phase is key to enhancing charge mobility.

- Thermal Annealing: Heating the F8 film after deposition is a critical step. Annealing at

temperatures near the polymer's glass transition or liquid crystal phase transition

temperature provides the thermal energy needed for the polymer chains to self-organize into

more ordered domains.[2] This process can convert an amorphous film into a highly ordered,

liquid-crystal phase, which significantly enhances hole mobility.[2]

- Solvent Selection: The choice of solvent affects how the polymer chains aggregate and

deposit during spin-coating.[6][7] Using a solvent system that promotes polymer aggregation

and crystallization upon drying can lead to better-ordered films. Sometimes, a dual-solvent

system, where one solvent has a higher boiling point, can slow the drying process, allowing

more time for molecular self-assembly.[8]

- Surface Treatment: Modifying the dielectric surface with a self-assembled monolayer (SAM), such as HMDS, can improve the wetting of the F8 solution and promote better film formation.

[9] Additionally, using alignment layers, like rubbed polyimide, can induce a preferred orientation of the polymer chains, leading to anisotropic and enhanced mobility.

Q3: What is the recommended annealing procedure for F8 thin films?

## Troubleshooting & Optimization

Thermal annealing is crucial for achieving high mobility in F8 transistors. The goal is to heat the film to a temperature that allows for structural reordering without causing decomposition.

- Temperature: For F8T2 (a common F8 derivative), annealing at temperatures between 150°C and 300°C has been shown to induce structural ordering from an amorphous to a more ordered phase.[2] The optimal temperature will depend on the specific molecular weight and formulation of the F8 polymer.

- Atmosphere: Annealing should be performed in an inert atmosphere (e.g., nitrogen or argon)

to prevent oxidative degradation of the polymer, which can create charge traps.[10]

- Duration: Annealing times can vary, but typically range from 10 to 60 minutes.

It is recommended to perform a systematic study by varying the annealing temperature and measuring the resulting transistor performance to find the optimal conditions for your specific material and device structure.

Q4: The electrical characteristics of my device are not ideal (e.g., high OFF current, hysteresis, large threshold voltage). What are the potential causes?

These issues often point to problems at the semiconductor-dielectric interface or with charge injection.

- Interface Traps: A high density of trap states at the interface can lead to a large subthreshold swing, a high threshold voltage (Vth), and hysteresis in the transfer characteristics.[4][5]

Ensure the dielectric surface is clean and consider surface treatments (e.g., HMDS) to passivate traps.

- Contact Issues: High contact resistance can result in non-linear output characteristics at low drain voltages and an underestimation of mobility. Ensure clean electrode surfaces and consider using electrode materials with work functions well-matched to the HOMO level of F8 for efficient hole injection.[4]

- Gate Leakage: A high OFF current can sometimes be attributed to a significant gate leakage current. This indicates a problem with the gate dielectric layer, which may be too thin or have pinholes or defects.[11]

Ambient Exposure: For n-channel transistors, in particular, exposure to air can be a significant issue, but even for p-type materials like F8, ambient moisture and oxygen can act as charge traps and degrade performance.[4][12]

# **Frequently Asked Questions (FAQs)**

Q1: What is a typical hole mobility value for F8-based transistors? Reported hole mobilities for F8 and its derivatives like F8T2 can vary widely based on processing conditions. While unoptimized, amorphous films may show mobilities in the range of  $10^{-5}$  to  $10^{-4}$  cm<sup>2</sup>/Vs, optimized films with high structural order can achieve mobilities greater than  $10^{-3}$  cm<sup>2</sup>/Vs, with some reports showing values approaching 0.1 cm<sup>2</sup>/Vs, especially when alignment layers are used.[2]

Q2: How do I select an appropriate solvent for dissolving F8? F8 polymers are typically soluble in common aromatic solvents. The choice can influence the final film quality.[7]

- Good Solvents: Toluene, xylene, and chloroform are frequently used.

- Considerations: The solvent's boiling point affects the drying rate. Higher boiling point solvents (like xylene) evaporate more slowly, which can allow more time for the polymer chains to self-organize, potentially leading to better-ordered films.[13] Using a mixed-solvent system can also be a strategy to control film morphology.[6]

Q3: Can I fabricate and test F8 transistors in an ambient environment? While initial processing steps like substrate cleaning can be done in ambient conditions, it is highly recommended to perform the deposition of the active layer, annealing, and electrical characterization in a controlled, inert environment (e.g., a nitrogen-filled glovebox).[12] Exposure to oxygen and moisture in the air can create charge traps at the semiconductor-dielectric interface and within the bulk film, leading to degraded performance and instability.[4]

### **Data Presentation**

Table 1: Effect of Thermal Annealing on F8T2 Transistor Mobility

This table summarizes the typical impact of post-deposition annealing on the hole mobility of F8T2 transistors, demonstrating the importance of thermal treatment for structural ordering.

| Annealing<br>Temperature    | Film Phase                | Typical Hole<br>Mobility<br>(cm²/Vs) | Anisotropy<br>(µ_parallel /<br>µ_perpendicul<br>ar) | Reference |

|-----------------------------|---------------------------|--------------------------------------|-----------------------------------------------------|-----------|

| As-deposited (No<br>Anneal) | Amorphous                 | ~ 1 x 10 <sup>-4</sup>               | ~ 1 (Isotropic)                                     | [2]       |

| 150 °C                      | Partially Ordered         | ~ 5 x 10 <sup>-4</sup>               | >1                                                  | [2]       |

| 280 °C                      | Nematic Liquid<br>Crystal | > 2 x 10 <sup>-3</sup>               | Up to 6.5                                           | [2]       |

Data is synthesized from trends reported in the literature. Actual values may vary based on specific experimental conditions.

# **Experimental Protocols**

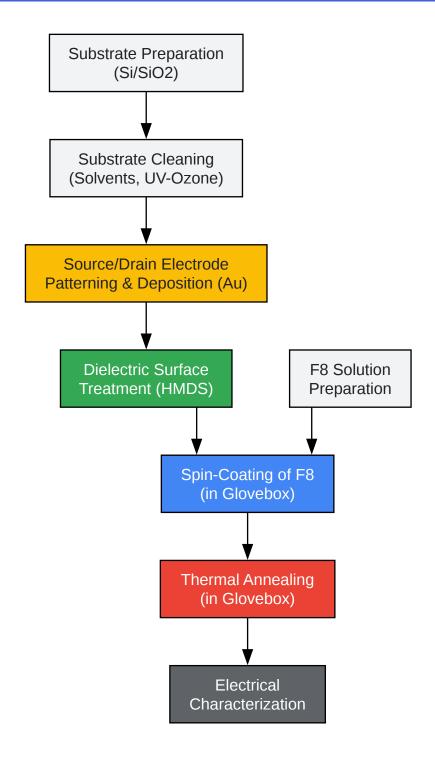

Protocol 1: Fabrication of a Bottom-Gate, Bottom-Contact (BGBC) F8 Transistor

- Substrate Cleaning:

- Sequentially sonicate the heavily doped Si wafer (acting as the gate) with a SiO<sub>2</sub> dielectric layer in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrate with a stream of nitrogen gas.

- Treat with UV-Ozone for 10 minutes to remove organic residues and create a hydrophilic surface.

- Electrode Deposition:

- Using photolithography or a shadow mask, pattern the source and drain electrodes.

- Deposit a 5 nm adhesion layer of Cr or Ti followed by a 40 nm layer of Au via thermal evaporation.

- Dielectric Surface Treatment:

To improve the interface quality, treat the SiO<sub>2</sub> surface with a self-assembled monolayer. A common method is vapor-phase deposition of hexamethyldisilazane (HMDS) at 120°C for 30 minutes.

[9] This makes the surface hydrophobic, which promotes better ordering of the F8 polymer chains.

#### F8 Active Layer Deposition:

- Prepare a solution of F8 in a suitable solvent (e.g., p-xylene) at a concentration of 5-10 mg/mL.

- Inside a nitrogen-filled glovebox, deposit the F8 solution onto the substrate via spincoating (e.g., at 2000 rpm for 60 seconds).

#### Thermal Annealing:

- Transfer the substrate to a hotplate within the glovebox.

- Anneal at the desired temperature (e.g., 280°C) for 30 minutes to induce the formation of the liquid-crystalline phase.[2]

- Allow the substrate to cool down slowly to room temperature.

#### Characterization:

• The device is now ready for electrical characterization.

## **Mandatory Visualization**

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. arxiv.org [arxiv.org]

- 2. researchgate.net [researchgate.net]

- 3. mdpi.com [mdpi.com]

- 4. d31kydh6n6r5j5.cloudfront.net [d31kydh6n6r5j5.cloudfront.net]

- 5. api.repository.cam.ac.uk [api.repository.cam.ac.uk]

- 6. researchgate.net [researchgate.net]

- 7. Influence of solvents on the morphology of Langmuir and Langmuir—Schaefer films of PCBM and PCBM-based oligomers and polymers - Physical Chemistry Chemical Physics (RSC Publishing) [pubs.rsc.org]

- 8. researchgate.net [researchgate.net]

- 9. researchgate.net [researchgate.net]

- 10. The effect of annealing ambient on the characteristics of an indium-gallium-zinc oxide thin film transistor PubMed [pubmed.ncbi.nlm.nih.gov]

- 11. Defects in Thin Films | Journal Article | PNNL [pnnl.gov]

- 12. researchgate.net [researchgate.net]

- 13. Stability of thin polymer films: influence of solvents PubMed [pubmed.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [troubleshooting low charge mobility in f8 transistors].

BenchChem, [2025]. [Online PDF]. Available at:

[https://www.benchchem.com/product/b1173580#troubleshooting-low-charge-mobility-in-f8-transistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide

accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com