# troubleshooting common defects in gallium arsenide semiconductor devices

Author: BenchChem Technical Support Team. Date: December 2025

## Gallium Arsenide Semiconductor Device Troubleshooting Center

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in resolving common issues encountered during experiments with **Gallium** Arsenide (GaAs) semiconductor devices.

### **Frequently Asked Questions (FAQs)**

1. What are the common types of defects in GaAs semiconductor devices?

**Gallium** Arsenide (GaAs) semiconductor devices can exhibit a variety of defects that can impact their performance and reliability. These defects can be broadly categorized as:

- Point Defects: These are zero-dimensional defects and include vacancies (a missing atom

from its lattice site), interstitials (an atom occupying a site that is not a regular lattice site),

and antisite defects (an atom of one type occupying a lattice site intended for another type,

e.g., a Ga atom on an As site).[1] These can be native defects or introduced by impurities.

- Extended Defects: These include one-dimensional defects like dislocations, and twodimensional defects such as stacking faults and grain boundaries.[1] Dislocations can be

introduced during crystal growth or device processing and are generally detrimental to device performance.[1]

- Surface Defects: A common surface defect in GaAs films grown by Molecular Beam Epitaxy (MBE) is the "oval defect," which is a macroscopic surface imperfection.[2][3] The presence of native oxides on the GaAs surface can also lead to a high density of surface states, which can negatively affect device performance.[2]

- 2. What are the primary causes of device failure in GaAs FETs and HEMTs?

Common failure mechanisms in **Gallium** Arsenide Field-Effect Transistors (FETs) and High Electron Mobility Transistors (HEMTs) include:

- Source-drain burnout: This is a catastrophic failure mode caused by thermal runaway, accounting for a significant percentage of GaAs FET failures.[4]

- Ohmic contact degradation: The resistance of ohmic contacts can increase over time at elevated temperatures, leading to device failure.

- Gate degradation: The gate metal can react with the underlying GaAs, a phenomenon sometimes referred to as "gate sinking," which degrades the Schottky junction.

- Surface degradation: Unpassivated GaAs surfaces are susceptible to oxidation, which can reduce breakdown voltage and increase gate leakage current.[4]

- Electromigration: The movement of metal atoms at high current densities can lead to the formation of voids or hillocks, causing device failure.

# Troubleshooting Guides Issue 1: High Leakage Current in a GaAs Device

Question: I am observing an unexpectedly high leakage current in my GaAs device. What are the potential causes and how can I troubleshoot this issue?

Answer: High leakage current in a GaAs device can originate from several factors, primarily related to material defects and processing issues. The following steps will guide you through the troubleshooting process.

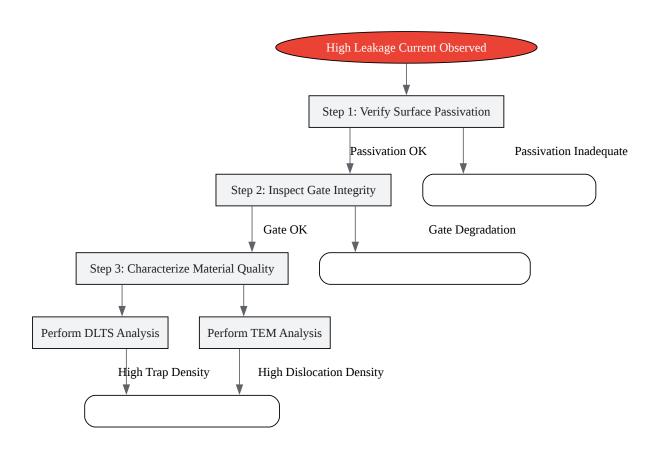

Troubleshooting Workflow:

Click to download full resolution via product page

Caption: Troubleshooting workflow for high leakage current in GaAs devices.

Step-by-Step Troubleshooting:

· Verify Surface Passivation:

Problem: An inadequate or non-existent surface passivation layer can lead to a high density of surface states, which act as leakage current pathways. The native oxide on an unpassivated GaAs surface is known to adversely affect device performance.

#### Action:

- Review your fabrication process to ensure a proper passivation step was included.

Common passivation techniques involve the use of silicon nitride (SiN) or silicon dioxide (SiO2).

- If the device is unpassivated, consider applying a suitable passivation layer.

- Characterize the surface using techniques like X-ray Photoelectron Spectroscopy (XPS)

to verify the composition and quality of the passivation layer.

- Inspect Gate Integrity:

- Problem: Degradation of the Schottky gate, such as "gate sinking" where the gate metal reacts with the GaAs, can create leakage paths.

- Action:

- Use a Scanning Electron Microscope (SEM) to visually inspect the gate for any signs of physical degradation, such as pitting or metal migration.

- Perform electrical characterization of the gate-source and gate-drain diodes to check for abnormally low breakdown voltages or high reverse leakage currents.

- Characterize Material Quality:

- Problem: Bulk material defects, such as dislocations and deep-level traps, can contribute significantly to leakage current. Threading screw dislocations, in particular, have been identified as a dominant source of high leakage currents.

- Action:

- Deep-Level Transient Spectroscopy (DLTS): This technique can identify and quantify the concentration of deep-level traps in the material. A high concentration of certain

traps can enhance leakage.

Transmission Electron Microscopy (TEM): TEM analysis can reveal the presence and density of dislocations and other extended defects within the epitaxial layers.

#### Possible Solutions:

- Improve Surface Passivation: Implement or optimize a surface passivation process. This can involve wet chemical treatments to remove the native oxide followed by the deposition of a high-quality dielectric layer.

- Optimize Gate Metallization: Re-evaluate the gate metallization scheme and deposition process to minimize reactions with the underlying GaAs.

- Optimize Crystal Growth: If bulk defects are the primary cause, a revision of the crystal growth parameters (e.g., growth temperature, V/III ratio in MBE) may be necessary to reduce the density of dislocations and deep-level traps.

### **Issue 2: Poor Ohmic Contacts on n-type GaAs**

Question: I am having trouble achieving low-resistance ohmic contacts on my n-type GaAs device. What could be the issue and how can I improve them?

Answer: Achieving low-resistance and thermally stable ohmic contacts on n-type GaAs is a common challenge. The quality of ohmic contacts is highly dependent on the surface preparation, metallization scheme, and annealing conditions.

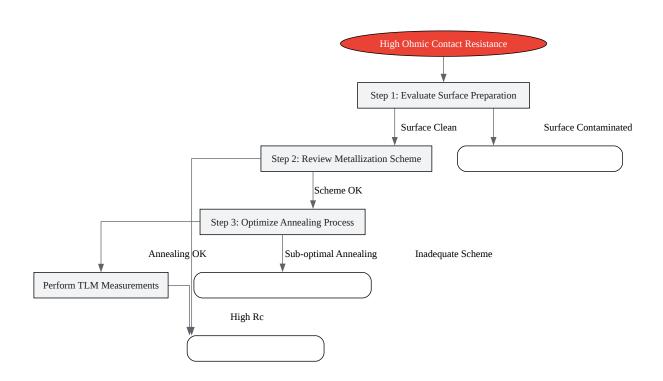

Troubleshooting Workflow:

#### Click to download full resolution via product page

Caption: Troubleshooting workflow for poor ohmic contacts on n-type GaAs.

Step-by-Step Troubleshooting:

- Evaluate Surface Preparation:

- Problem: The presence of a native oxide layer or other contaminants on the GaAs surface before metal deposition is a primary cause of poor ohmic contacts.

#### Action:

- Ensure a thorough surface cleaning procedure is performed immediately before loading the wafer into the deposition system. This typically involves degreasing with organic solvents followed by an acid dip (e.g., HCl or NH4OH solution) to remove the native oxide.[5][6][7]

- Minimize the time the cleaned wafer is exposed to air before deposition to prevent reoxidation.

#### Review Metallization Scheme:

Problem: The choice of metals and their deposition sequence is crucial. The most common metallization for n-type GaAs is a AuGe/Ni/Au system.[8] The germanium acts as an n-type dopant upon annealing, creating a heavily doped layer that facilitates tunneling.

#### Action:

- Verify that the composition and thicknesses of the metal layers are appropriate for your application.

- Consider alternative metallization schemes if the standard ones are not yielding good results.

#### • Optimize Annealing Process:

Problem: The annealing temperature and time are critical parameters that control the alloying reaction between the metal and the GaAs. Sub-optimal annealing can result in incomplete alloying or excessive diffusion of the metals.

#### Action:

- Systematically vary the annealing temperature and time to find the optimal process window. Rapid thermal annealing (RTA) is often preferred for better control.

- Characterize the contact resistance after each annealing condition using the Transmission Line Method (TLM).

#### Possible Solutions:

- Improve Surface Cleaning: Implement a robust surface cleaning protocol. A common procedure involves:

- Degreasing in acetone, methanol, and isopropanol.

- Rinsing in deionized (DI) water.

- Immersion in an HCl or NH4OH solution to remove native oxides.[5][6]

- Final rinse in DI water and drying with nitrogen.

- Modify Metallization: If the current metallization scheme is not working, consider alternatives.

For instance, adding a Ni layer between the AuGe and GaAs can improve adhesion and promote a more uniform reaction.[8]

- Adjust Annealing Parameters: Use TLM to systematically determine the optimal annealing temperature and duration for your specific metallization.

# Issue 3: Low or Degraded Photoluminescence (PL) Intensity

Question: The photoluminescence intensity from my GaAs sample is very low or degrades quickly during measurement. What could be the cause, and how can I improve it?

Answer: Low or degrading photoluminescence (PL) intensity in GaAs is often indicative of a high density of non-radiative recombination centers, which can be located at the surface or within the bulk of the material.

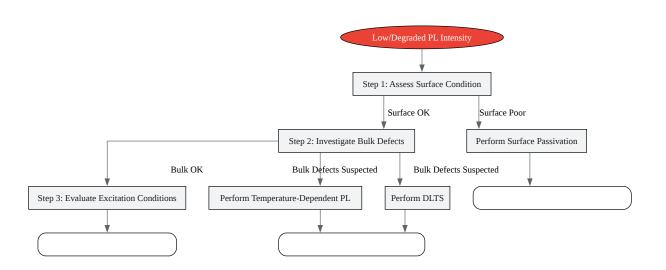

Troubleshooting Workflow:

#### Click to download full resolution via product page

Caption: Troubleshooting workflow for low or degraded PL intensity in GaAs.

#### Step-by-Step Troubleshooting:

- Assess Surface Condition:

- Problem: A high density of surface states acts as efficient non-radiative recombination centers, quenching the PL intensity. Photo-induced oxidation of the GaAs surface can also lead to a rapid degradation of the PL signal.

- Action:

- If the sample is unpassivated, consider a surface treatment to reduce surface recombination.

• If the PL intensity degrades over time during measurement, this is a strong indicator of surface-related issues.

#### Investigate Bulk Defects:

Problem: Crystalline defects within the GaAs, such as vacancies, interstitials, and dislocations, can create deep energy levels within the bandgap that act as non-radiative recombination centers.

#### Action:

- Temperature-Dependent PL: Analyze the PL spectra at various temperatures. The thermal quenching behavior of the PL intensity can provide information about the activation energy of non-radiative recombination centers.

- Deep-Level Transient Spectroscopy (DLTS): Identify and quantify deep-level defects that may be responsible for non-radiative recombination.

#### Evaluate Excitation Conditions:

Problem: High laser excitation power can sometimes lead to sample heating or an increase in surface-related degradation processes.

#### Action:

- Measure the PL intensity as a function of excitation power. If the intensity saturates or decreases at high power, it could indicate the presence of saturable trap states or heating effects.

- Use the lowest excitation power necessary to obtain a good signal-to-noise ratio.

#### Possible Solutions:

• Improve Surface Passivation: Applying a suitable surface passivation layer, such as silicon nitride or treating the surface with a sulfur-containing solution, can significantly enhance the PL intensity by reducing surface recombination.

- Optimize Material Growth: If bulk defects are the dominant issue, the crystal growth conditions (e.g., substrate temperature, V/III ratio) may need to be optimized to improve the material quality.

- Adjust Excitation Power: Use a lower excitation power density to minimize sample heating and photo-induced degradation.

## Issue 4: Presence of Oval Defects in MBE-Grown GaAs Films

Question: My MBE-grown GaAs films are showing a high density of oval defects. What is the origin of these defects and how can I eliminate them?

Answer: Oval defects are a common morphological issue in GaAs films grown by Molecular Beam Epitaxy (MBE). Their presence can degrade device performance and yield. The primary causes are related to the Ga source and substrate preparation.

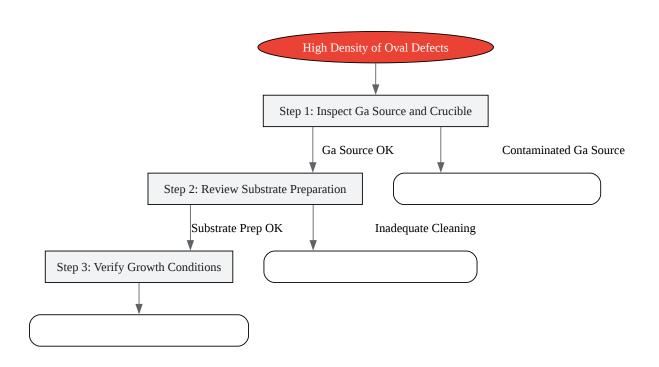

Troubleshooting Workflow:

Click to download full resolution via product page

Caption: Troubleshooting workflow for oval defects in MBE-grown GaAs.

Step-by-Step Troubleshooting:

- Inspect Ga Source and Crucible:

- Problem: The most widely accepted cause of oval defects is the presence of gallium oxide (Ga2O) in the Ga melt.[9] These oxides can be ejected from the crucible and act as nucleation sites for the defects. "Ga spitting," where droplets of Ga are ejected from the crucible, is another potential cause.

- Action:

- Thoroughly outgas the Ga source before growth to remove volatile oxides.

- Ensure the Ga crucible is not overfilled.

- Consider reloading with fresh, high-purity gallium.

- Review Substrate Preparation:

- Problem: Particulate contamination or imperfections on the substrate surface can act as nucleation sites for oval defects.

- Action:

- Ensure a meticulous substrate cleaning procedure is followed.

- Inspect the substrate surface for any visible defects or particles before loading it into the MBE system.

- Verify Growth Conditions:

- Problem: While less common, sub-optimal growth parameters can contribute to the formation of oval defects.

- Action:

- Ensure the substrate temperature and As overpressure are within the optimal range for high-quality GaAs growth.

#### Possible Solutions:

- Outgas/Replace Ga Source: The most effective way to reduce oval defects is to ensure a clean Ga source. This may involve extended outgassing at high temperatures or replacing the Ga charge entirely.

- Improve Substrate Cleaning: Implement a stringent substrate cleaning protocol to minimize particulate contamination.

- Optimize Growth Parameters: While the Ga source is the primary culprit, optimizing growth conditions can help to minimize the formation of various types of defects.

### **Quantitative Data Summary**

Table 1: Common Deep-Level Electron Traps in n-type GaAs identified by DLTS

| Trap Label | Activation Energy (eV) | Common Association                  |

|------------|------------------------|-------------------------------------|

| EL2        | E_c - 0.82             | As antisite (As_Ga) related complex |

| E3         | E_c - 0.30             | Possibly related to V_As            |

| E4         | E_c - 0.52             | -                                   |

| E5         | E_c - 0.42             | -                                   |

Note: Activation energies can vary slightly depending on the measurement conditions and material properties.

Table 2: Typical Photoluminescence Peak Energies for Defects and Impurities in GaAs at Low Temperature (e.g., 4.2 K or 77 K)

| Peak Energy (eV) | Identification                   |

|------------------|----------------------------------|

| ~1.514           | Free Exciton (FE)                |

| ~1.492           | Carbon acceptor (C_As)           |

| ~1.452           | Gallium antisite (Ga_As) related |

| ~1.36            | Copper acceptor (Cu_Ga)          |

| ~1.326           | Gallium antisite (Ga_As) related |

| ~1.289           | Arsenic vacancy (V_As) related   |

Note: Peak positions can be influenced by temperature, doping concentration, and strain.[10] [11]

### **Experimental Protocols**

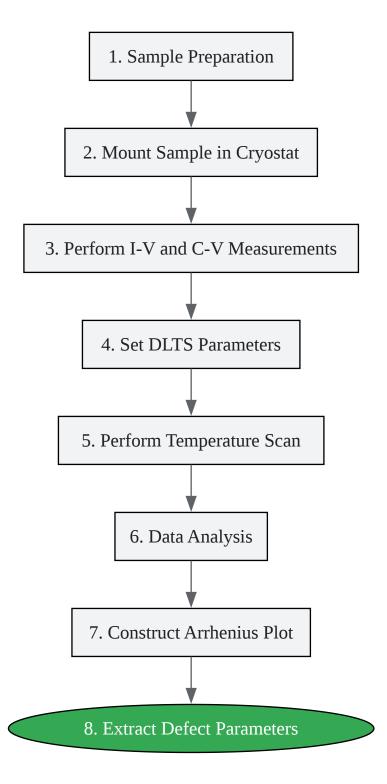

# Protocol 1: Deep-Level Transient Spectroscopy (DLTS) Measurement

Objective: To identify and characterize deep-level defects in a GaAs semiconductor device.

**Experimental Workflow:**

#### Click to download full resolution via product page

Caption: Experimental workflow for DLTS measurement.

#### Methodology:

- Sample Preparation:

- Fabricate a Schottky diode or a p-n junction on the GaAs sample. The device should have good rectifying characteristics (low reverse leakage current).

- Ensure good ohmic contact to the backside of the sample.

- Mount Sample in Cryostat:

- Mount the sample on the cold finger of a cryostat that allows for temperature variation (typically from liquid nitrogen temperature to above room temperature).

- Make electrical connections to the Schottky/p-n junction and the ohmic contact.

- Perform I-V and C-V Measurements:

- Before the DLTS measurement, perform current-voltage (I-V) and capacitance-voltage (C-V) measurements at a fixed temperature (e.g., room temperature) to verify the quality of the diode and determine the doping concentration.

- Set DLTS Parameters:

- Reverse Bias (V\_R): Apply a steady-state reverse bias to the diode to create a depletion region.

- Filling Pulse (V\_P): Apply a periodic voltage pulse to reduce the reverse bias (or apply a forward bias) to fill the deep levels with majority carriers.

- Pulse Width (t\_p): Set the duration of the filling pulse. It should be long enough to saturate the traps.

- Rate Window: Set the time window for observing the capacitance transient after the filling pulse.

- Perform Temperature Scan:

- Slowly ramp the temperature of the sample while continuously applying the voltage pulses and measuring the capacitance transient.

- The DLTS system will output a signal that is proportional to the change in capacitance within the set rate window.

- Data Analysis:

- A peak will appear in the DLTS spectrum at the temperature where the thermal emission rate of a specific deep level matches the chosen rate window.

- Repeat the temperature scan for several different rate windows.

- · Construct Arrhenius Plot:

- For each deep level (each peak in the spectrum), plot the natural logarithm of the emission rate (corrected for temperature dependence) versus the inverse of the peak temperature (1/T).

- This plot should yield a straight line.

- Extract Defect Parameters:

- The slope of the Arrhenius plot is proportional to the activation energy (E\_a) of the deep level.

- The y-intercept of the plot can be used to determine the capture cross-section ( $\sigma_n$ ) of the defect.

- The amplitude of the DLTS peak is proportional to the concentration of the deep level.

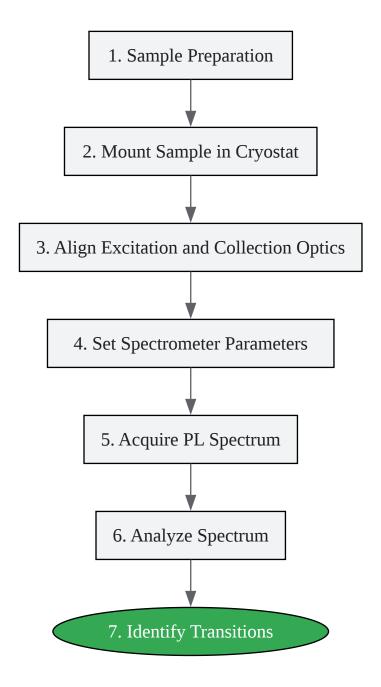

# Protocol 2: Photoluminescence (PL) Spectroscopy Measurement

Objective: To investigate the optical properties of a GaAs sample, including the identification of impurities and defects.

#### **Experimental Workflow:**

Click to download full resolution via product page

Caption: Experimental workflow for PL spectroscopy measurement.

#### Methodology:

- Sample Preparation:

- Ensure the surface of the GaAs sample is clean and free of contaminants. A solvent clean may be necessary.

- Mount Sample in Cryostat:

- Mount the sample on the cold finger of a cryostat. For defect studies, low-temperature measurements (e.g., liquid helium or liquid nitrogen) are often required to sharpen the spectral features.

- Align Excitation and Collection Optics:

- Use a laser with a photon energy greater than the GaAs bandgap as the excitation source (e.g., a He-Ne laser or a Ti:sapphire laser).

- Focus the laser beam onto the sample surface.

- Position the collection optics to efficiently gather the emitted photoluminescence.

- Set Spectrometer Parameters:

- Direct the collected light into a spectrometer.

- Select an appropriate grating and set the center wavelength to the region of interest.

- Set the slit width to achieve the desired spectral resolution.

- Acquire PL Spectrum:

- Use a suitable detector (e.g., a silicon CCD or a photomultiplier tube) to record the PL spectrum.

- Set the integration time to obtain a good signal-to-noise ratio.

- Analyze Spectrum:

- Identify the various peaks in the PL spectrum.

- Determine the peak energy, full width at half maximum (FWHM), and integrated intensity

of each peak.

- If performing temperature-dependent or power-dependent measurements, analyze the evolution of these parameters.

- Identify Transitions:

- Compare the observed peak energies to known transitions in GaAs (see Table 2) to

identify the presence of specific impurities, defects, and excitonic recombinations. The

near-band-edge emission provides information on the overall crystal quality, while deeperlevel emissions are indicative of specific defects.[10]

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. ias.ac.in [ias.ac.in]

- 2. opticaapplicata.pwr.edu.pl [opticaapplicata.pwr.edu.pl]

- 3. researchgate.net [researchgate.net]

- 4. navsea.navy.mil [navsea.navy.mil]

- 5. docs.lib.purdue.edu [docs.lib.purdue.edu]

- 6. researchgate.net [researchgate.net]

- 7. researchgate.net [researchgate.net]

- 8. opticaapplicata.pwr.edu.pl [opticaapplicata.pwr.edu.pl]

- 9. semanticscholar.org [semanticscholar.org]

- 10. Low temperature photoluminescence study of GaAs defect states [cpb.iphy.ac.cn]

- 11. pubs.aip.org [pubs.aip.org]

- To cite this document: BenchChem. [troubleshooting common defects in gallium arsenide semiconductor devices]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b148102#troubleshooting-common-defects-in-gallium-arsenide-semiconductor-devices]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

### BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com