# refining silicon wafer edge processing to reduce chip stacking defects

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |          |           |

|----------------------|----------|-----------|

| Compound Name:       | Silicon  |           |

| Cat. No.:            | B1239273 | Get Quote |

# Technical Support Center: Refining Silicon Wafer Edge Processing

This technical support center provides researchers, scientists, and drug development professionals with detailed troubleshooting guides, FAQs, and experimental protocols to address challenges in **silicon** wafer edge processing for advanced applications like 3D chip stacking.

# Frequently Asked Questions (FAQs)

Q1: What are the most common types of wafer edge defects that impact chip stacking yield?

A1: The most prevalent wafer edge defects include micro-cracks, chipping, particles, thin-film peeling, and scratches.[1][2] These defects can act as stress concentration points, leading to catastrophic wafer breakage during aggressive processing steps like rapid thermal anneal or Chemical Mechanical Polishing (CMP).[1] In chip stacking, such flaws can cause delamination, void formation, and poor bonding integrity, significantly reducing device yield and reliability.[3]

Q2: How does the wafer dicing method affect edge quality and subsequent stacking success?

A2: The dicing method is critical to the final quality of the die edge.

### Troubleshooting & Optimization

- Blade Dicing: This traditional mechanical method can induce significant stress, leading to chipping, micro-cracks, and a larger heat-affected zone.[5][6] Improper parameters, such as high dicing speed or a worn blade, can increase defect density.[5]

- Laser Dicing: Laser-based methods can reduce mechanical stress and produce a smaller kerf width.[7][8] However, they can introduce thermal damage if not optimized.

- Stealth Dicing: This technique creates a modified layer within the silicon, followed by tape

expansion to separate the dies. It is a particle-free process that significantly reduces

mechanical stress and chipping, making it ideal for thin wafers used in stacking.[8]

- Plasma Dicing: This method uses etching to separate dies and is free of mechanical and thermal stress, resulting in very high-quality edges.

Q3: What is the purpose of wafer edge trimming and profiling?

A3: Wafer edge trimming and profiling are processes designed to shape the wafer's edge to a specific geometry.[9] This is crucial for removing the damaged outer layer of the wafer that may contain micro-cracks and other defects from earlier manufacturing stages.[10][11] By creating a smooth, well-defined edge profile (e.g., flat or sloped), it minimizes the risk of edge chipping during handling and subsequent processing, which is essential for achieving high yields in wafer-to-wafer or die-to-wafer bonding.[9][10]

Q4: How can I detect sub-surface or micro-cracks at the wafer edge that are not visible with standard optical inspection?

A4: Detecting sub-surface defects requires non-destructive testing (NDT) methods that can penetrate the **silicon**. Techniques include:

- X-ray Diffraction Imaging (XRDI): This method is sensitive to crystallographic abnormalities and can identify buried defects like dislocations and micro-cracks.[12]

- Infrared Scatterometry: This technique uses infrared light to penetrate through the wafer and detect bulk defects such as voids or air pockets.[1][13]

- Automated Inspection Systems: Modern systems often combine multiple channels (e.g.,

Scatter, Phase, and Specular) to achieve high sensitivity for detecting various defect types,

including small cracks.[14]

## **Troubleshooting Guides**

Problem: High Incidence of Edge Chipping After Dicing

Q: We are observing a high rate of micro-chipping and cracking along the die edges after dicing, which we believe is causing failures during chip stacking. What are the potential causes and how can we troubleshoot this issue?

A: Edge chipping is a common but critical issue that often points to suboptimal parameters in the dicing process or poor initial wafer edge quality. Follow these steps to diagnose and resolve the problem.

Step 1: Investigate the Dicing Process (If using Blade Dicing)

- Check Blade Condition: Is the blade new? A new blade without proper pre-cutting or "dressing" can lead to initial chipping.[5][15] Conversely, a worn-out blade will also cause defects.

- Corrective Action: Implement a standard procedure for pre-cutting with new blades to expose the diamond grit fully.[15] Replace blades based on a defined lifespan or after observing a degradation in cut quality.

- Review Dicing Parameters: Are the feed rate (dicing speed) and spindle rotational speed optimized for your wafer thickness and material?

- Corrective Action: Experiment with reducing the dicing speed. Studies have shown that a 50% reduction in dicing speed can increase chip strength by nearly 13% by reducing mechanical stress.[5] Optimize the feed rate and rotational speed through a Design of Experiments (DOE).

- Verify Blade and Wafer Mounting: Is the wafer securely mounted? Is the blade installed correctly without any tilt?

- Corrective Action: Ensure the wafer is held flat and secure on the chuck. Check the dicing blade for any signs of tilt or improper installation.[15]

#### Step 2: Evaluate Pre-Dicing Wafer Edge Quality

- Inspect Incoming Wafers: Are there pre-existing micro-cracks or damage from handling or previous grinding steps?

- Corrective Action: Introduce an incoming wafer edge inspection step using a high-resolution imaging system or an automated tool.[2][14] Defects introduced before dicing are often the precursors to major chipping.[1]

- Consider Edge Polishing/Trimming: Is the wafer edge sufficiently smooth and robust before dicing?

- Corrective Action: Implement a pre-dicing edge processing step. Edge trimming can remove the fragile, defect-prone region of the wafer, while edge polishing can create a mirror-smooth finish that is more resistant to crack propagation.[10][16][17]

#### Step 3: Assess Alternative Dicing Technologies

- Evaluate Laser or Stealth Dicing: If blade dicing consistently produces unacceptable results, consider alternative technologies.

- Corrective Action: For thin wafers and applications sensitive to mechanical stress, laser or stealth dicing offers superior edge quality by minimizing chipping and cracks.[8][18]

Conduct a feasibility study to compare the yield improvement against the cost of implementation.

## **Quantitative Data Summaries**

Table 1: Comparison of Dicing Technologies on Edge Quality

| Dicing<br>Technology | Primary<br>Mechanism           | Key<br>Advantages                                               | Common<br>Defects                                        | Typical Use<br>Case                                  |

|----------------------|--------------------------------|-----------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------|

| Blade Dicing         | Mechanical<br>Abrasion         | Low cost, high<br>throughput for<br>thick wafers                | Chipping,<br>micro-cracks,<br>mechanical<br>stress[5][6] | Standard<br>microcontrolle<br>rs, memory<br>chips[8] |

| Laser Dicing         | Thermal Ablation               | Reduced<br>mechanical<br>stress, smaller<br>kerf width          | Heat-affected<br>zone (HAZ),<br>recast material          | Thin/fragile<br>wafers, MEMS[8]                      |

| Stealth Dicing       | Internal Laser<br>Modification | No material<br>removal, particle-<br>free, minimal<br>stress[8] | Requires tape expansion step                             | Ultra-thin wafers<br>for stacking[8]                 |

| Plasma Dicing | Chemical Etching | No mechanical or thermal stress, smooth sidewalls | Slower process, higher cost | Advanced packaging, high-aspect-ratio MEMS |

Table 2: Impact of Process Parameters on Wafer Edge Integrity

| Process        | Parameter                | Effect of<br>Optimization                                        | Quantitative<br>Impact<br>(Example)                                                      | Citation |

|----------------|--------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------|

| Blade Dicing   | Dicing Speed             | Reduced<br>speed lowers<br>mechanical<br>stress and<br>chipping. | A 50% speed reduction can increase chip strength by ~13%.                                | [5]      |

| Blade Dicing   | Blade Pre-<br>processing | "Dressing" a new<br>blade is essential<br>for quality.           | Undressed new blade led to a 61% reduction in chip strength.                             | [5]      |

| Edge Polishing | Abrasive Type            | Polishing films can achieve a smoother surface than grinding.    | Surface<br>roughness (Ra)<br>reduced from<br>1639.5 Å<br>(grinder) to 852.5<br>Å (film). | [16]     |

| Edge Trimming | Dimensional Control | Enables precise geometries for better handling and bonding. | Automated systems can achieve +/- 0.15mm edge exclusion zone tolerance. |[9] |

## **Detailed Experimental Protocols**

Protocol 1: Wafer Edge Polishing with Abrasive Tape

This protocol describes a method for polishing the wafer edge to remove micro-cracks and improve surface finish, thereby strengthening the edge against chipping.[4][16]

Objective: To reduce wafer edge surface roughness and remove the defect-prone surface layer.

Materials & Equipment:

• Silicon wafer with processed edge (e.g., after grinding).

- Edge polishing tool equipped with polishing heads.

- Diamond abrasive tape (e.g., 3mm width).[16]

- Deionized (DI) water for lubrication and particle removal.[4]

- Surface profilometer or Atomic Force Microscope (AFM) for roughness measurement.

#### Methodology:

- Preparation: Mount the **silicon** wafer securely onto the polishing tool's chuck.

- Tape Installation: Load the diamond abrasive tape into the polishing head. Ensure the tape is pulled tight and advances continuously during the process to present a fresh abrasive surface.[4]

- Process Parameter Setup:

- Set the polishing head angle to ensure uniform contact with the top edge, bevel, and backside edge.[4]

- Set the polishing pressure and head speed according to a pre-determined recipe. Use soft pressure to minimize the introduction of new defects.[16]

- Initiate the flow of DI water to the polishing interface.

- Polishing Execution:

- Start the wafer rotation and the polishing head movement.

- The tool will press the abrasive tape against the wafer edge, removing material. The DI water will wash away removed particles.

- Continue the process for the specified duration to achieve the target material removal.

- Post-Process Cleaning: After the polishing cycle, perform a final rinse with DI water and a drying step (e.g., spin-dry) to ensure no particles remain on the wafer surface.

#### · Characterization:

- Measure the surface roughness (Ra) of the polished bevel region using an AFM or profilometer.

- Inspect the wafer edge for any remaining defects using a high-resolution optical microscope or an automated inspection tool.

Protocol 2: Laser-Based Wafer Edge Trimming

This protocol outlines the steps for using a laser to trim the outer edge of a wafer, removing defects and creating a precise diameter.

Objective: To remove the mechanically damaged outer zone of the wafer and define a precise edge exclusion zone.

#### Materials & Equipment:

- Silicon wafer.

- Pulsed laser dicing system (e.g., nanosecond or picosecond laser).

- Wafer mounting system (e.g., dicing tape on a frame).

- High-magnification vision system for alignment.

- Post-trim inspection tool.

#### Methodology:

- Mounting: Mount the wafer onto dicing tape within a film frame. Ensure the tape is free of bubbles and the wafer is held flat.

- System Setup and Alignment:

- Load the mounted wafer into the laser dicing system.

- Using the vision system, align the wafer and define the target trim diameter. This will

create the new, smaller wafer diameter, effectively removing the outer edge.

- · Laser Parameter Optimization:

- Set the laser parameters, including pulse frequency, power, and scan speed. These

parameters must be optimized to ablate the silicon cleanly with minimal thermal damage.

- Focus the laser beam precisely on the wafer surface.

- Trimming Execution:

- Initiate the laser trimming process. The laser will ablate the silicon along the defined circular path.

- Multiple passes may be required depending on the wafer thickness and laser power.

- Wafer Separation: After the laser cut is complete, the outer ring of the wafer (the trimmed portion) will remain on the dicing tape, separated from the newly-sized wafer.

- Cleaning and Inspection:

- Perform a post-dicing clean to remove any ablation debris.

- Inspect the new wafer edge for quality, checking for signs of thermal damage, recast material, or micro-cracking. Verify that the final wafer diameter and edge exclusion zone meet specifications.[9]

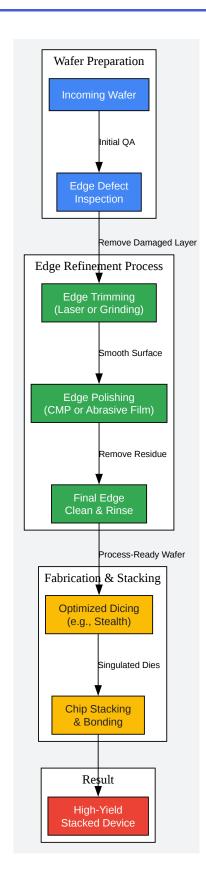

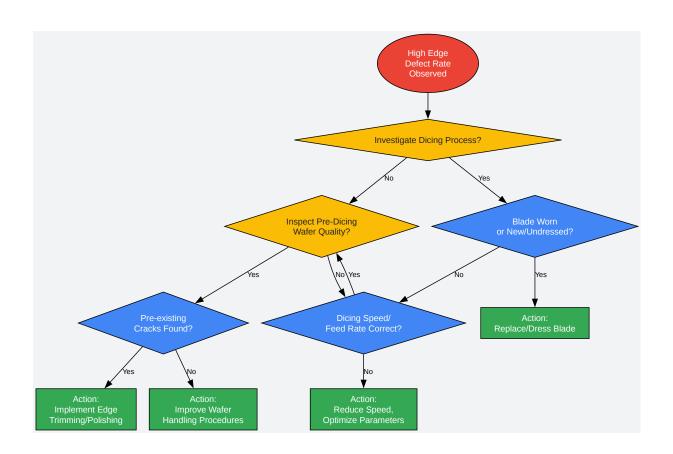

# **Diagrams and Workflows**

Click to download full resolution via product page

Caption: Optimized workflow for wafer edge processing to improve chip stacking yield.

Click to download full resolution via product page

Caption: Troubleshooting decision tree for identifying the root cause of wafer edge defects.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. semiengineering.com [semiengineering.com]

- 2. Savantech | News [savantech.co.uk]

- 3. semiengineering.com [semiengineering.com]

- 4. nccavs-usergroups.avs.org [nccavs-usergroups.avs.org]

- 5. researchgate.net [researchgate.net]

- 6. researchgate.net [researchgate.net]

- 7. researchgate.net [researchgate.net]

- 8. intech-technologies.com [intech-technologies.com]

- 9. waferpro.com [waferpro.com]

- 10. Edge Trim AxusTech [axustech.com]

- 11. US8309464B2 Methods for etching the edge of a silicon wafer Google Patents [patents.google.com]

- 12. news.thomasnet.com [news.thomasnet.com]

- 13. semiengineering.com [semiengineering.com]

- 14. ieeexplore.ieee.org [ieeexplore.ieee.org]

- 15. morediamondwheel.com [morediamondwheel.com]

- 16. isit.fraunhofer.de [isit.fraunhofer.de]

- 17. Edge and Notch Polishing Service | Mipox PRODUCT [product.mipox.co.jp]

- 18. wevolver.com [wevolver.com]

- To cite this document: BenchChem. [refining silicon wafer edge processing to reduce chip stacking defects]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1239273#refining-silicon-wafer-edge-processing-toreduce-chip-stacking-defects]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com