# reducing charge trapping in devices with 5,5'-Dibromo-2,2'-bithiophene polymers

Author: BenchChem Technical Support Team. Date: December 2025

Compound of Interest

Compound Name: 5,5'-Dibromo-2,2'-bithiophene

Cat. No.: B015582

Get Quote

# Technical Support Center: 5,5'-Dibromo-2,2'-bithiophene Polymer Devices

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers and scientists working with devices incorporating **5,5'-Dibromo-2,2'-bithiophene**-based polymers. The information provided is intended to assist in overcoming common experimental challenges and optimizing device performance.

### Frequently Asked Questions (FAQs)

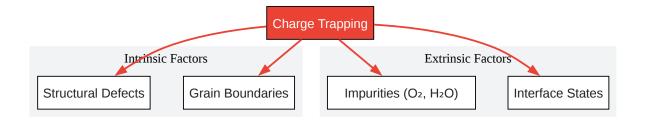

Q1: What are the common sources of charge traps in organic field-effect transistors (OFETs) based on **5,5'-Dibromo-2,2'-bithiophene** polymers?

Charge traps in these devices can be broadly categorized as intrinsic or extrinsic.

- Intrinsic traps originate from the polymer material itself, including structural defects, grain boundaries, and conformational disorder in the polymer chains.

- Extrinsic traps are introduced from external sources. Common extrinsic trap sources include

impurities from the synthesis and purification process, atmospheric contaminants like oxygen

and water, and defects at the semiconductor-dielectric interface.[1][2][3] Molecular oxygen

and water-oxygen complexes, in particular, can introduce deep trap states that significantly

limit charge carrier mobility.[1]

Q2: How does the dielectric interface affect charge trapping and device performance?

The interface between the semiconductor and the gate dielectric is a critical region where charge transport occurs. A high density of trap states at this interface will severely degrade device performance. The choice of dielectric material is crucial. For instance, SiO2 surfaces often have hydroxyl groups that can act as charge trapping sites.[3] In contrast, hydrophobic and chemically inert dielectrics, such as Cytop, tend to form interfaces with a lower density of trap states, leading to improved device performance.[2][3]

Q3: What is the role of thermal annealing in optimizing device performance?

Thermal annealing is a critical post-deposition processing step that can significantly improve the performance of polymer-based OFETs. Proper thermal annealing can:

- Improve the morphology of the polymer film: This leads to better molecular ordering and  $\pi$ - $\pi$  stacking, which facilitates intermolecular charge hopping.

- Reduce charge carrier trapping: By removing residual solvent and improving crystallinity, annealing can reduce the density of trap states.

- Lower contact resistance: Annealing can improve the contact between the polymer and the source/drain electrodes.

The annealing temperature is a critical parameter and needs to be optimized for each specific polymer.[4][5][6]

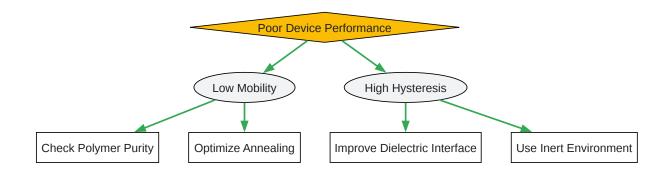

Q4: What causes hysteresis in the transfer characteristics of my OFETs?

Hysteresis, the difference in the current-voltage (I-V) curve during forward and reverse voltage sweeps, is a common issue in OFETs and is often attributed to charge trapping.[3] Slow trapping and de-trapping of charge carriers at the semiconductor-dielectric interface or within the bulk of the semiconductor are primary causes. Bias stress, where the device is held at a constant gate voltage, can exacerbate this effect.[7] The choice of gate insulator can play a significant role in mitigating hysteresis.[7]

# **Troubleshooting Guides**

### Troubleshooting & Optimization

Check Availability & Pricing

This section provides solutions to common problems encountered during the fabrication and characterization of **5,5'-Dibromo-2,2'-bithiophene** polymer devices.

# Troubleshooting & Optimization

Check Availability & Pricing

| Problem                        | Possible Causes                                                                                                                                 | Recommended Solutions                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low Charge Carrier Mobility    | - High density of charge traps due to impurities Poor morphology of the polymer film High contact resistance Sub-optimal annealing temperature. | - Ensure high purity of the 5,5'-Dibromo-2,2'-bithiophene monomer and the final polymer Optimize the solvent and deposition conditions (e.g., spin coating speed, substrate temperature) to improve film quality Treat the source/drain electrodes with a suitable self-assembled monolayer (SAM) to reduce contact resistance Systematically vary the annealing temperature to find the optimal condition for your specific polymer.[5] |

| Large Hysteresis in I-V Curves | - Charge trapping at the semiconductor-dielectric interface Presence of mobile ions in the dielectric layer Water or oxygen contamination.      | - Use a hydrophobic and chemically inert gate dielectric (e.g., Cytop, PMMA) to minimize interface traps.[3] - Ensure the dielectric layer is of high quality and free from mobile ions Fabricate and characterize the devices in an inert atmosphere (e.g., a glovebox) to minimize exposure to air and moisture.                                                                                                                       |

| High Off-State Current         | - Impurities in the semiconductor leading to unintentional doping Gate leakage current.                                                         | - Rigorously purify the polymer to remove any ionic or metallic impurities Verify the integrity of the gate dielectric to ensure there are no pinholes or defects that could lead to leakage.                                                                                                                                                                                                                                            |

|                                         |                                                                                                                          | - Improve the quality of the                                  |  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|

|                                         |                                                                                                                          | semiconductor-dielectric                                      |  |

| Device Instability under Bias<br>Stress | - Trapping of charge carriers in deep trap states Electrochemical reactions at the contacts or within the semiconductor. | interface to reduce the density                               |  |

|                                         |                                                                                                                          | of deep traps Use stable                                      |  |

|                                         |                                                                                                                          | electrode materials and ensure a clean fabrication process to |  |

|                                         |                                                                                                                          |                                                               |  |

|                                         |                                                                                                                          | reactions Encapsulate the                                     |  |

|                                         |                                                                                                                          |                                                               |  |

|                                         |                                                                                                                          | ambient environment.                                          |  |

|                                         |                                                                                                                          |                                                               |  |

## **Quantitative Data**

The following table summarizes representative performance parameters for OFETs based on bithiophene-containing polymers. Note that the exact values for devices with **5,5'-Dibromo-2,2'-bithiophene** polymers will depend on the specific molecular structure, device architecture, and processing conditions.

| Polymer Type                                        | Dielectric       | Annealing<br>Temp. (°C) | Hole Mobility<br>(cm²/Vs)  | On/Off Ratio      |

|-----------------------------------------------------|------------------|-------------------------|----------------------------|-------------------|

| Bithiophene-<br>Imide Copolymer<br>(p-type)         | Top-gate         | N/A                     | ~10 <sup>-2</sup>          | > 10 <sup>5</sup> |

| Fluorene-<br>Bithiophene<br>Copolymer (p-<br>type)  | SiO <sub>2</sub> | 100                     | up to 5 x 10 <sup>-3</sup> | N/A               |

| Naphthalene Diimide- Bithiophene Analogue (n- type) | N/A              | < Tm                    | ~10 <sup>-3</sup>          | N/A               |

### **Experimental Protocols**

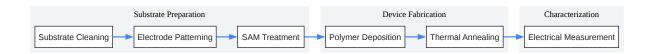

#### 1. OFET Fabrication (Bottom-Gate, Bottom-Contact)

This protocol outlines a general procedure for fabricating OFETs. Optimization of specific parameters is recommended.

#### Substrate Cleaning:

- Ultrasonically clean heavily doped Si wafers with a thermally grown SiO<sub>2</sub> layer in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrates with a stream of nitrogen.

- Treat the substrates with an oxygen plasma or a piranha solution to create a hydrophilic surface.

#### Electrode Patterning:

- Define the source and drain electrodes using standard photolithography.

- Deposit a thin adhesion layer (e.g., 5 nm of Cr or Ti) followed by the electrode material (e.g., 50 nm of Au) using thermal evaporation.

- Perform lift-off in a suitable solvent (e.g., acetone).

- Dielectric Surface Treatment (Optional but Recommended):

- To improve the interface quality, treat the SiO<sub>2</sub> surface with a self-assembled monolayer (SAM) such as octadecyltrichlorosilane (OTS).

- Polymer Film Deposition:

- Dissolve the 5,5'-Dibromo-2,2'-bithiophene polymer in a suitable organic solvent (e.g., chloroform, chlorobenzene) at a specific concentration.

- Deposit the polymer film onto the substrate using spin coating. The spin speed and time should be optimized to achieve the desired film thickness.

- Thermal Annealing:

- Anneal the samples on a hotplate in an inert atmosphere (e.g., a glovebox) at the optimized temperature and for a specific duration.

- Characterization:

- Measure the transfer and output characteristics of the OFETs using a semiconductor parameter analyzer in an inert environment.

- 2. Quantitative Analysis of Trap States (Grünewald's Method)

This method allows for the extraction of the density of trap states (DOS) from the transfer characteristics of the OFET.[1]

- Measure the transfer characteristics (ID vs. VG) of the OFET in the linear regime (low VD).

- Calculate the interface potential (ψs) as a function of the gate voltage (VG).

- The density of trap states N(E) can then be calculated using the following relationship:

$$N(E) = (1/q) * (d^2\psi s/dVG^2) * Ci$$

where q is the elementary charge and Ci is the capacitance per unit area of the gate dielectric.

### **Visualizations**

Click to download full resolution via product page

Caption: Workflow for the fabrication of a bottom-gate, bottom-contact organic field-effect transistor.

Click to download full resolution via product page

Caption: Common intrinsic and extrinsic causes of charge trapping in polymer-based OFETs.

Click to download full resolution via product page

Caption: A logical flow for troubleshooting common issues in OFET device performance.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

• 1. fkf.mpg.de [fkf.mpg.de]

- 2. researchgate.net [researchgate.net]

- 3. uknowledge.uky.edu [uknowledge.uky.edu]

- 4. researchgate.net [researchgate.net]

- 5. Temperature-dependent morphology-electron mobility correlations of naphthalene diimideindacenodithiophene copolymers prepared via direct arylation po ... - Materials Advances (RSC Publishing) DOI:10.1039/D1MA00633A [pubs.rsc.org]

- 6. pure.mpg.de [pure.mpg.de]

- 7. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [reducing charge trapping in devices with 5,5'-Dibromo-2,2'-bithiophene polymers]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b015582#reducing-charge-trapping-in-devices-with-5-dibromo-2-2-bithiophene-polymers]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com