# performance comparison of HfO2 films in MOS devices

Author: BenchChem Technical Support Team. Date: December 2025

Compound of Interest

Compound Name: ethyl(methyl)azanide;hafnium(4+)

Cat. No.: B1587031

Get Quote

A Comparative Guide to the Performance of Hafnium Oxide (HfO2) Films in MOS Devices

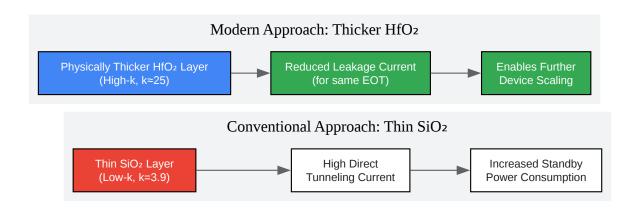

As the scaling of Metal-Oxide-Semiconductor (MOS) devices continues, traditional silicon dioxide (SiO<sub>2</sub>) gate dielectrics face fundamental limitations due to excessive leakage currents at reduced thicknesses.[1][2] This has necessitated the adoption of high-k dielectric materials, which allow for a physically thicker film while maintaining a low equivalent oxide thickness (EOT), thus mitigating quantum tunneling effects.[3][4] Among various candidates, Hafnium Oxide (HfO<sub>2</sub>) has emerged as one of the most promising and widely adopted high-k materials due to its high dielectric constant, good thermal stability in contact with silicon, and a relatively large bandgap.[1][5][6]

This guide provides an objective comparison of HfO<sub>2</sub> performance against SiO<sub>2</sub> and other high-k alternatives, supported by experimental data from peer-reviewed studies.

#### **Data Presentation: Performance Metrics**

The performance of a gate dielectric in a MOS device is evaluated through several key metrics. HfO<sub>2</sub> generally offers a significant reduction in leakage current for the same EOT compared to SiO<sub>2</sub>, although it can present challenges such as higher interface trap densities.

# Table 1: Physical and Electrical Properties of Selected Gate Dielectrics

| Property                                  | SiO <sub>2</sub> | HfO <sub>2</sub> | Al <sub>2</sub> O <sub>3</sub> | ZrO₂ |

|-------------------------------------------|------------------|------------------|--------------------------------|------|

| Dielectric<br>Constant (k)                | 3.9[7]           | ~25[1][6]        | ~9[4]                          | ~25  |

| Band Gap (eV)                             | 9[7]             | 5.6 - 5.8[1][7]  | ~8.8[8]                        | 5.8  |

| Conduction Band<br>Offset with Si<br>(eV) | 3.2              | 1.5 - 2.2[9][10] | 2.8                            | 1.4  |

# **Table 2: Comparative Performance Data of HfO₂ in MOS**

**Devices**

| Performance Metric                                                | HfO₂ Films                               | SiO₂ (for<br>comparison)                                               | Other High-k Films                                                          |

|-------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Equivalent Oxide<br>Thickness (EOT)                               | 2.9 nm[1]                                | -                                                                      | 0.93 nm (HfO₂/In₂O₃<br>stack)[11]                                           |

| 0.75 - 0.82 nm[12]                                                | -                                        | -                                                                      |                                                                             |

| Leakage Current<br>Density (A/cm²)                                | 3.09 x 10 <sup>-6</sup> @<br>-1.5V[1]    | > 100 @ 1V (for 1nm<br>film)[2]                                        | $< 10^{-7}$ (HfO <sub>2</sub> -Al <sub>2</sub> O <sub>3</sub> laminate)[13] |

| 1.5 x 10 <sup>-5</sup> @ -2V[8]                                   | -                                        | 9.24 nA (Nb₂O₅), 7.8<br>nA (ZnO) @ 1V[14]                              |                                                                             |

| < 5 @ VFB+1V (for<br>sub-1nm EOT)[12]                             | -                                        | -                                                                      | _                                                                           |

| Breakdown Electric<br>Field (MV/cm)                               | > 20[1]                                  | -                                                                      | -                                                                           |

| Interface Trap Density (Dit) (cm <sup>-2</sup> eV <sup>-1</sup> ) | 6.3 x 10 <sup>12</sup> (mean)[8]<br>[15] | -                                                                      | 3.84 x 10 <sup>13</sup> (Al-doped<br>HfO <sub>2</sub> )[16]                 |

| 7.76 x 10 <sup>12</sup> (max)[8]<br>[15]                          | -                                        | 2.18 x 10 <sup>11</sup> (on<br>Ge <sub>3</sub> N <sub>4</sub> /Ge)[17] |                                                                             |

| 10 <sup>10</sup> (on SiC)[18]                                     | -                                        | 10 <sup>13</sup> (on InGaAs)[19]                                       | -                                                                           |

## **Experimental Protocols and Methodologies**

The performance characteristics detailed above are highly dependent on the fabrication and processing of the MOS device. The following sections describe typical experimental protocols for creating and testing HfO<sub>2</sub>-based MOS capacitors.

## Fabrication of HfO<sub>2</sub> MOS Capacitors

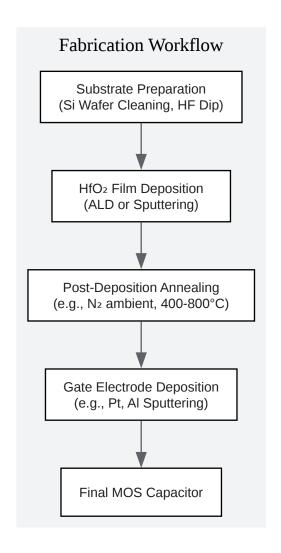

A typical fabrication process involves substrate cleaning, dielectric deposition, electrode metallization, and annealing.

- Substrate Preparation: The process begins with cleaning a p-type or n-type silicon (Si) wafer. A common procedure is the RCA clean, followed by a dip in hydrofluoric acid (HF) to remove the native oxide layer.[1]

- Dielectric Deposition: The HfO<sub>2</sub> thin film is deposited onto the clean Si substrate. Common techniques include:

- Atomic Layer Deposition (ALD): This method allows for precise thickness control and excellent film uniformity, making it suitable for ultrathin gate dielectrics.[11][18]

- Ion Beam Sputtering: A sintered HfO<sub>2</sub> target is sputtered to deposit a thin film on the substrate.[1][5]

- Pulsed-Laser Deposition (PLD): This technique is also used for depositing HfO<sub>2</sub> films for MIM (Metal-Insulator-Metal) capacitors.[20]

- Post-Deposition Annealing (PDA): After deposition, the film is often annealed in a nitrogen

(N2) or oxygen (O2) ambient at various temperatures (e.g., 400-800°C).[1] This step is crucial

for densifying the film, reducing defects, and improving the interfacial quality.

- Electrode Deposition: A metal top electrode (e.g., Platinum, Aluminum, Molybdenum) is deposited, typically by sputtering or thermal evaporation, through a shadow mask to define the capacitor area.[1][21][22] An ohmic contact is also formed on the backside of the wafer.

### **Electrical Characterization**

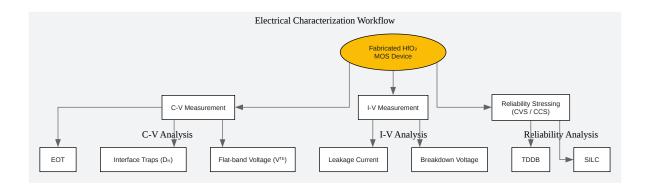

The primary techniques for evaluating the electrical properties of the MOS capacitor are Capacitance-Voltage (C-V) and Current-Voltage (I-V) measurements.

- Capacitance-Voltage (C-V) Measurement: A varying DC bias with a superimposed small AC signal is applied across the MOS capacitor. The resulting capacitance is measured to determine key parameters like EOT, flat-band voltage (Vfb), and interface trap density (Dit).

[1][15] Dit can be estimated using methods like the high-low frequency capacitance method or the conductance method.[11][15]

- Current-Voltage (I-V) Measurement: The gate leakage current is measured as a function of the applied gate voltage. This provides information about the insulating properties of the dielectric and is used to determine the leakage current density and the breakdown voltage.

[1][15]

- Reliability Testing: To assess long-term reliability, tests such as Time-Dependent Dielectric Breakdown (TDDB) and Stress-Induced Leakage Current (SILC) are performed, where the device is subjected to constant voltage or current stress.[5][21]

## **Mandatory Visualizations**

The following diagrams illustrate the experimental workflows and logical comparisons related to HfO<sub>2</sub> in MOS devices.

Click to download full resolution via product page

Fig 1. Generalized workflow for HfO2 MOS capacitor fabrication.

Click to download full resolution via product page

Fig 2. Workflow for electrical characterization of HfO2 MOS devices.

Click to download full resolution via product page

Fig 3. Logical comparison of using HfO2 versus traditional SiO2.

## **Reliability and Performance Challenges**

While HfO<sub>2</sub> successfully addresses the leakage current problem, its integration introduces other challenges that must be managed.

- Interface Quality: The interface between HfO<sub>2</sub> and the silicon substrate is critical. A common issue is the formation of an unintentional, lower-quality interfacial layer (often SiOx or silicate) during deposition and annealing.[5] This layer can increase the overall EOT and introduce a high density of interface traps (Dit).[15][23] These traps can degrade carrier mobility and affect the device's threshold voltage stability.

- Charge Trapping: HfO<sub>2</sub> films, particularly those with defects in the bulk, can be prone to charge trapping under voltage stress. This can cause significant shifts in the flat-band and threshold voltages, impacting the long-term reliability and performance of the device.[9]

- Reliability: Studies on stress-induced leakage current (SILC) and time-dependent dielectric breakdown (TDDB) indicate that HfO<sub>2</sub> generally exhibits good reliability.[5] However, soft breakdown behavior has been observed under stress conditions.[5][21] The choice of metal gate electrode also significantly influences reliability characteristics, with materials like Molybdenum (Mo) showing excellent breakdown voltage and reliability.[21]

## Conclusion

Hafnium Oxide (HfO<sub>2</sub>) has established itself as the leading high-k dielectric material for replacing SiO<sub>2</sub> in advanced MOS devices. Its high dielectric constant enables the fabrication of transistors with low equivalent oxide thickness and significantly reduced gate leakage current, a critical factor for continued CMOS scaling.[3][24] While challenges related to interface trap density and charge trapping persist, they can be mitigated through process optimization, such as doping (e.g., with Al or N), the use of interfacial layers, and appropriate annealing techniques.[4][9][16] The extensive research and development in HfO<sub>2</sub>-based gate stacks have been pivotal in enabling the performance gains seen in sub-100nm semiconductor technology nodes.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. electrochem.org [electrochem.org]

- 2. Why use hafnium oxide in a mos versus silicon dioxide? FUNCMATER [funcmater.com]

- 3. irjet.net [irjet.net]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. researchgate.net [researchgate.net]

- 7. lup.lub.lu.se [lup.lub.lu.se]

- 8. researchgate.net [researchgate.net]

- 9. repositories.lib.utexas.edu [repositories.lib.utexas.edu]

- 10. researchgate.net [researchgate.net]

- 11. Frontiers | Characterization of Interface and Bulk Traps in Ultrathin Atomic Layer-Deposited Oxide Semiconductor MOS Capacitors With HfO2/In2O3 Gate Stack by C-V and Conductance Method [frontiersin.org]

- 12. researchgate.net [researchgate.net]

- 13. mdpi.com [mdpi.com]

- 14. eejournal.ktu.lt [eejournal.ktu.lt]

- 15. scholar.lib.ntnu.edu.tw [scholar.lib.ntnu.edu.tw]

- 16. pure.korea.ac.kr [pure.korea.ac.kr]

- 17. researchgate.net [researchgate.net]

- 18. Electrical characterization of HfO>2>/4H-SiC and HfO>2>/Si MOS structures Xi'an Jiaotong-Liverpool University [scholar.xjtlu.edu.cn]

- 19. pubs.aip.org [pubs.aip.org]

- 20. Material and Electrical Characterization of HfO2 Films for MIM Capacitors Application |

MRS Online Proceedings Library (OPL) | Cambridge Core [resolve.cambridge.org]

- 21. Electrical and Reliability Characteristics of HfO2 MOS Capacitor with Mo Metal Gate Electrode [jkps.or.kr]

- 22. researchgate.net [researchgate.net]

- 23. tsapps.nist.gov [tsapps.nist.gov]

- 24. files.core.ac.uk [files.core.ac.uk]

- To cite this document: BenchChem. [performance comparison of HfO2 films in MOS devices]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1587031#performance-comparison-of-hfo2-films-in-mos-devices]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com