# minimizing defects in solution-processed 5-Methoxy-12-phenylrubicene transistors

Author: BenchChem Technical Support Team. Date: December 2025

Compound of Interest

Compound Name: 5-Methoxy-12-phenylrubicene

Cat. No.: B15171363 Get Quote

# Technical Support Center: 5-Methoxy-12-phenylrubicene Transistors

Disclaimer: While specific experimental data for **5-Methoxy-12-phenylrubicene** is not extensively available in public literature, this guide provides troubleshooting and fabrication protocols based on well-established principles for solution-processed small-molecule organic thin-film transistors (OTFTs). Researchers can adapt these general guidelines for their work with **5-Methoxy-12-phenylrubicene**.

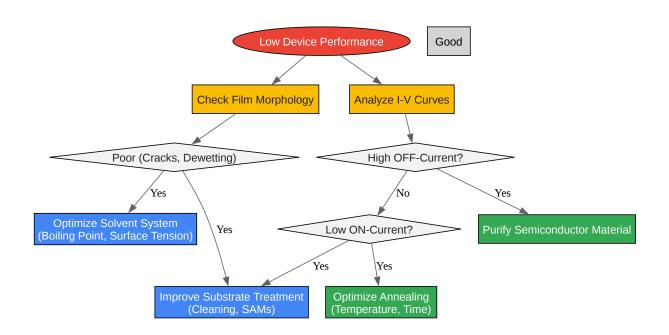

#### **Troubleshooting Guide**

This guide addresses common issues encountered during the solution-processing of small-molecule organic semiconductor devices.

## Troubleshooting & Optimization

Check Availability & Pricing

| Issue                                                                  | Potential Cause                                                                                                                                                                                                               | Recommended Solution                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low Charge Carrier Mobility                                            | Poor crystallinity and molecular ordering in the semiconductor film.                                                                                                                                                          | - Optimize the solvent system. A solvent with a higher boiling point can slow down the evaporation rate, allowing more time for molecular self-assembly Experiment with different substrate temperatures during deposition Implement a post-deposition annealing step. Systematically vary the annealing temperature and time to find the optimal conditions for improving crystallinity. |

| High density of trap states at the semiconductor-dielectric interface. | - Treat the dielectric surface with a self-assembled monolayer (SAM), such as octadecyltrichlorosilane (OTS), to reduce surface energy and passivate trap sites Ensure the substrate is scrupulously clean before deposition. |                                                                                                                                                                                                                                                                                                                                                                                           |

| High OFF-Current                                                       | Impurities in the semiconductor material.                                                                                                                                                                                     | - Purify the 5-Methoxy-12-<br>phenylrubicene using<br>techniques like temperature<br>gradient sublimation or<br>recrystallization.                                                                                                                                                                                                                                                        |

| Gate leakage through the dielectric layer.                             | - Verify the integrity and thickness of the gate dielectric Ensure there are no pinholes or defects in the dielectric layer.                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                           |

| Poor Film Morphology (Cracks,<br>Dewetting, Coffee Rings) | Mismatched surface energies between the solution and the substrate.                                                                                                                            | - Modify the substrate surface energy using SAMs to improve solution wetting Adjust the solution concentration. A lower concentration can sometimes lead to more uniform films.                   |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rapid and non-uniform solvent evaporation.                | - Use a solvent with a higher boiling point Employ deposition techniques that offer better control over evaporation, such as blade coating or solution shearing in a controlled environment.   |                                                                                                                                                                                                   |

| High Device-to-Device<br>Variability                      | Inconsistent deposition conditions across the substrate.                                                                                                                                       | - Ensure uniform substrate temperature during deposition Optimize the deposition technique (e.g., spin-coating speed and acceleration, blade-coating speed) to achieve consistent film thickness. |

| Inhomogeneous solution.                                   | - Ensure the 5-Methoxy-12- phenylrubicene is fully dissolved before deposition. Gentle heating or sonication may be necessary Filter the solution before use to remove any particulate matter. |                                                                                                                                                                                                   |

## **Frequently Asked Questions (FAQs)**

Q1: How does the choice of solvent affect the performance of **5-Methoxy-12-phenylrubicene** transistors?

#### Troubleshooting & Optimization

A1: The solvent plays a critical role in determining the morphology and crystallinity of the solution-processed semiconductor film. Key solvent properties to consider are:

- Boiling Point: A higher boiling point allows for slower solvent evaporation, which can provide

more time for the molecules to self-organize into well-ordered crystalline domains, potentially

leading to higher charge carrier mobility.

- Solubility: The solubility of **5-Methoxy-12-phenylrubicene** in the chosen solvent will dictate the solution concentration and can influence the nucleation and growth of crystals.

- Surface Tension: The solvent's surface tension affects how the solution wets the substrate, influencing film uniformity and helping to prevent dewetting.

Q2: What is the purpose of treating the dielectric surface with a Self-Assembled Monolayer (SAM)?

A2: Treating the dielectric surface (e.g., SiO<sub>2</sub>) with a SAM serves two primary purposes. First, it can passivate surface hydroxyl groups (-OH) which are known to act as electron traps, thereby reducing the density of trap states at the critical semiconductor-dielectric interface. Second, SAMs can modify the surface energy of the dielectric, promoting more favorable growth of the organic semiconductor and leading to improved film morphology and molecular ordering.

Q3: What is the typical effect of post-deposition annealing on the transistor characteristics?

A3: Post-deposition thermal annealing, typically performed at a temperature below the melting point of the organic semiconductor, can provide the thermal energy necessary to promote the rearrangement of molecules into a more ordered crystalline structure. This can lead to a reduction in grain boundaries and structural defects, often resulting in an increase in charge carrier mobility and a decrease in the threshold voltage. However, excessive annealing temperatures or durations can sometimes lead to film dewetting or degradation of the semiconductor.

Q4: What are the most common sources of defects in solution-processed OTFTs?

A4: Defects in solution-processed OTFTs can be broadly categorized as:

- Structural Defects: These include grain boundaries, dislocations, and vacancies within the crystalline domains of the organic semiconductor. These disrupt the pathways for charge transport.

- Chemical Impurities: Residual solvent molecules, atmospheric contaminants (e.g., water, oxygen), or impurities from the synthesis of the semiconductor can introduce electronic trap states.

- Interfacial Defects: Traps and charge scattering sites at the interface between the semiconductor and the dielectric, electrodes, or ambient environment are critical to device performance.

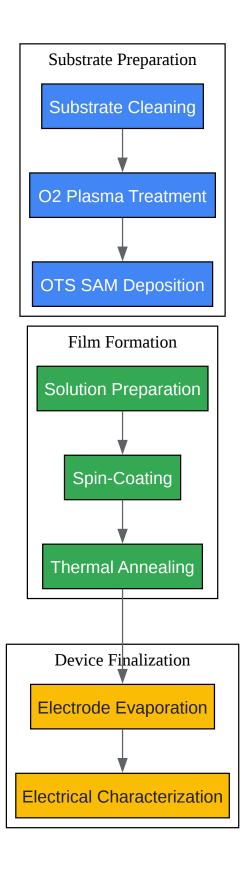

# Experimental Protocols Protocol 1: Fabrication of a Bottom-Gate, Top-Contact OTFT

- Substrate Cleaning:

- Sequentially sonicate the heavily n-doped Si wafers with a thermally grown SiO<sub>2</sub> layer

(300 nm) in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrates with a stream of dry nitrogen.

- Treat the substrates with an O<sub>2</sub> plasma for 5 minutes to remove any organic residues and create a hydrophilic surface.

- Dielectric Surface Treatment (OTS Deposition):

- Place the cleaned substrates in a vacuum desiccator along with a small vial containing a few drops of octadecyltrichlorosilane (OTS).

- Evacuate the desiccator to allow for vapor-phase deposition of the OTS monolayer for 2 hours.

- After deposition, sonicate the substrates in toluene and isopropanol to remove any physisorbed OTS molecules.

- Dry the substrates with dry nitrogen.

- Semiconductor Solution Preparation:

- Prepare a solution of **5-Methoxy-12-phenylrubicene** in a high-boiling-point solvent (e.g., toluene, chlorobenzene, or a mixture) at a concentration of **5-10** mg/mL.

- Gently heat the solution (e.g., at 40-60 °C) while stirring to ensure complete dissolution.

- Filter the solution through a 0.2 μm PTFE filter before use.

- Thin-Film Deposition (Spin-Coating):

- Place the OTS-treated substrate on the spin-coater chuck.

- Dispense the filtered semiconductor solution onto the substrate.

- Spin-coat at 2000 RPM for 60 seconds.

- Transfer the coated substrate to a hotplate for solvent removal at 80-100 °C for 10 minutes.

- Post-Deposition Annealing:

- Anneal the semiconductor film in a nitrogen-filled glovebox at a temperature of 120-150 °C for 30 minutes.

- Allow the film to cool slowly to room temperature.

- Electrode Deposition:

- Using a shadow mask, thermally evaporate 50 nm of gold (Au) for the source and drain electrodes at a rate of 0.1-0.2 Å/s. The channel length and width are defined by the mask.

- Characterization:

- Measure the electrical characteristics of the transistor in a nitrogen environment using a semiconductor parameter analyzer.

#### **Visualizations**

Click to download full resolution via product page

Caption: Experimental workflow for OTFT fabrication.

Click to download full resolution via product page

Caption: Troubleshooting logic for low-performance devices.

• To cite this document: BenchChem. [minimizing defects in solution-processed 5-Methoxy-12-phenylrubicene transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b15171363#minimizing-defects-in-solution-processed-5-methoxy-12-phenylrubicene-transistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide

accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

#### BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com