# improving light extraction efficiency in AlGaInP LEDs

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                  |           |

|----------------------|------------------|-----------|

| Compound Name:       | Aluminum;gallium |           |

| Cat. No.:            | B14657816        | Get Quote |

# **Technical Support Center: AlGaInP LEDs**

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and professionals in overcoming common challenges encountered during experiments aimed at improving light extraction efficiency (LEE) in AlGaInP light-emitting diodes (LEDs).

# **Troubleshooting Guide**

This guide addresses specific issues that may arise during the fabrication and testing of AlGaInP LEDs, providing potential causes and solutions in a question-and-answer format.

Issue 1: Low Light Output Power (LOP) or External Quantum Efficiency (EQE) After Surface Texturing.

- Question: My surface texturing process is complete, but the expected improvement in LOP is minimal or non-existent. What could be the cause?

- Answer: Several factors could be at play. First, the etching process parameters may be suboptimal. For wet etching, as the etching time is prolonged, the density of beneficial features like pores may increase initially but then decrease, diminishing the light scattering effect[1][2]. Second, the texturing process might have introduced surface defects, leading to non-radiative recombination and reducing the internal quantum efficiency (IQE)[3]. Finally, the geometry of the textured features is critical. For instance, sub-wavelength structures

## Troubleshooting & Optimization

must have a tapered profile and appropriate periodicity to effectively reduce Fresnel reflection[4]. It's also possible that another factor, such as current crowding or photon absorption in a contact layer, is the primary limiter of your device's efficiency[5][6].

Issue 2: Increased Forward Voltage or Device Failure at High Currents.

- Question: After applying a current spreading layer (e.g., Indium Tin Oxide ITO), the device's forward voltage increases significantly under high current stress, sometimes leading to failure. Why is this happening?

- Answer: This issue often points to the degradation of the current spreading layer itself. ITO films can experience degradation and increased series resistance when subjected to high current stress, a phenomenon that is less pronounced at high temperatures alone[7]. This degradation may be caused by current crowding in the ITO film, especially around the p-type electrode[7]. Using a thicker ITO layer can improve reliability and reduce the voltage increase[7]. Another cause could be device self-heating, which stimulates electron leakage into the p-side of the structure, particularly when current is crowded around the p-electrode[5][6].

Issue 3: Inconsistent or Poor Results with Photonic Crystal (PhC) Structures.

- Question: The enhancement from my photonic crystals is lower than theoretical predictions and less effective than simple surface roughening. What is the problem?

- Answer: Photonic crystals are highly design-dependent and extract a limited range of light modes with high efficiency, while other modes are not extracted at all[8]. In contrast, random surface roughening scatters light into all directions, providing a broader, albeit potentially less optimized, enhancement[8]. Your PhC design (lattice type, constant, etch depth) may not be optimized for your device's specific mode distribution[8]. Furthermore, the fabrication process for PhCs can be complex. For embedded PhCs, the etching process removes part of the active region, which can increase current density and lead to serious heat generation, causing the LOP to decay earlier, especially at high injection currents[9][10][11].

Issue 4: Cracking or Damage During Substrate Removal.

Question: I am trying to create a thin-film vertical LED (VLED), but the AlGaInP epilayer cracks when I perform the epitaxial lift-off (ELO) process. How can I prevent this?

Answer: Crack formation during the ELO process is a common issue caused by stress

distribution in the epilayer as the sacrificial layer is etched[12][13]. The design of the new

carrier substrate is critical. Using a patterned metallic substrate (e.g., Cu) can help manage

this stress by confining the maximum stress to the edges of the chip[12][13]. Finite element

method (FEM) simulations can be used to determine an optimal pattern for the carrier

substrate that significantly decreases stress during the ELO process, reducing crack

generation[12][13].

# Frequently Asked Questions (FAQs)

Q1: What are the primary barriers to high light extraction efficiency in AlGaInP LEDs?

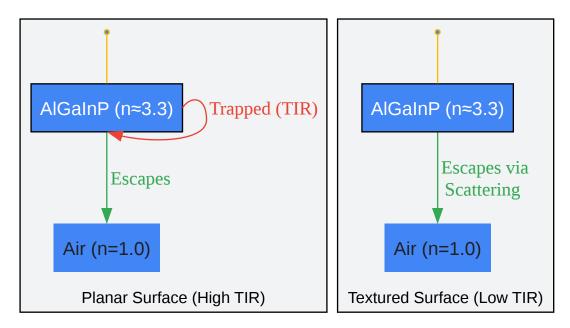

A1: The primary barrier is the large difference in refractive index between the AlGaInP semiconductor material ( $n \approx 3.3$ ) and the surrounding air (n = 1)[14]. This leads to a narrow escape cone for light, causing a severe phenomenon known as total internal reflection (TIR), where a majority of the generated light is trapped within the device[1][14]. Other significant loss mechanisms include Fresnel reflection at the semiconductor-air interface, light absorption by the GaAs substrate or opaque metal contacts, and inefficient current spreading[1][4][15][16] [17].

Q2: What are the most common experimental techniques to improve LEE?

A2: Numerous methods have been developed to enhance LEE. The most common include:

- Surface Texturing/Roughening: Creating features on the LED surface to scatter trapped light and give it multiple opportunities to escape, effectively suppressing TIR[1][18][19][20].

- Photonic Crystals (PCs): Fabricating periodic dielectric structures that interact with guided light modes, diffracting them into the extraction cone[8][9].

- Substrate Removal/Wafer Bonding: Removing the light-absorbing GaAs substrate and bonding the thin AlGaInP epilayer to a reflective or transparent carrier, often to create a vertical device architecture[17][21].

- Chip Shaping: Modifying the geometry of the LED die (e.g., into a truncated-inverted-pyramid) to provide multiple escape routes for light[14].

• Improved Current Spreading: Using transparent conductive layers (e.g., ITO) or current blocking layers to ensure uniform current injection across the active region, preventing light generation under opaque electrodes[15][16].

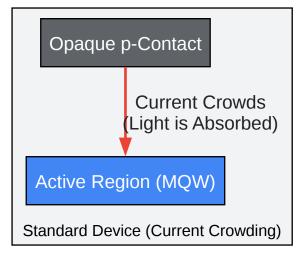

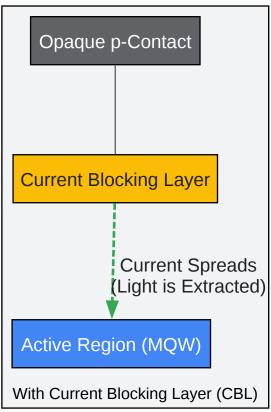

Q3: How does a current blocking layer (CBL) work to improve efficiency?

A3: In vertical LEDs, current tends to crowd around the p-electrode. Since this electrode is typically opaque, any light generated directly beneath it is absorbed or reflected back into the device, lowering LEE[16]. A current blocking layer, often made of an insulating material like SiO<sub>2</sub> or a Schottky contact, is placed directly under the p-electrode[1][16]. This layer forces the current to flow around it and spread more uniformly into the active region, avoiding the area under the opaque contact and thereby improving both current distribution and light extraction[16].

Q4: What is the difference between surface and embedded photonic crystals?

A4: A surface photonic crystal (SPCLED) is fabricated on the top surface of the completed LED structure. An embedded photonic crystal (EPCLED) is created by etching the PC pattern into an underlying layer (e.g., the p-type cladding layer) before subsequent layers are grown or deposited over it[9][10][11]. EPCLEDs can show higher photoluminescence intensity enhancement, but the fabrication process can damage the active region, leading to greater heat generation and a potential drop in LOP at higher currents compared to SPCLEDs[9][10] [11].

# **Data on Efficiency Enhancements**

The following table summarizes quantitative data on the performance improvements achieved through various LEE enhancement techniques for AlGaInP LEDs.

| Enhancement<br>Technique                          | Metric                               | Improvement<br>Reported                               | Reference  |

|---------------------------------------------------|--------------------------------------|-------------------------------------------------------|------------|

| Surface Texturing<br>(Porous n-AlGaInP)           | External Quantum<br>Efficiency (EQE) | 38.9% increase at 20 mA                               | [1][2][18] |

| Surface Texturing<br>(Periodic, Bowl-<br>shaped)  | Light Output Power (LOP)             | 45.7% increase (from<br>81 mW to 118 mW) at<br>350 mA | [22]       |

| Surface Texturing (n-side roughening)             | Light Output Power (LOP)             | 1.6 times higher than flat-surface LED at 20 mA       | [19][20]   |

| Antireflection Coating (SiON)                     | Optical Power                        | 11.38% increase after packaging                       | [23]       |

| Evanescent Wave Coupling (Sub- wavelength ridges) | Light Output Power (LOP)             | Enhancement factor of ~3.8                            | [14]       |

| Surface Photonic<br>Crystal (SPCLED)              | Light Output Power (LOP)             | 24% increase at 200 mA                                | [10][11]   |

| Embedded Photonic<br>Crystal (EPCLED)             | Light Output Power (LOP)             | 11% increase at 200 mA                                | [10][11]   |

| Schottky-Contact Current Blocking Layer (SCBL)    | External Quantum<br>Efficiency (EQE) | 31.8% increase at 20<br>mA                            | [16]       |

# **Experimental Protocols**

Protocol 1: Fabrication of a Vertical Mini-LED with a Textured n-AlGaInP Surface

This protocol outlines the key steps for creating a vertical AlGaInP LED on a Si carrier with a roughened surface for enhanced light extraction, based on the process described in literature[1].

#### Troubleshooting & Optimization

- Wafer Pretreatment & Blocking Layer: Start with a standard AlGaInP LED wafer. Deposit a 300-nm-thick SiO<sub>2</sub> layer via plasma-enhanced chemical vapor deposition (PECVD) to serve as a current blocking layer[1].

- P-Contact Formation: Use wet etching to form cylindrical holes in the SiO<sub>2</sub> layer for p-contact. Evaporate a highly reflective p-electrode (e.g., Ag-based) followed by a bonding metal layer[1].

- Wafer Bonding & Substrate Removal: Bond the LED wafer to a Si carrier wafer. Remove the

original GaAs substrate and the GaInP etching stop layer using appropriate chemical etching

processes[1][21].

- N-Contact & Mesa Definition: Evaporate the n-electrode. Define the individual mini-LED mesa structures through etching[1].

- Surface Texturing: Use a wet etching solution (e.g., 3 NH<sub>4</sub>F: 2 CH₃COOH: 6 H₂O) to create a

porous, roughened surface on the exposed n-AlGaInP layer. The etching time is a critical

parameter that controls pore density[1].

- Passivation & Finishing: Deposit a SiNx passivation layer. Thin the Si carrier substrate and deposit the final Ti/Au contacts on the backside[1].

Protocol 2: Fabrication of Antireflective Subwavelength Structures (SWS)

This protocol describes a method for creating tapered, antireflective nanostructures on the LED surface using a self-assembled metal mask[4].

- Metal Deposition: Deposit a thin layer of metal (e.g., Ag) onto the GaP window layer of the AlGaInP LED.

- Nanoparticle Formation: Perform a thermal dewetting process (annealing) to cause the thin metal film to agglomerate into a pattern of isolated nanoparticles.

- Dry Etching: Use the Ag nanoparticles as an etch mask in a dry etching process (e.g., inductively coupled plasma reactive-ion etching). The etching process transfers the nanoparticle pattern into the GaP layer. The non-uniform erosion of the mask during etching results in the formation of tapered pillars.

Mask Removal: Remove any residual Ag mask material using a suitable wet etch. The

resulting tapered SWS on the GaP surface acts as an antireflective layer, improving light

extraction[4].

#### **Visualizations**

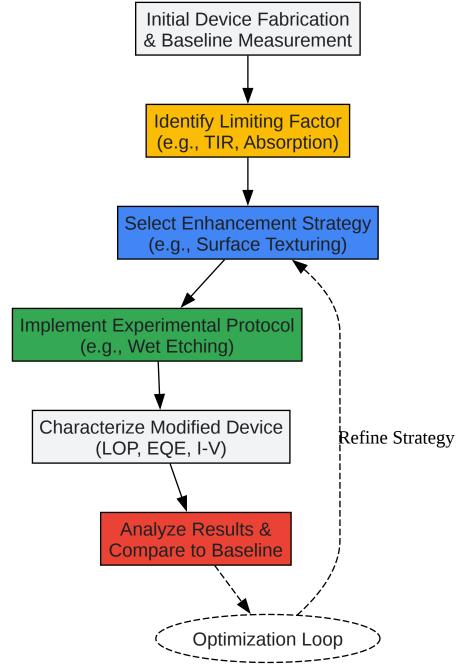

Fig. 1: General Workflow for LEE Enhancement

Click to download full resolution via product page

Caption: General workflow for improving AlGaInP LED light extraction efficiency.

Fig. 2: Mechanism of Surface Texturing

Click to download full resolution via product page

Caption: Total Internal Reflection (TIR) in planar vs. textured LEDs.

Fig. 3: Current Spreading vs. Current Crowding

Click to download full resolution via product page

Caption: Role of a Current Blocking Layer (CBL) in mitigating current crowding.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. Improvement of light extraction efficiency in AlGaInP-based vertical miniaturized-lightemitting diodes via surface texturing [opg.optica.org]

- 2. Improvement of light extraction efficiency in AlGaInP-based vertical miniaturized-lightemitting diodes via surface texturing - PubMed [pubmed.ncbi.nlm.nih.gov]

- 3. IEEE Xplore Full-Text PDF: [ieeexplore.ieee.org]

### Troubleshooting & Optimization

- 4. OPG [opg.optica.org]

- 5. OPG [opg.optica.org]

- 6. researchgate.net [researchgate.net]

- 7. jos.ac.cn [jos.ac.cn]

- 8. pubs.aip.org [pubs.aip.org]

- 9. OPG [opg.optica.org]

- 10. Enhanced light extraction from AlGaInP-based red light-emitting diodes with photonic crystals PubMed [pubmed.ncbi.nlm.nih.gov]

- 11. researchgate.net [researchgate.net]

- 12. Thin-film vertical-type AlGaInP LEDs fabricated by epitaxial lift-off process via the patterned design of Cu substrate PubMed [pubmed.ncbi.nlm.nih.gov]

- 13. researchgate.net [researchgate.net]

- 14. pubs.aip.org [pubs.aip.org]

- 15. pubs.aip.org [pubs.aip.org]

- 16. Schottky-contact intrinsic current blocking layer for high efficiency AlGaInP-based red mini-LEDs [opg.optica.org]

- 17. High-efficiency AlGaInP thin-film LEDs using surface-texturing and waferbonding with conductive epoxy | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 18. compoundsemiconductor.net [compoundsemiconductor.net]

- 19. researchgate.net [researchgate.net]

- 20. Increasing the extraction efficiency of AlGaInP LEDs via n-side surface roughening |

IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 21. OPG [opg.optica.org]

- 22. Improved Light Extraction Efficiency in AlGaInP Light-Emitting Diodes by Applying a

Periodic Texture on the Surface | IEEE Journals & Magazine | IEEE Xplore

[ieeexplore.ieee.org]

- 23. Improvement of LED extraction efficiency with antireflection coating | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- To cite this document: BenchChem. [improving light extraction efficiency in AlGaInP LEDs]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b14657816#improving-light-extraction-efficiency-in-algainp-leds]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com