# identifying and reducing dislocations in gallium arsenide on silicon

Author: BenchChem Technical Support Team. Date: December 2025

# Technical Support Center: Gallium Arsenide on Silicon Heteroepitaxy

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working on the heteroepitaxial growth of **Gallium Arsenide** (GaAs) on Silicon (Si) substrates. The focus is on identifying and reducing dislocations, a critical challenge in this materials system.

## Frequently Asked Questions (FAQs)

Q1: What are the primary challenges when growing **Gallium Arsenide** (GaAs) on a Silicon (Si) substrate?

A1: The direct epitaxial growth of GaAs on Si substrates presents three main challenges that lead to the formation of defects:

- Large Lattice Mismatch: There is a significant difference in the lattice constants of GaAs and Si (~4.1%), which induces misfit dislocations at the interface to relieve strain.[1][2] These dislocations can propagate into the epitaxial layer as threading dislocations.

- Thermal Expansion Mismatch: The thermal expansion coefficients of GaAs and Si are different. This mismatch results in large thermal stresses when the wafer is cooled down from the high growth temperatures, which can generate additional dislocations.[1][3]

Polar-on-Nonpolar Growth: Growing a polar semiconductor like GaAs on a nonpolar substrate like Si can lead to the formation of anti-phase boundaries (APBs), which are planar defects.[1]

Q2: How can I identify and quantify dislocations in my GaAs on Si films?

A2: Several characterization techniques are available to identify and quantify dislocations:

- Transmission Electron Microscopy (TEM): TEM is a powerful technique for directly imaging and characterizing dislocations.[4][5] Both cross-sectional and plan-view TEM can be used to observe the dislocation distribution and estimate their density.[6]

- Electron Channeling Contrast Imaging (ECCI): ECCI is a non-destructive technique performed in a scanning electron microscope (SEM) that allows for the rapid and large-area characterization of threading dislocations.[2][7][8][9]

- Etch Pit Density (EPD): This method involves chemical etching (e.g., with molten KOH) to reveal dislocation-related etch pits on the GaAs surface.[3] The density of these pits can then be counted using an optical or scanning electron microscope.

- X-ray Diffraction (XRD): High-resolution XRD rocking curve measurements can provide

information about the crystalline quality of the epilayer. A broader full width at half maximum

(FWHM) of the rocking curve is often correlated with a higher dislocation density.

## **Troubleshooting Guides**

# Issue 1: High Threading Dislocation Density (TDD) in the GaAs Epilayer

High TDD is a common problem that degrades the performance of devices fabricated on the GaAs/Si platform. The following table summarizes common causes and potential solutions.

| Potential Cause                   | Troubleshooting Steps & Solutions                                                                                                                                                                                                 |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Sub-optimal Growth Initiation     | Ensure proper Si substrate preparation, including cleaning and pre-heating to achieve a reconstructed surface before growth.[10] A low-temperature GaAs nucleation layer is often used to accommodate the initial mismatch.[2][7] |  |

| Ineffective Dislocation Filtering | Implement one or more dislocation reduction techniques such as Thermal Cycle Annealing (TCA), Strained-Layer Superlattices (SLS), or a combination of both.                                                                       |  |

| Incorrect Growth Parameters       | Optimize growth parameters such as temperature, growth rate, and V/III ratio for your specific growth system (MBE or MOCVD).                                                                                                      |  |

### Issue 2: Poor Surface Morphology of the GaAs Film

A rough surface can negatively impact subsequent processing steps and device performance.

| Potential Cause                          | Troubleshooting Steps & Solutions                                                                                                                                                        |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Three-Dimensional Island Growth          | Optimize the initial nucleation conditions to promote two-dimensional growth. This can involve adjusting the temperature and using techniques like migration-enhanced epitaxy (MEE).[11] |

| Presence of Anti-Phase Boundaries (APBs) | Use off-axis Si substrates (miscut towards a <110> direction) to promote double-atomic steps on the surface, which can suppress APB formation.[6]                                        |

| High Dislocation Density                 | High TDD can contribute to surface roughness. Implementing dislocation reduction techniques will also improve surface morphology.                                                        |

### **Experimental Protocols**

## Protocol 1: Dislocation Reduction using Thermal Cycle Annealing (TCA)

Thermal cycle annealing is an effective in-situ technique to reduce threading dislocation density. The process involves cycling the substrate temperature, which enhances dislocation movement and annihilation.[3][12]

#### Methodology:

- Grow an initial GaAs buffer layer (e.g., 1-2  $\mu$ m) on the Si substrate at the standard growth temperature (e.g., 600-700 °C).

- · Interrupt the growth and initiate the thermal cycling.

- Ramp the substrate temperature up to a high annealing temperature (e.g., 700-850 °C) and hold for a few minutes.

- Ramp the temperature down to a lower temperature (e.g., 300-400 °C) and hold for a few minutes.

- Repeat this cycle multiple times (e.g., 4-10 cycles).[7]

- After the final cycle, stabilize the temperature at the growth temperature and continue growing the final GaAs layer.

# Protocol 2: Dislocation Filtering with Strained-Layer Superlattices (SLS)

Strained-layer superlattices act as dislocation filters by bending and terminating threading dislocations at the strained interfaces.[13][14][15]

#### Methodology:

After growing an initial GaAs buffer layer, deposit the strained-layer superlattice.

- A common SLS structure consists of alternating layers of InGaAs and GaAs (e.g., 10 periods of 10 nm In<sub>0.1</sub>Ga<sub>0.9</sub>As / 10 nm GaAs).[7]

- The indium content and layer thickness are critical parameters that determine the strain and effectiveness of the filter. These should be kept below the critical thickness for dislocation generation within the SLS itself.

- Grow the SLS at a relatively low temperature (e.g., 450-550 °C) to effectively bend dislocations.

- After the SLS, grow the final GaAs top layer at the standard growth temperature.

#### **Data Presentation**

Table 1: Comparison of Dislocation Reduction Techniques

| Technique                             | Typical TDD Reduction           | Key Parameters                                                                                   |

|---------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------|

| Thermal Cycle Annealing (TCA)         | 1-2 orders of magnitude         | Annealing temperature range, number of cycles, ramp rates. [3][12]                               |

| Strained-Layer Superlattices (SLS)    | ~1 order of magnitude           | Material system (e.g.,<br>InGaAs/GaAs), layer<br>thickness, number of periods,<br>strain.[6][13] |

| Aspect Ratio Trapping (ART)           | Can achieve defect-free regions | Trench aspect ratio (height/width), trench orientation.[16][17][18]                              |

| Combined Approaches (e.g., TCA + SLS) | >2 orders of magnitude          | Combination of the parameters listed above.[7][19]                                               |

### **Visualizations**

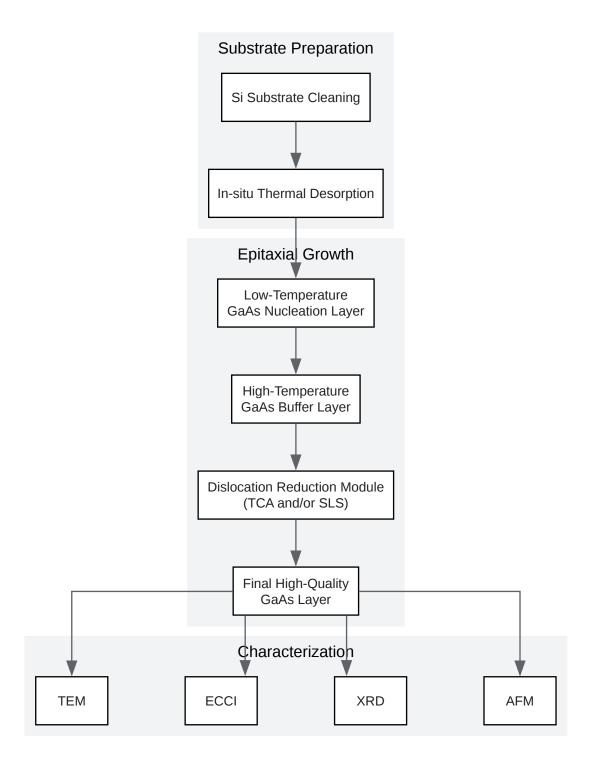

Click to download full resolution via product page

Caption: Experimental workflow for GaAs on Si growth.

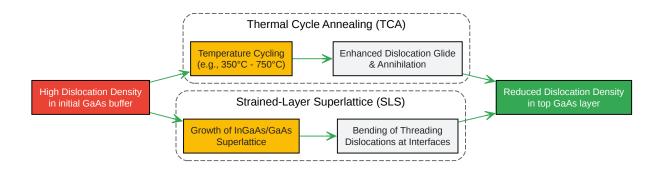

Click to download full resolution via product page

Caption: Dislocation reduction pathways in GaAs on Si.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. The Growth of GaAs on Si by Molecular Beam Epitaxy | MRS Online Proceedings Library (OPL) | Cambridge Core [cambridge.org]

- 2. semiconductor-today.com [semiconductor-today.com]

- 3. pubs.aip.org [pubs.aip.org]

- 4. files.core.ac.uk [files.core.ac.uk]

- 5. researchgate.net [researchgate.net]

- 6. researchgate.net [researchgate.net]

- 7. Reducing dislocations in gallium arsenide on silicon templates [semiconductor-today.com]

- 8. researchgate.net [researchgate.net]

- 9. researchgate.net [researchgate.net]

- 10. pubs.aip.org [pubs.aip.org]

- 11. ee.stanford.edu [ee.stanford.edu]

- 12. pubs.aip.org [pubs.aip.org]

- 13. pubs.aip.org [pubs.aip.org]

- 14. pubs.aip.org [pubs.aip.org]

- 15. pubs.aip.org [pubs.aip.org]

- 16. pubs.aip.org [pubs.aip.org]

- 17. Defect reduction of GaAs/Si epitaxy by aspect ratio trapping [ouci.dntb.gov.ua]

- 18. pubs.aip.org [pubs.aip.org]

- 19. Reduced Dislocation of GaAs Layer Grown on Ge-Buffered Si (001) Substrate Using Dislocation Filter Layers for an O-Band InAs/GaAs Quantum Dot Narrow-Ridge Laser - PMC [pmc.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [identifying and reducing dislocations in gallium arsenide on silicon]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b074776#identifying-and-reducing-dislocations-in-gallium-arsenide-on-silicon]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com