# how to decrease resistivity in InAIN films for optoelectronics

Author: BenchChem Technical Support Team. Date: November 2025

# Technical Support Center: InAlN Films for Optoelectronics

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to help researchers, scientists, and engineers address challenges related to decreasing the electrical resistivity of Indium Aluminum Nitride (InAIN) films for optoelectronic applications.

## Frequently Asked Questions (FAQs)

Q1: Why is low resistivity in InAIN films important for optoelectronics?

A1: Low resistivity is crucial for optoelectronic devices like LEDs, laser diodes, and high-electron-mobility transistors (HEMTs) to ensure efficient current injection and minimize power loss due to resistive heating. For transparent conductive layers, low resistivity is required to maintain high optical transparency and good electrical conductivity. In HEMTs, low resistance in the access regions (source and drain) is vital for achieving high-frequency performance and high power output.[1]

Q2: What are the primary factors that determine the resistivity of an InAIN film?

A2: The resistivity ( $\rho$ ) is determined by the carrier concentration (n) and the carrier mobility ( $\mu$ ), according to the formula  $\rho = 1/(q * n * \mu)$ , where q is the elementary charge. Therefore, the primary factors are:

- Carrier Concentration: The number of free electrons or holes, which can be increased through intentional doping (e.g., with Silicon for n-type or Magnesium for p-type).[2][3]

- Carrier Mobility: The ease with which carriers move through the material. Mobility is limited by scattering from various sources, including crystal defects (dislocations), impurities, lattice vibrations (phonons), and alloy scattering.[4][5]

- Contact Resistance: In a device structure, the resistance at the metal-semiconductor interface can be a significant contributor to the total measured resistance.[6]

Q3: What is a 2DEG and how does it help lower resistance in InAIN-based structures?

A3: A 2DEG, or two-dimensional electron gas, is a high-density sheet of electrons confined at the interface of a heterostructure, such as InAlN/GaN.[4] Strong spontaneous and piezoelectric polarization effects in the InAlN/GaN system create a deep quantum well at the interface, accumulating a high concentration of electrons without intentional doping.[7][8] This high-density channel of electrons provides a very low-resistance path for current, resulting in a low sheet resistance, which is essential for HEMT applications.[9]

## **Troubleshooting Guide: High Film Resistivity**

This guide addresses common issues encountered when attempting to achieve low resistivity in InAIN films.

## Issue 1: My intentionally doped InAIN film has high resistivity.

Q: I am trying to create a conductive n-type InAIN film using Silicon (Si) doping, but the resistivity is too high. What could be wrong?

A: High resistivity in Si-doped InAlN often stems from compensation effects or poor crystal quality. Consider the following:

• Insufficient Dopant Activation: Silicon acts as a shallow donor in GaN, but its activation energy increases in Al-rich AlGaN alloys.[10] In InAlN, a sufficiently high Si concentration is necessary to achieve high carrier concentrations.

### Troubleshooting & Optimization

- Self-Compensation: At very high Si doping levels, the formation of compensating defects, such as cation vacancies (V-III), can trap free electrons and limit the achievable conductivity.

[10]

- Oxygen Contamination: Unintentionally incorporated oxygen can act as a donor but can also be part of compensating defect complexes. High oxygen levels are often associated with high dislocation densities.[11]

- Poor Crystal Quality: High dislocation densities act as scattering centers and carrier traps, which reduces electron mobility and free carrier concentration, thereby increasing resistivity.

[12]

#### Solutions:

- Optimize SiH<sub>4</sub> Flow: Systematically vary the silane (SiH<sub>4</sub>) flow rate during MOCVD growth to find the optimal doping concentration that maximizes carrier concentration before selfcompensation becomes dominant.

- Optimize Growth Temperature: Growth temperature affects dopant incorporation, impurity levels (like oxygen), and crystal quality. Higher temperatures can improve crystal quality but may also enhance the formation of compensating defects.[13][14]

- Improve Buffer Layers: Use high-quality buffer layers (e.g., GaN on sapphire) to reduce the dislocation density in the subsequent InAIN film.

Q: I am attempting to achieve p-type conductivity in InAIN with Magnesium (Mg) doping, but the film is highly resistive or remains n-type. What is the issue?

A: Achieving p-type conductivity in Al-rich nitrides is notoriously difficult. The primary challenges are:

- High Mg Acceptor Activation Energy: The energy required to create a free hole from a Mg acceptor is high (~0.25 eV in GaN and higher in Al-rich alloys), meaning only a small fraction of Mg atoms are ionized at room temperature.[15]

- Dopant Compensation: Unintentional donors (like oxygen or nitrogen vacancies) and Mgrelated defects can compensate for the Mg acceptors, reducing the net hole concentration.

#### [11][16]

- Hydrogen Passivation: During MOCVD growth, hydrogen can form complexes with Mg acceptors, passivating them. A post-growth thermal annealing step is required to activate the Mg dopants.[16]

- Phase Separation: High Mg flow rates can degrade the crystal quality and even lead to phase separation in the InAIN film.[15]

#### Solutions:

- Post-Growth Annealing: Perform rapid thermal annealing (RTA) in an N<sub>2</sub> ambient after growth to break the Mg-H bonds and activate the acceptors.

- Optimize Cp<sub>2</sub>Mg Flow: Carefully control the bis(cyclopentadienyl)magnesium (Cp<sub>2</sub>Mg) precursor flow. Too little will not provide enough acceptors, while too much can degrade material quality.[15][16] A net acceptor concentration of 5 x 10<sup>18</sup> cm<sup>-3</sup> has been achieved with a Mg concentration of ~2 x 10<sup>19</sup> cm<sup>-3</sup>.[16]

- Reduce Background Impurities: Optimize growth conditions to minimize the concentration of unintentional n-type dopants like oxygen.

## Issue 2: The sheet resistance of my InAIN/GaN heterostructure is too high.

Q: My InAIN/GaN HEMT structure shows high sheet resistance. How can I improve the 2DEG conductivity?

A: High sheet resistance in an InAIN/GaN structure is due to either low 2DEG density or low electron mobility.

Suboptimal InAIN Barrier: The In content and thickness of the InAIN barrier are critical. An indium content of ~17-18% is needed to be lattice-matched to GaN, which minimizes defects.[4] The barrier must be thick enough to induce a strong 2DEG but thin enough to avoid relaxation and cracking.

- Interface Roughness and Alloy Scattering: A rough InAIN/GaN interface or compositional inhomogeneities in the InAIN alloy can severely scatter electrons, reducing mobility.[5]

- Polarization Coulomb Field (PCF) Scattering: Polarization charges in the InAlN barrier can create a scattering field that reduces electron mobility.[4]

#### Solutions:

- Insert an AlN Interlayer: Growing a thin (~1 nm) AlN interlayer between the InAlN barrier and the GaN channel can reduce alloy scattering and improve the interface quality, significantly boosting electron mobility.[8][9]

- Optimize Growth Conditions: Fine-tune the MOCVD growth temperature and V/III ratio for the InAIN barrier to minimize alloy clustering and improve compositional uniformity.[5]

- Apply Surface Treatments: Post-growth treatments can modify the surface charge and reduce PCF scattering. For instance, treatment with bis(trifluoromethane) sulfonamide (TFSI) solution has been shown to neutralize surface polarization charges, increasing 2DEG mobility from 1180 to 1500 cm²/Vs.[4]

Click to download full resolution via product page

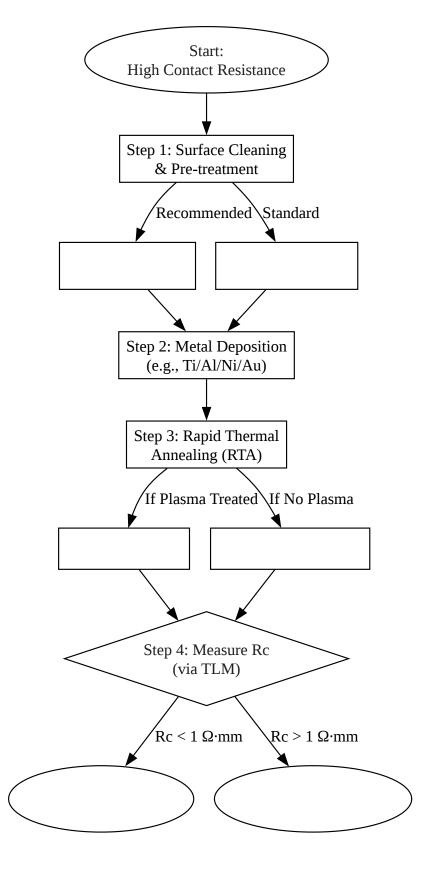

## **Troubleshooting Guide: High Contact Resistance**

Even with a low-resistivity film, poor electrical contacts can dominate the overall device resistance.

## Issue 3: My ohmic contacts to InAIN have high resistance.

Q: I am fabricating contacts on an InAIN/GaN structure, but the contact resistance is very high, or the contact is not ohmic. What are the best practices?

A: Forming low-resistance ohmic contacts to the wide-bandgap InAlN surface is challenging. High annealing temperatures required for standard Ti/Al-based contacts can damage the

#### sensitive InAIN surface.

- Surface Contamination: Oxides and organic residues on the InAIN surface before metal deposition can inhibit the formation of a good ohmic contact.

- Insufficient Annealing: The annealing temperature and time are critical for the metal stack to react with the semiconductor and form a low-resistance contact. Standard recipes for AlGaN/GaN may not be optimal for InAlN/GaN.

- Barrier to Tunneling: The InAIN barrier itself can impede current flow from the metal to the 2DEG channel.

#### Solutions:

- Surface Pre-treatment: Use a plasma treatment before metallization. A SiCl<sub>4</sub> reactive ion etching (RIE) treatment has been shown to reduce carbon impurities and enable the formation of good ohmic contacts with an annealing temperature as low as 600°C.[17]

- Optimize Metal Stack and Annealing: A common metal stack is Ti/Al/Ni/Au. The annealing should be performed using RTA for precise temperature control. While contacts on untreated surfaces may require ~800°C, SiCl<sub>4</sub> pre-treatment can lower this to 600°C, achieving a contact resistance of 0.7 Ω·mm.[17]

- Regrown Ohmic Contacts: This is a highly effective but more complex method. It involves etching the source/drain regions and regrowing a heavily doped n+-GaN or n+-InGaN layer using MOCVD or MBE.[18][19] This creates a low-resistance path to the 2DEG and can achieve extremely low contact resistances (e.g., 0.102 Ω·mm) without high-temperature alloy annealing.[6][19]

Click to download full resolution via product page

## **Quantitative Data Summary**

Table 1: Effect of Doping on InAIN/AIN Resistivity

| Dopant | Doping<br>Method            | Carrier<br>Concentrati<br>on (cm <sup>-3</sup> ) | Mobility<br>(cm²/Vs)                           | Resistivity<br>(Ω·cm) | Reference |

|--------|-----------------------------|--------------------------------------------------|------------------------------------------------|-----------------------|-----------|

| Si     | MOCVD (on<br>AIN)           | 4 x 10 <sup>14</sup>                             | 30                                             | 530                   | [20]      |

| Mg     | MOCVD (N-<br>polar In-rich) | ~10 <sup>19</sup> (n-type)                       | ~0.3 (at 80<br>nmol/min<br>Cp <sub>2</sub> Mg) | ~0.5                  | [15][21]  |

| Mg | MOVPE (Lattice-matched) | 5.3 x 1018 (p-type, NA-ND) | - | - |[16] |

Table 2: Electrical Properties of InAIN/GaN Heterostructures

| In Content<br>(%) | Interlayer             | 2DEG<br>Density<br>(cm <sup>-2</sup> ) | Mobility<br>(cm²/Vs) | Sheet<br>Resistance<br>(Ω/sq) | Reference |

|-------------------|------------------------|----------------------------------------|----------------------|-------------------------------|-----------|

| 17                | None                   | -                                      | 1180                 | 465<br>(derived)              | [4]       |

| 17                | None (TFSI<br>Treated) | -                                      | 1500                 | 366 (derived)                 | [4]       |

| 18                | ~1 nm AlN              | 0.96 x 10 <sup>13</sup>                | 17600 (at<br>77K)    | -                             | [9]       |

| 17                | None                   | 2.42 x 10 <sup>13</sup>                | 120                  | 2135<br>(derived)             | [9]       |

| 17 (AllnGaN) | 1 nm AlN | 1.09 x 10 $^{13}$  | 2090 | 274 |[5] |

Table 3: Ohmic Contact Resistance (Rc) on InAIN/GaN

| Metallization        | Surface<br>Treatment | Annealing | Rc (Ω·mm) | Reference |

|----------------------|----------------------|-----------|-----------|-----------|

| Ti/Al/Ni/Au          | None                 | 800°C     | 1.7       | [17]      |

| Ti/Al/Ni/Au          | SiCl4 RIE            | 600°C     | 0.7       | [17]      |

| n+-GaN<br>Regrowth   | MBE Regrowth         | -         | 0.4       | [18]      |

| n+-InGaN<br>Regrowth | MOCVD<br>Regrowth    | -         | 0.102     | [19]      |

| Ti/Au (on n+-GaN) | MOCVD Regrowth | 850°C | 0.06 |[6] |

## **Experimental Protocols**

### Protocol 1: MOCVD Growth and Si-Doping of n-type AIN

This protocol is adapted from methodologies for growing conductive AIN, which are foundational for InAIN.

- Substrate Preparation: Use c-plane sapphire substrates. Perform a thermal cleaning step in the MOCVD reactor at ~1100°C in an H<sub>2</sub> ambient.

- Buffer Layer Growth: Grow a high-quality, undoped AIN buffer layer (~250 nm) to improve crystal quality. Precursors: Trimethylaluminum (TMAI) and ammonia (NH₃). Carrier gas: H₂.

Growth Temperature: ~1190°C. Reactor Pressure: ~35 mbar.[20]

- Si-Doped Layer Growth: Introduce silane (SiH<sub>4</sub>) into the reactor to begin the doped layer growth (~350 nm).

- Doping Concentration Control: Vary the SiH<sub>4</sub> molar flow rate to achieve the desired silicon concentration. A Si concentration of 1.5 x 10<sup>18</sup> cm<sup>-3</sup> has been shown to yield fair n-type conductivity.[20]

- Cooldown: After growth, cool the wafer down under an NH₃ and N₂ ambient to protect the film surface.

## Protocol 2: Achieving p-type Conduction in InAlN via Mg Doping

This protocol is based on methods for p-doping lattice-matched AlInN on GaN templates.

- Growth Setup: Grow on a GaN-on-sapphire template using a MOVPE system.

- Precursors: Use TMAI, Trimethylindium (TMI), and NH₃ for the AlInN layer. Use Bis-cyclopentadienylmagnesium (Cp₂Mg) as the p-type dopant source. Carrier gas: N₂.[16]

- Doping Control: Control the Mg concentration by adjusting the Cp<sub>2</sub>Mg/(TMAI + TMI) molar ratio. A ratio of ~0.002 can achieve a [Mg] of ~2 x 10<sup>19</sup> cm<sup>-3</sup>, resulting in a net acceptor concentration of ~5 x 10<sup>18</sup> cm<sup>-3</sup>.[16]

- Growth Termination: Complete the growth of the Mg-doped AllnN layer (e.g., 100 nm thick).

- Post-Growth Activation Anneal: After unloading from the reactor, perform RTA in an N₂

atmosphere. This step is critical to drive out hydrogen and activate the Mg acceptors. Typical

conditions for GaN are ~700-800°C for several minutes; conditions may need to be

optimized for InAIN to prevent surface degradation.

## Protocol 3: Fabrication of Low-Resistance Ohmic Contacts with SiCl<sub>4</sub> Pre-treatment

- Photolithography: Define the source and drain contact areas using standard photolithography.

- Surface Cleaning: Perform a standard solvent clean (acetone, IPA) followed by a dip in dilute HCl to remove native oxides.

- Plasma Treatment: Immediately load the sample into a Reactive Ion Etching (RIE) system.

Perform a brief etch using SiCl<sub>4</sub> plasma. This step removes surface contaminants and prepares the surface for metallization.[17]

- Metal Deposition: Without breaking vacuum if possible, or by quickly transferring the sample, deposit the metal stack (e.g., Ti/Al/Ni/Au with thicknesses of 20/100/20/50 nm) using electron-beam evaporation.

- Lift-off: Perform lift-off in a suitable solvent to remove the photoresist and unwanted metal.

- Rapid Thermal Annealing (RTA): Anneal the sample in an N₂ atmosphere. For SiCl₄-treated surfaces, an optimized temperature is around 600°C for 30-60 seconds.[17]

- Characterization: Measure the contact resistance using the Transmission Line Method (TLM).

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. pubs.aip.org [pubs.aip.org]

- 2. m.youtube.com [m.youtube.com]

- 3. quora.com [quora.com]

- 4. Improved Electrical Performance of InAIN/GaN High Electron Mobility Transistors with Post Bis(trifluoromethane) Sulfonamide Treatment [mdpi.com]

- 5. pubs.aip.org [pubs.aip.org]

- 6. pubs.aip.org [pubs.aip.org]

- 7. researchgate.net [researchgate.net]

- 8. Theoretical Study of InAlN/GaN High Electron Mobility Transistor (HEMT) with a Polarization-Graded AlGaN Back-Barrier Layer [mdpi.com]

- 9. pubs.aip.org [pubs.aip.org]

- 10. depts.ttu.edu [depts.ttu.edu]

- 11. bohrium.com [bohrium.com]

- 12. researchgate.net [researchgate.net]

- 13. researchgate.net [researchgate.net]

- 14. Electrical activity at the AlN/Si Interface: identifying the main origin of propagation losses in GaN-on-Si devices at microwave frequencies PMC [pmc.ncbi.nlm.nih.gov]

- 15. Mg Doping of N-Polar, In-Rich InAIN PMC [pmc.ncbi.nlm.nih.gov]

- 16. pubs.aip.org [pubs.aip.org]

- 17. researchgate.net [researchgate.net]

- 18. djena.engineering.cornell.edu [djena.engineering.cornell.edu]

- 19. HTTP500 内部服务器出错 [cpb.iphy.ac.cn]

- 20. uni-ulm.de [uni-ulm.de]

- 21. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [how to decrease resistivity in InAIN films for optoelectronics]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b15444497#how-to-decrease-resistivity-in-inaln-filmsfor-optoelectronics]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com