# fabrication process of gallium arsenide-based photodetectors

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                  |           |

|----------------------|------------------|-----------|

| Compound Name:       | Gallium arsenide |           |

| Cat. No.:            | B074776          | Get Quote |

An Application Note and Protocol for the Fabrication of **Gallium Arsenide** (GaAs)-Based Photodetectors

Audience: Researchers, scientists, and drug development professionals.

Objective: This document provides a detailed, step-by-step protocol for the fabrication of **Gallium Arsenide** (GaAs) p-i-n junction photodetectors. The process outlined covers epitaxial growth, device patterning, metallization, passivation, and characterization.

## Introduction

Gallium Arsenide (GaAs) is a direct bandgap semiconductor with high electron mobility, making it an excellent material for high-speed optoelectronic devices, including photodetectors. [1] These devices are crucial components in various applications, from optical fiber communications to advanced sensing systems.[2] This protocol details a standard fabrication process for creating a mesa-structured GaAs p-i-n photodiode. The workflow begins with an epitaxially grown wafer and proceeds through photolithography, etching, contact formation, and final device passivation.

## **Materials and Equipment**

A comprehensive list of materials and equipment required for the fabrication process is detailed in the table below.

| Category          | ategory Item                                                                                                                                                                                                                  |                                                                                           |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| Substrate         | GaAs Wafer                                                                                                                                                                                                                    | 3-inch or 4-inch diameter, semi-insulating (100) orientation with p-i-n epitaxial layers. |  |

| Chemicals         | Photoresist (Positive)                                                                                                                                                                                                        | e.g., AZ 5214                                                                             |  |

| Developer         | Tetramethylammonium hydroxide (TMAH)-based                                                                                                                                                                                    |                                                                                           |  |

| Solvents          | Acetone, Isopropanol (IPA),<br>Methanol (all electronic grade)                                                                                                                                                                | <del>-</del>                                                                              |  |

| Adhesion Promoter | Hexamethyldisilazane (HMDS)                                                                                                                                                                                                   |                                                                                           |  |

| Wet Etchants      | Citric Acid (C <sub>6</sub> H <sub>8</sub> O <sub>7</sub> ), Hydrogen<br>Peroxide (H <sub>2</sub> O <sub>2</sub> ), Phosphoric<br>Acid (H <sub>3</sub> PO <sub>4</sub> ), Hydrochloric<br>Acid (HCl), Deionized (DI)<br>Water |                                                                                           |  |

| Metal Deposition  | Titanium (Ti), Platinum (Pt),<br>Gold (Au), Germanium (Ge),<br>Nickel (Ni)                                                                                                                                                    | _                                                                                         |  |

| Equipment         | Epitaxial Growth System                                                                                                                                                                                                       | Metal-Organic Chemical Vapor Deposition (MOCVD) or Molecular Beam Epitaxy (MBE)           |  |

| Photolithography  | Spin Coater, Hot Plate, Mask<br>Aligner                                                                                                                                                                                       |                                                                                           |  |

| Etching System    | Reactive Ion Etching (RIE) or<br>Inductively Coupled Plasma<br>(ICP-RIE) System, Wet<br>Etching Bench                                                                                                                         |                                                                                           |  |

| Deposition System | Electron Beam Evaporator or<br>Sputtering System                                                                                                                                                                              | -<br>-                                                                                    |  |

| Annealing System | Rapid Thermal Annealing /stem (RTA) System                                             |  |

|------------------|----------------------------------------------------------------------------------------|--|

| Passivation      | Plasma-Enhanced Chemical Vapor Deposition (PECVD) System                               |  |

| Characterization | Probe Station with Semiconductor Parameter Analyzer, Optical Power Meter, Laser Source |  |

## **Experimental Protocols**

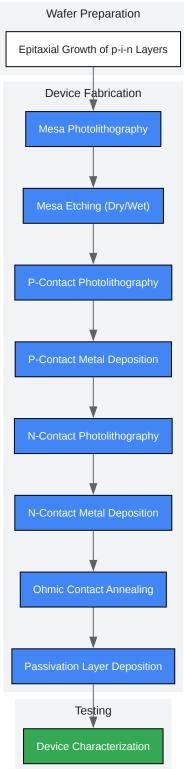

The overall fabrication workflow is depicted in the diagram below, followed by detailed protocols for each major step.

Overall Fabrication Workflow for GaAs Photodetector

Click to download full resolution via product page

**Caption:** High-level workflow from epitaxial growth to final device characterization.

## **Epitaxial Layer Growth**

The device performance is critically dependent on the quality of the epitaxially grown layers.[3] The process typically uses MOCVD or MBE systems to grow a specific heterostructure on a semi-insulating GaAs substrate.[4] A representative p-i-n structure is detailed below.

Table 1: Representative p-i-n Epitaxial Structure

| Layer       | Material                                 | Thickness      | Doping Type            | Doping Conc.<br>(cm <sup>-3</sup> ) |

|-------------|------------------------------------------|----------------|------------------------|-------------------------------------|

| 5 (Top)     | p+-GaAs                                  | 200 nm         | p-type (Carbon)        | > 1 x 10 <sup>19</sup>              |

| 4           | p-Al <sub>0.3</sub> Ga <sub>0.7</sub> As | 50 nm          | p-type (Carbon)        | ~ 5 x 10 <sup>17</sup>              |

| 3           | i-GaAs<br>(Absorber)                     | 1000 - 2000 nm | Intrinsic<br>(undoped) | < 1 x 10 <sup>15</sup>              |

| 2           | n+-GaAs                                  | 600 nm         | n-type (Silicon)       | > 2 x 10 <sup>18</sup>              |

| 1 (Buffer)  | AlAs/GaAs SL                             | 100 nm         | -                      | -                                   |

| Substrate   | SI-GaAs                                  | 500 μm         | Semi-Insulating        | -                                   |

| Note: Laver |                                          |                |                        |                                     |

Note: Layer structure adapted from references.[1][5]

#### Protocol for MOCVD Growth:

- Load a (100) semi-insulating GaAs substrate into the MOCVD reactor.[7]

- Perform thermal cleaning by heating the substrate under an Arsine (AsH₃) atmosphere to remove the native oxide layer.

- Grow the AlAs/GaAs superlattice (SL) buffer layer, followed by the n+-GaAs contact layer at a growth temperature of approximately 720°C.[5]

- Lower the temperature to around 620°C for the growth of the intrinsic GaAs absorption layer and the p-type layers to minimize dopant diffusion.[5]

- Use Trimethylgallium (TMGa) and Trimethylaluminum (TMAl) as Group III precursors and AsH₃ as the Group V precursor. Use Silane (SiH₄) for n-type doping and Carbon Tetrachloride (CCl₄) for p-type doping.[7]

#### **Mesa Definition**

To isolate individual devices, a mesa structure is created by etching through the p-type and intrinsic layers down to the n-type contact layer.

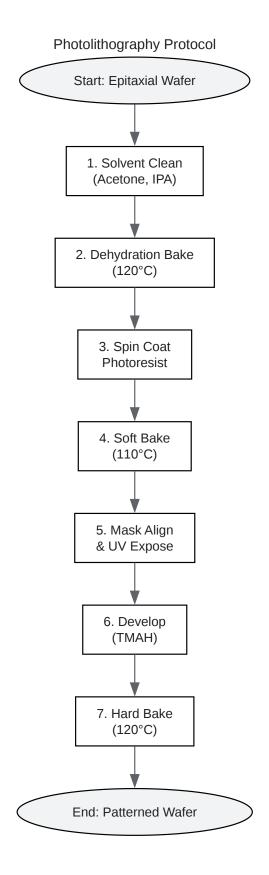

#### 3.2.1 Mesa Photolithography Protocol

- Substrate Cleaning: Clean the wafer by sonicating sequentially in acetone, methanol, and isopropanol for 5 minutes each, followed by a DI water rinse and N<sub>2</sub> blow dry.[8]

- Dehydration Bake: Bake the wafer on a hotplate at 120°C for 10 minutes to remove residual moisture.[9]

- Photoresist Coating: Apply a positive photoresist using a spin coater to achieve a uniform thickness of ~1.5 μm.[9][10]

- Soft Bake: Bake the wafer on a hotplate at 90-110°C for 60-90 seconds to drive off solvents from the photoresist.[10]

- Exposure: Place the wafer in a mask aligner, align the mesa mask, and expose the photoresist to UV light.

- Development: Develop the pattern by immersing the wafer in a TMAH-based developer for approximately 60 seconds. A double-puddle methodology can be used for improved feature resolution.[10] Rinse thoroughly with DI water and blow dry with N<sub>2</sub>.

- Hard Bake: Post-bake the wafer at 120°C for 2-5 minutes to further harden the resist, improving its resilience during the etching process.

Click to download full resolution via product page

**Caption:** Step-by-step workflow for a standard photolithography process.

3.2.2 Mesa Etching Protocol Either dry or wet etching can be used to define the mesa. Dry etching provides more anisotropic profiles and better dimensional control, which is critical for small, high-speed devices.[11]

Protocol A: Dry Etching (ICP-RIE)

- Place the patterned wafer into the ICP-RIE chamber.

- Perform a breakthrough etch using Ar plasma to remove any native oxide.

- Etch the GaAs/AlGaAs layers using a BCl<sub>3</sub>/Ar plasma chemistry.[11]

- Monitor the etch depth in-situ using laser interferometry or ex-situ with a profilometer until the n+-GaAs layer is exposed.

- Remove the remaining photoresist using an oxygen plasma ash followed by a solvent clean (acetone).

Protocol B: Wet Etching

- Prepare the etching solution. A common etchant for GaAs is a solution of Phosphoric Acid,

Hydrogen Peroxide, and DI Water.[12]

- Immerse the patterned wafer in the etchant solution with gentle agitation.

- Etch for a calibrated time to reach the n<sup>+</sup>-GaAs layer. The process must be timed carefully as wet etching is isotropic.

- Terminate the etch by immersing the wafer in DI water, followed by an N2 blow dry.

- Strip the photoresist using acetone.

Table 2: Comparison of Wet and Dry Etching Parameters

| Parameter         | Dry Etching (ICP-RIE)                      | Wet Etching                                                                                                                        |  |

|-------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| Chemistry/Etchant | BCl <sub>3</sub> /Ar Plasma[11]            | H <sub>3</sub> PO <sub>4</sub> :H <sub>2</sub> O <sub>2</sub> :H <sub>2</sub> O (e.g., 3:1:50)<br>[12]                             |  |

| Selectivity       | Moderate; can be tuned with gas chemistry. | High (e.g., Citric Acid:H <sub>2</sub> O <sub>2</sub> is<br>highly selective for GaAs over<br>AlGaAs with high Al content)<br>[12] |  |

| Profile           | Anisotropic (vertical sidewalls)           | Isotropic (undercutting)                                                                                                           |  |

| Control           | High; endpoint detection possible.         | Low; relies on timed etching.                                                                                                      |  |

| Typical Etch Rate | 50-300 nm/min (process dependent)          | ~100-500 nm/min<br>(concentration dependent)                                                                                       |  |

### **Ohmic Contact Formation**

Separate photolithography, metal deposition, and lift-off steps are required to form the p-type and n-type ohmic contacts.

#### 3.3.1 P-type Contact Protocol (Ti/Pt/Au)

- Perform a photolithography step (as in 3.2.1) to define the p-contact window on the top of the mesa.

- Prior to metal deposition, perform a brief surface treatment with an HCI:H<sub>2</sub>O solution to remove native oxides.[10]

- Load the wafer into an e-beam evaporator or sputtering system.

- Sequentially deposit Titanium (Ti), Platinum (Pt), and Gold (Au). A typical stack is 20 nm Ti / 20 nm Pt / 200 nm Au.

- Perform lift-off by immersing the wafer in acetone, using sonication to remove the unwanted metal and photoresist.

#### 3.3.2 N-type Contact Protocol (AuGe/Ni/Au)

- Perform a photolithography step to define the n-contact window on the exposed n+-GaAs layer.

- After oxide removal, load the wafer into the deposition system.

- Sequentially deposit a stack of AuGe alloy, Nickel (Ni), and Gold (Au). A common stack is 100 nm AuGe / 35 nm Ni / 300 nm Au.[13]

- · Perform lift-off as described previously.

- 3.3.3 Contact Annealing Protocol To achieve low-resistance ohmic behavior, especially for the n-contact, a thermal annealing step is required.[13][14]

- Place the wafer in a Rapid Thermal Annealing (RTA) system.

- Anneal the wafer in a nitrogen (N2) atmosphere.

- A typical annealing cycle for AuGe/Ni-based contacts is 380-420°C for 15-30 seconds.[15]

Table 3: Ohmic Contact Metallization Schemes

| Contact<br>Type | Layer   | Metallizat<br>ion Stack | Thicknes<br>s (nm) | Annealin<br>g Temp.<br>(°C) | Annealin<br>g Time (s) | Typical<br>Contact<br>Resistivit<br>y (Ω·cm²) |

|-----------------|---------|-------------------------|--------------------|-----------------------------|------------------------|-----------------------------------------------|

| p-type          | p+-GaAs | Ti / Pt / Au            | 20 / 20 /<br>200   | Not<br>required             | -                      | 10 <sup>-6</sup> - 10 <sup>-7</sup>           |

| n-type          | n+-GaAs | AuGe / Ni /<br>Au       | 100 / 35 /<br>300  | 400[15]                     | 15[15]                 | < 1 x<br>10 <sup>-6</sup> [16]                |

## **Passivation and Planarization**

A dielectric layer is deposited to passivate the exposed surfaces of the photodetector, protecting it from the environment and reducing surface leakage currents.

#### Protocol:

- Deposit a layer of Silicon Nitride (SiN<sub>x</sub>) or a polymer like Benzocyclobutene (BCB) over the entire wafer. BCB is often used for planarization and reducing parasitic capacitance.[11]

- If required, perform another photolithography and dry etching step (e.g., using CF<sub>4</sub> RIE for BCB) to open vias to the p- and n-contact pads for probing.[11]

- Deposit a final thick metal layer (e.g., Ti/Au) for bond pads.

## **Device Characterization**

After fabrication, the devices are tested to determine their key performance metrics.

#### 4.1 Electrical Characterization

- Place the wafer on a probe station.

- Measure the current-voltage (I-V) characteristics in the dark using a semiconductor parameter analyzer. This is used to determine the dark current, which should be as low as possible (typically in the nA range or lower).[11]

- Determine the breakdown voltage from the reverse bias I-V curve.

#### 4.2 Optical Characterization

- Illuminate the photodetector's optical aperture with a calibrated light source (e.g., an 850 nm laser for GaAs detectors).

- Measure the photocurrent as a function of applied reverse bias and incident optical power.[1]

- Calculate the responsivity (in A/W) by dividing the generated photocurrent by the incident optical power.

- Measure the spectral response by sweeping the wavelength of the incident light and recording the photocurrent to determine the operational wavelength range of the detector.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. pubs.aip.org [pubs.aip.org]

- 2. Spectral response curves of InGaAs, silicon, and GaAs detectors [eureka.patsnap.com]

- 3. A Comprehensive Guide to Gallium Arsenide (GaAs) Wafers [sputtertargets.net]

- 4. pubs.aip.org [pubs.aip.org]

- 5. mdpi.com [mdpi.com]

- 6. OPG [opg.optica.org]

- 7. Advanced AlGaAs/GaAs Heterostructures Grown by MOVPE [mdpi.com]

- 8. sensors.myu-group.co.jp [sensors.myu-group.co.jp]

- 9. azonano.com [azonano.com]

- 10. csmantech.org [csmantech.org]

- 11. csmantech.org [csmantech.org]

- 12. experts.illinois.edu [experts.illinois.edu]

- 13. opticaapplicata.pwr.edu.pl [opticaapplicata.pwr.edu.pl]

- 14. przyrbwn.icm.edu.pl [przyrbwn.icm.edu.pl]

- 15. US5309022A Ni-Ge-Au ohmic contacts for GaAs and GaAlAs Google Patents [patents.google.com]

- 16. osti.gov [osti.gov]

- To cite this document: BenchChem. [fabrication process of gallium arsenide-based photodetectors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b074776#fabrication-process-of-gallium-arsenide-based-photodetectors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com