# detailed methodology for validating the GEM-5 memory model

Author: BenchChem Technical Support Team. Date: December 2025

## A Guide to Validating the GEM-5 Memory Model

Prepared for: Researchers and Engineers in Computer Architecture

This guide provides a detailed methodology for validating the memory model of the **GEM-5** simulator, a crucial step for ensuring trustworthy results in computer architecture research.[1][2] Validation involves comparing simulation outputs against a known baseline—either real hardware or a previously validated simulator—to quantify and minimize inaccuracies.[3][4] This document outlines the experimental workflow, protocols for key validation experiments, and comparative data from a sample validation study.

## Validation Methodology: A Systematic Approach

The core of **GEM-5** memory model validation is a systematic process of comparison and refinement. The primary metrics for comparison are typically memory bandwidth and average access latency, as these directly impact overall system performance.[1][5] The methodology focuses on isolating memory components (like DRAM or caches) to pinpoint sources of error.[1]

Key Methodological Steps:

Isolate the Component: Test individual memory components in isolation first (e.g., DRAM models, cache hierarchy) before validating the entire subsystem.[1] This prevents inaccuracies from other components, such as processor models, from confounding the results.[1][4][5]

- Select a Reference: Choose a reliable baseline for comparison. For DRAM models, a validated, cycle-accurate simulator like DRAMSim3 is often used as a reference.[1][5] For the complete memory subsystem, performance counters from real hardware (e.g., an Intel Core i7 or ARM processor) are the gold standard.[3][6]

- Use Synthetic and Standard Benchmarks: Employ synthetic traffic generators to stress specific memory behaviors and standard benchmarks to represent realistic workloads.[1][3]

- Configure and Run: Configure the GEM-5 model to match the reference system's

architecture as closely as possible.[3][4] Run identical benchmarks on both GEM-5 and the

reference platform.

- Analyze and Refine: Compare the performance metrics (latency, bandwidth, cache misses, etc.) and calculate the error rate. Use the discrepancies to identify and correct sources of inaccuracy in the GEM-5 model.[3]

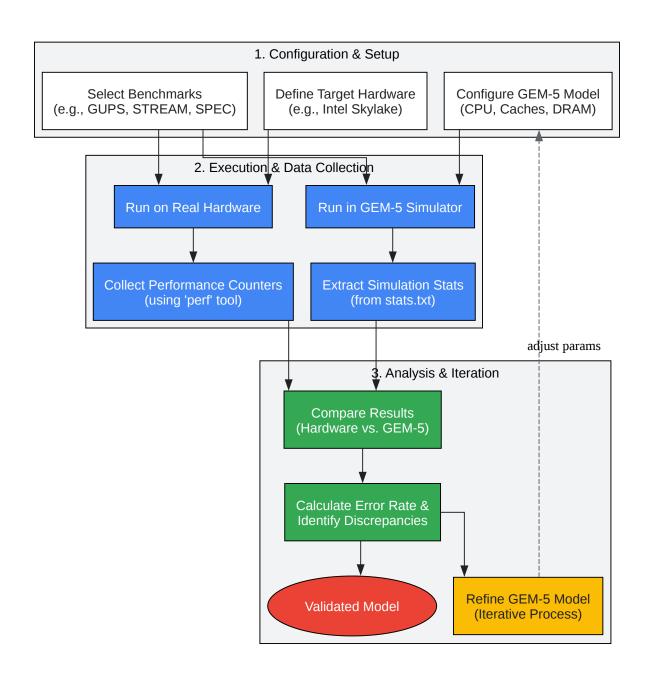

## **Validation Workflow Diagram**

The following diagram illustrates the general workflow for validating the **GEM-5** memory model against a real hardware target.

Click to download full resolution via product page

Caption: Workflow for **GEM-5** memory model validation against real hardware.

## **Experimental Protocols**

Here are detailed protocols for two key validation experiments.

Experiment 1: DRAM Model Validation using Synthetic Traffic

- Objective: To validate the bandwidth and latency of GEM-5's DRAM models (e.g., DDR4) against a trusted reference simulator like DRAMSim3.[1][5]

- Methodology:

- Setup: Configure a simple simulation in **GEM-5** with only a traffic generator and a memory controller connected to the DRAM model under test.[5] No CPU model is needed, which isolates the DRAM performance.[1][4]

- Reference: Set up the identical DRAM configuration (e.g., DDR4\_2400\_16x4) in DRAMSim3.

- Traffic Generation: Use a synthetic traffic generator, such as **GEM-5**'s PyTrafficGen, to create various access patterns (e.g., sequential, random) and stress the DRAM model with different demand bandwidths.[1]

- Data Collection:

- In **GEM-5**, measure the achieved bandwidth and average access latency from the simulation statistics.

- In DRAMSim3, collect the corresponding bandwidth and latency metrics.

- Analysis: Plot the measured bandwidth and latency from both simulators against the demand bandwidth. The results should be closely aligned, ideally within 5% for validated models.[1] A common visualization is a "hockey stick" graph for latency, which should show a sharp increase as demand approaches the DRAM's maximum bandwidth.[5]

Experiment 2: Full Memory Subsystem Validation with a Standard Benchmark

Objective: To validate the entire memory subsystem (caches and DRAM) by comparing

GEM-5's performance with a real hardware system running a memory-intensive benchmark.

#### Methodology:

Hardware Setup: Select a target hardware platform (e.g., an Intel Skylake-based machine).[4] Document its memory hierarchy specifications: L1/L2/L3 cache sizes, associativities, latencies, and DRAM configuration.[7]

#### • **GEM-5** Configuration:

- Use an appropriate CPU model (e.g., DerivO3CPU for an out-of-order core).[3]

- Configure the Ruby cache coherence protocol to model the hardware's hierarchy.[4] For instance, use a two-level cache model (L1 and L2) to approximate a three-level hierarchy if a direct match isn't available.[4]

- Use a validated DRAM model from the previous experiment as the main system memory.[1]

- Benchmark: Use a benchmark that heavily stresses the memory system, such as the RandomAccess benchmark, which is measured in Giga-Updates Per Second (GUPS).[1]

[4] The STREAM benchmark is also a good choice for measuring sustainable memory bandwidth.[8]

#### Data Collection:

- On the real hardware, use tools like perf to measure performance counters for CPU cycles, instructions, and cache misses.[3] Run the GUPS benchmark to get a hardware baseline value.

- In **GEM-5**'s Full System (FS) mode, run the same benchmark. Extract the corresponding statistics from the stats.txt output file after the simulation.[9]

- Analysis: Compare the GUPS value from hardware with the simulated value. Calculate the

percentage error to quantify the model's accuracy. Studies have shown it's possible to

achieve an error rate of around 10% with careful configuration.[1][2][4]

## **Comparative Performance Data**

Validating a simulator is an iterative process of refinement. Initial comparisons can reveal significant errors, which can be reduced by tuning the model.[3][10] The table below presents sample data from a validation study comparing a **GEM-5** model of an Intel Skylake architecture against the real hardware using the GUPS (Giga-Updates Per Second) benchmark.

| Parameter   | Intel Skylake<br>(Hardware) | GEM-5 Model<br>(Configured) | Notes                                       |

|-------------|-----------------------------|-----------------------------|---------------------------------------------|

| L1 Cache    | 32 KiB, 8-way assoc.        | 32 KiB, 8-way assoc.        | Matched hardware specifications.            |

| L2 Cache    | 256 KiB, 4-way assoc.       | 16 MiB, 16-way assoc.       | L2 in GEM-5 used to model L2/L3.[4][7]      |

| L3 Cache    | 16 MiB, 16-way assoc.       | N/A                         | Size and associativity combined into L2.[4] |

| L1 Latency  | 4 cycles                    | 4 cycles                    | Matched hardware specifications.            |

| L2 Latency  | 12 cycles                   | 40 cycles                   | Weighted average of L2/L3 latencies.[4][7]  |

| Performance | 0.39 GUPS                   | 0.43 GUPS                   | ~10% Error                                  |

Table based on data from Samani and Lowe-Power, ISCA 2022.[7]

This data shows that even with approximations in the cache hierarchy configuration, a carefully tuned **GEM-5** model can achieve a performance estimate within approximately 10% of the real hardware for a memory-intensive workload.[2][4][7]

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. arch.cs.ucdavis.edu [arch.cs.ucdavis.edu]

- 2. Validating gem5's Memory Components UC Davis Computer Architecture [arch.cs.ucdavis.edu]

- 3. sc19.supercomputing.org [sc19.supercomputing.org]

- 4. Methodologies for Evaluating Memory Models in gem5 [escholarship.org]

- 5. escholarship.org [escholarship.org]

- 6. eprints.soton.ac.uk [eprints.soton.ac.uk]

- 7. arch.cs.ucdavis.edu [arch.cs.ucdavis.edu]

- 8. Running and Evaluating STREAM benchmark for NVM in Gem5 | by Nick Felker | Medium [fleker.medium.com]

- 9. gem5: SPEC Tutorial [gem5.org]

- 10. scribd.com [scribd.com]

- To cite this document: BenchChem. [detailed methodology for validating the GEM-5 memory model]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b12410503#detailed-methodology-for-validating-thegem-5-memory-model]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

Check Availability & Pricing

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com