# contact resistance issues in TES-ADT based transistors

Author: BenchChem Technical Support Team. Date: December 2025

## Technical Support Center: TES-ADT Based Transistors

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with **TES-ADT** (5,11-bis(triethylsilylethynyl)anthradithiophene) and its derivatives (e.g., diF-**TES-ADT**) in transistor-based experiments.

## **Troubleshooting Guides & FAQs General Issues**

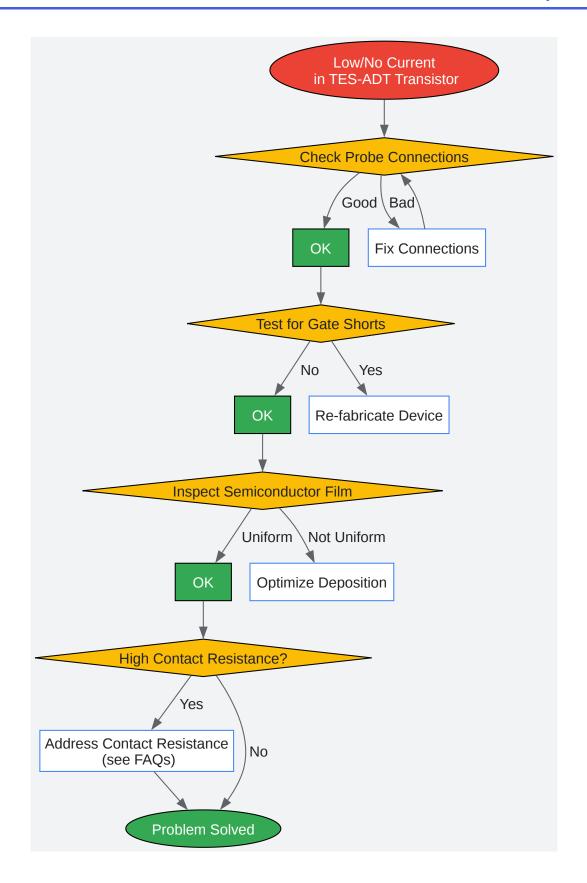

Q1: My fabricated **TES-ADT** transistor shows very low or no drain current. What are the possible causes?

A1: Several factors could lead to low or no drain current in your **TES-ADT** transistor. Here's a step-by-step troubleshooting guide:

- Verify Electrical Connections: Ensure that the probes from your measurement setup are making good contact with the source, drain, and gate electrodes.

- Check for Shorts: Test for shorts between the gate and the source/drain electrodes. A short in the gate dielectric will prevent proper transistor operation.

### Troubleshooting & Optimization

- Semiconductor Film Quality: Visually inspect the **TES-ADT** film for uniformity and continuity. Cracks, dewetting, or a non-uniform film can disrupt the channel. The crystallization of the **TES-ADT** film is crucial for good performance.[1][2]

- Contact Issues: High contact resistance at the source and drain electrodes can severely limit the current. This is a common issue and is addressed in more detail in the following sections.

- Processing Residues: Ensure that no residues from solvents or other processing steps are

present on the semiconductor or dielectric surfaces, as they can act as traps or insulators.

Q2: The measured charge carrier mobility in my diF-**TES-ADT** transistor is significantly lower than reported values. Why might this be?

A2: Lower than expected mobility is a frequent challenge and is often linked to contact resistance.

- Contact Resistance Effects: A high contact resistance can lead to an underestimation of the

intrinsic charge carrier mobility.[3] The voltage drop across the contacts reduces the effective

voltage across the channel, leading to an artificially low calculated mobility. It is crucial to

measure and account for contact resistance, for instance by using the Transmission Line

Method (TLM).

- Gate Voltage Dependence: Both contact resistance and channel resistance in organic transistors are often dependent on the gate voltage.[4][5][6] If the contact resistance does not decrease as rapidly as the channel resistance with increasing gate voltage, it can dominate the device performance and lead to an apparent lower mobility. An apparent high mobility at low gate voltages can sometimes be an artifact of a rapidly decreasing contact resistance.[5]

- Semiconductor Morphology: The crystallinity and domain connectivity of the diF-TES-ADT film are critical for high mobility. Poorly connected or misaligned crystalline domains can significantly reduce charge transport.[7]

- Bias Stress Effects: Prolonged application of a gate voltage can lead to a degradation in performance, including a decrease in mobility. This effect can be influenced by the choice of electrode metal.[8]

### **Contact Resistance Issues**

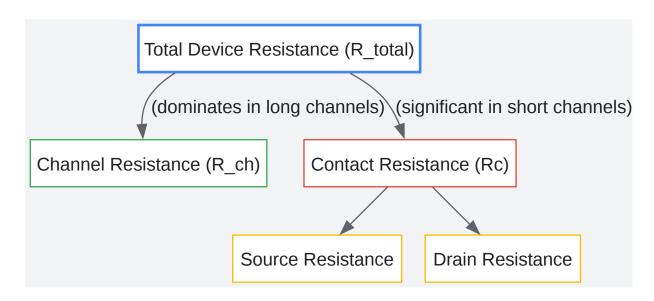

Q3: What is contact resistance and why is it a problem in **TES-ADT** transistors?

A3: Contact resistance (Rc) is the parasitic resistance at the interface between the metal electrode (source or drain) and the organic semiconductor layer.[9] It arises from factors like an energy barrier to charge injection (Schottky barrier), poor physical contact, or disordered regions in the semiconductor near the electrode.[2][3] In high-mobility materials like **TES-ADT**, where the channel resistance (Rch) is low, the contact resistance can become a significant portion of the total device resistance, limiting the overall performance and leading to inaccurate measurements of intrinsic material properties.[10][11]

Q4: How can I measure the contact resistance in my devices?

A4: The most common and reliable method for measuring contact resistance is the Transmission Line Method (TLM). This technique separates the contact resistance from the channel resistance by measuring a series of transistors with identical widths but varying channel lengths.[11] Other methods include the gated four-probe technique and Scanning Kelvin Probe Microscopy (SKPM), which can map the potential distribution across the channel and directly visualize the voltage drops at the contacts.[4][12][13][14]

Q5: My contact resistance is too high. What are the common causes and how can I reduce it?

A5: High contact resistance can stem from several sources. Here are some common causes and mitigation strategies:

- Energy Barrier: A significant energy barrier between the work function of the electrode metal and the molecular orbitals of the **TES-ADT** can impede charge injection.[3][4]

- Mitigation: Select electrode metals with work functions that align well with the charge transport level of the TES-ADT. For p-type semiconductors like TES-ADT, high work function metals (e.g., Gold, Palladium) are generally preferred.

- Interface Contamination: Contaminants or oxide layers on the electrode surface can create an insulating barrier.

- Mitigation: Ensure pristine surfaces by using clean deposition techniques and consider insitu processing. A UV-ozone treatment of the substrate before semiconductor deposition can also be beneficial.[1]

- Poor Film Morphology at the Contact: The morphology of the TES-ADT film at the contact interface is crucial.

- Mitigation: Optimizing deposition parameters and post-deposition annealing can improve crystallinity at the interface.[15] Surface treatment of the electrodes with self-assembled monolayers (SAMs), such as pentafluorobenzothiol (PFBT), can reduce the surface energy and promote better film growth and charge injection.[16]

- Device Architecture: The device geometry (e.g., top-contact vs. bottom-contact) can influence the contact resistance. Top-contact structures often exhibit lower contact resistance.

- Electrode Deposition Rate: A slow deposition rate for the metal electrodes can lead to the formation of larger grains at the injection interface, which can reduce contact resistance.[17]

## **Quantitative Data Summary**

The following tables summarize typical contact resistance values and influencing factors for organic transistors, including those based on **TES-ADT** derivatives.

| Parameter                       | Typical Values                                           | Semiconductor                           | Notes                                                          |

|---------------------------------|----------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------|

| Contact Resistance<br>(Rc)      | 200 Ω·cm - 1 kΩ·cm                                       | diF-TES-ADT, various<br>small molecules | Can vary significantly with processing conditions.[11][17][18] |

| Specific Contact<br>Resistivity | < 10 <sup>-4</sup> Ω·cm²                                 | Ink-jet printed IGZO                    | Lower values are desirable for high-performance devices. [19]  |

| Mobility                        | up to 1.5 cm²/Vs<br>(film), 6 cm²/Vs (single<br>crystal) | diF-TES-ADT                             | High mobility makes low contact resistance critical.[7][20]    |

| Factor                        | Effect on Contact<br>Resistance                                                                     | Recommended Practice for TES-ADT                                                       |

|-------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Electrode Metal Work Function | Mismatch with semiconductor energy levels increases Rc.                                             | Use high work function metals (e.g., Au, Pd) for p-type TES-ADT.                       |

| Semiconductor Thickness       | Increasing thickness can sometimes increase Rc.[4]                                                  | Optimize thickness; very thin films can also have high Rc due to poor step coverage.   |

| Electrode Thickness           | Thinner source/drain<br>electrodes (e.g., 20 nm) can<br>reduce Rc in bottom-contact<br>devices.[21] | Optimize electrode thickness in conjunction with semiconductor thickness.              |

| Gate Voltage                  | Rc generally decreases with increasing gate voltage.[4][6]                                          | Characterize Rc at various gate voltages to understand its impact on device operation. |

| Annealing Temperature         | Optimal annealing can improve film crystallinity and reduce Rc.                                     | For TES-ADT, annealing at 80°C for 60 minutes has shown good results.[15]              |

| Electrode Surface Treatment   | SAMs can reduce surface energy and improve charge injection.                                        | Treatment with PFBT on gold electrodes is a common strategy.[16]                       |

## **Experimental Protocols**

# Protocol 1: Fabrication of a Bottom-Gate, Bottom-Contact (BGBC) TES-ADT Transistor

This protocol outlines a general procedure for fabricating a BGBC **TES-ADT** transistor.

- Substrate Preparation:

- Start with a heavily doped silicon wafer (acting as the gate electrode) with a thermally grown silicon dioxide layer (gate dielectric).

- Clean the substrate sequentially in an ultrasonic bath with deionized water, acetone, and isopropanol.

- Dry the substrate with nitrogen gas.

- Electrode Patterning:

- Use photolithography to define the source and drain electrode patterns.

- Deposit the electrode metal (e.g., a thin adhesion layer of Cr or Ti followed by Au) using thermal or e-beam evaporation.

- Perform lift-off in a suitable solvent to remove the photoresist and unwanted metal.

- Surface Treatment (Optional but Recommended):

- Treat the substrate with a UV-ozone cleaner to remove organic residues.

- Immerse the substrate in a solution of a self-assembled monolayer (e.g., PFBT in isopropanol) to modify the electrode surfaces.[16]

- Rinse with isopropanol and dry with nitrogen.

- TES-ADT Solution Preparation:

- Prepare a solution of **TES-ADT** in a suitable solvent like toluene or chlorobenzene at a specific concentration (e.g., 8% wt).[1]

- Semiconductor Deposition:

- Deposit the TES-ADT solution onto the substrate using a technique like spin-coating or drop-casting.[1]

- Control the deposition parameters (e.g., spin speed, temperature) to achieve the desired film thickness and morphology.

- Annealing:

- Anneal the sample at an optimized temperature and time (e.g., 80°C for 60 minutes) to promote crystallization of the TES-ADT film.[15]

- Characterization:

- Perform electrical characterization using a semiconductor parameter analyzer in a probe station.

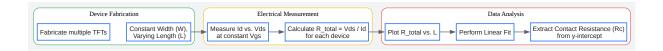

# Protocol 2: Measuring Contact Resistance using the Transmission Line Method (TLM)

This protocol describes the steps to measure contact resistance using TLM.

- Device Fabrication:

- Fabricate a set of transistors on the same substrate with a constant channel width (W) and varying channel lengths (L). Ensure all other fabrication parameters are identical for all devices.

- Electrical Measurement:

- For each transistor, measure the drain current (Id) as a function of the source-drain voltage (Vds) at a constant gate voltage (Vgs) in the linear regime (low Vds).

- Calculate the total resistance (R\_total) for each device using the formula: R\_total = Vds / Id.

- Data Analysis:

- Plot the total resistance (R total) as a function of the channel length (L).

- Perform a linear fit to the data points. The equation for the line will be: R\_total = (R\_sheet / W) \* L + Rc, where R\_sheet is the sheet resistance of the channel and Rc is the contact resistance.

- The y-intercept of the linear fit gives the total contact resistance (Rc).

- The slope of the line is equal to R\_sheet / W, from which the sheet resistance and the

effective mobility can be calculated.[11]

- Gate Voltage Dependence:

- Repeat steps 2 and 3 for different gate voltages (Vgs) to determine the gate voltage dependence of the contact resistance.[4]

### **Visualizations**

Click to download full resolution via product page

Caption: Workflow for measuring contact resistance using the Transmission Line Method (TLM).

Click to download full resolution via product page

Caption: Components of total resistance in a field-effect transistor.

Click to download full resolution via product page

Caption: Troubleshooting flowchart for low current in **TES-ADT** transistors.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. physics.rutgers.edu [physics.rutgers.edu]

- 2. Single-step processing of TES-ADT based transistors | Laboratory of Organic Matter Physics [www-lfos.ung.si]

- 3. pubs.aip.org [pubs.aip.org]

- 4. pubs.aip.org [pubs.aip.org]

- 5. Comparing the Gate Dependence of Contact Resistance and Channel Resistance in Organic Field-Effect Transistors for Understanding the Mobility Overestimation Issue | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 6. researchgate.net [researchgate.net]

- 7. Structure—function relations in diF-TES-ADT blend organic field effect transistors studied by scanning probe microscopy - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 8. researchgate.net [researchgate.net]

- 9. Contact resistance Wikipedia [en.wikipedia.org]

- 10. fkf.mpg.de [fkf.mpg.de]

- 11. Reliability of the Transmission Line Method and Reproducibility of the Measured Contact Resistance of Organic Thin-Film Transistors PMC [pmc.ncbi.nlm.nih.gov]

- 12. researchgate.net [researchgate.net]

- 13. researchgate.net [researchgate.net]

- 14. researchgate.net [researchgate.net]

- 15. tandfonline.com [tandfonline.com]

- 16. cris.unibo.it [cris.unibo.it]

- 17. communities.springernature.com [communities.springernature.com]

- 18. researchgate.net [researchgate.net]

- 19. researchgate.net [researchgate.net]

- 20. tsapps.nist.gov [tsapps.nist.gov]

- 21. ieeexplore.ieee.org [ieeexplore.ieee.org]

- To cite this document: BenchChem. [contact resistance issues in TES-ADT based transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b565832#contact-resistance-issues-in-tes-adt-based-transistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com