# common challenges in the synthesis of gallium arsenide (GaAs) wafers

Author: BenchChem Technical Support Team. Date: December 2025

# Technical Support Center: Gallium Arsenide (GaAs) Wafer Synthesis

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in overcoming common challenges during the synthesis of **Gallium** Arsenide (GaAs) wafers.

# **Troubleshooting Guides**

This section provides systematic approaches to diagnose and resolve common problems encountered during GaAs wafer synthesis using Liquid Encapsulated Czochralski (LEC) and Vertical Gradient Freeze (VGF) methods.

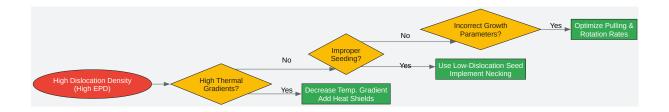

## **Problem: High Dislocation Density in LEC-Grown Wafers**

High dislocation density is a prevalent issue in LEC growth, primarily caused by significant thermal stresses.[1]

#### Symptoms:

- Wafers exhibit high Etch Pit Density (EPD) counts (> 5 x 10<sup>4</sup> cm<sup>-2</sup>).

- Increased device leakage currents and reduced carrier mobility.

• Poor performance and reliability of fabricated devices.[2]

Possible Causes and Solutions:

| Cause                                | Recommended Solution                                                                                                                                                                                                                                                                                             |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Thermal Gradients               | Decrease the temperature gradient across the crystal. For LEC, typical gradients are around 100-150 K/cm; aim for the lower end of this range.[3] Modify the furnace design to include heat shields to reduce radial heat loss.                                                                                  |

| Improper Seeding                     | Ensure the use of a low-dislocation density seed crystal. Implement a "necking" procedure (Dash necking) where the crystal diameter is reduced after seeding to interrupt the propagation of dislocations from the seed.                                                                                         |

| Incorrect Pulling and Rotation Rates | Optimize the crystal pulling and crucible rotation rates. Typical pulling rates for LEC are 7-10 mm/h.[4] Slower pulling rates can reduce thermal shock at the growth interface. The crucible rotation rate, typically 0-20 rpm, influences melt flow and temperature distribution.[5]                           |

| Melt Stoichiometry Imbalance         | Precisely control the arsenic overpressure in the growth chamber to maintain a stoichiometric melt. An arsenic-rich melt can sometimes reduce the incidence of twinning, a related defect.                                                                                                                       |

| B₂O₃ Encapsulant Issues              | Ensure the boric oxide (B <sub>2</sub> O <sub>3</sub> ) encapsulant is of high purity and sufficiently thick to prevent arsenic loss and provide thermal stability.  However, be aware that the low thermal conductivity of B <sub>2</sub> O <sub>3</sub> can contribute to non-linear temperature gradients.[1] |

# Problem: Polycrystallinity or Twinning in VGF-Grown Wafers

The formation of multiple crystal grains (polycrystallinity) or twin boundaries is a common failure mode in VGF growth, often related to thermal stresses and interface shape.[6][7]

#### Symptoms:

- Visible grain boundaries on the wafer surface.

- Sudden changes in crystal orientation observed through characterization techniques.

- Reduced single-crystal yield from the ingot.

Possible Causes and Solutions:

| Cause                                    | Recommended Solution                                                                                                                                                                                                     |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unfavorable Crystal-Melt Interface Shape | Optimize the heater power distribution to achieve a slightly convex interface shape, which helps to suppress the formation of new grains.  [8] Numerical modeling can aid in optimizing the furnace temperature profile. |

| High Thermal Stresses                    | Reduce the axial and radial temperature gradients. VGF allows for lower gradients compared to LEC. Lowering these gradients minimizes thermal stress, a primary driver for twinning and dislocation formation.[8][9]     |

| Improper Seed Crystal Quality or Seating | Use a high-quality, single-crystal seed and ensure it is properly seated at the bottom of the crucible to promote uniform initial growth.                                                                                |

| Incorrect Cooling Rate                   | Implement a controlled, slow cooling rate after solidification to prevent the introduction of stress and defects into the crystal.                                                                                       |

| Crucible and Furnace Design              | The design of the crucible and its support can significantly influence the temperature field.  Optimizing these components can lead to a more stable growth process.                                                     |

# Frequently Asked Questions (FAQs)

Q1: What are the primary sources of silicon (Si) and carbon (C) impurities in GaAs wafers, and what are their effects?

A1: Silicon and carbon are common unintentional impurities in GaAs.[2]

• Silicon (Si): The primary source of silicon is the quartz (SiO<sub>2</sub>) components used in the growth furnace and crucibles, which can react with **gallium** at high temperatures.[10] Silicon is an amphoteric dopant, meaning it can substitute for both Ga and As atoms. In Ga-rich conditions, it tends to occupy Ga sites and act as a donor (n-type). In As-rich conditions, it

## Troubleshooting & Optimization

can occupy As sites and act as an acceptor (p-type). High Si concentration can lead to compensation, reducing carrier mobility.[11]

• Carbon (C): Carbon contamination often originates from the graphite heaters and crucibles used in the furnace.[2] It typically substitutes for arsenic atoms, acting as a shallow acceptor (p-type). High carbon concentrations can significantly affect the electrical properties of the wafer.[12][13]

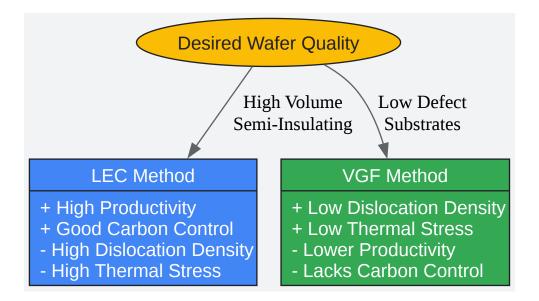

Q2: How does the choice between LEC and VGF growth methods affect wafer quality?

A2: LEC and VGF are the two dominant methods for bulk GaAs growth, each with distinct advantages and disadvantages that impact wafer quality.

- Liquid Encapsulated Czochralski (LEC): This method allows for higher growth rates and is

well-suited for producing large-diameter, semi-insulating wafers.[3] However, the high

thermal gradients inherent in the process typically result in higher dislocation densities (EPD

> 10<sup>4</sup> cm<sup>-2</sup>).[3]

- Vertical Gradient Freeze (VGF): VGF utilizes lower thermal gradients, which results in significantly lower dislocation densities (EPD < 5000 cm<sup>-2</sup>).[3][4] This method offers better control over crystal shape. However, VGF has a slower growth rate and less control over carbon doping compared to LEC.[14]

Q3: What causes twinning in LEC-grown GaAs, and how can it be prevented?

A3: Twinning, the formation of a mirror-image crystal lattice, is a significant issue in LEC growth. It is often caused by an unstable growth interface.[1] This instability can be triggered by thermal fluctuations, impurities in the melt, or issues with the seed crystal. To prevent twinning, it is crucial to maintain a stable thermal environment, use high-purity source materials, and ensure a high-quality seed crystal with proper orientation. Growing from a slightly arsenic-rich melt has also been shown to reduce the incidence of twinning.

Q4: How is stoichiometry controlled during GaAs synthesis?

A4: Due to the high vapor pressure of arsenic at the melting point of GaAs, maintaining a 1:1 ratio of Ga to As is critical. This is typically achieved by applying an arsenic overpressure in the sealed growth environment (ampoule or high-pressure chamber).[15][16] In both LEC and VGF,

the temperature of a separate arsenic source is controlled to maintain the desired arsenic partial pressure over the melt, preventing its decomposition.

Q5: What are "point defects" in GaAs, and why are they important?

A5: Point defects are zero-dimensional imperfections in the crystal lattice. In GaAs, these include:

- Vacancies: An empty lattice site where a Ga (V\_Ga) or As (V\_As) atom is missing.

- Interstitials: A Ga (Ga i) or As (As i) atom located in a non-lattice position.

- Antisite defects: A Ga atom on an As site (Ga\_As) or an As atom on a Ga site (As\_Ga).[2]

These defects can create energy levels within the bandgap, acting as traps or recombination centers that affect the electronic and optical properties of the material. The famous "EL2" deep-level donor in undoped semi-insulating GaAs is related to an arsenic antisite defect.

### **Data Presentation**

Table 1: Comparison of LEC and VGF Growth Methods for GaAs Wafers

| Parameter             | Liquid Encapsulated<br>Czochralski (LEC)  | Vertical Gradient Freeze<br>(VGF) |

|-----------------------|-------------------------------------------|-----------------------------------|

| Typical Growth Rate   | 7 - 10 mm/h[4]                            | ~3 mm/h[4]                        |

| Temperature Gradient  | High (~100 - 150 K/cm)[3]                 | Low (< 25 °C/cm)[10]              |

| Operating Pressure    | High (e.g., 2 MPa Argon)[3]               | Lower than LEC                    |

| Typical EPD (undoped) | > 10 <sup>4</sup> cm <sup>-2</sup> [3]    | < 5000 cm <sup>-2</sup> [3]       |

| Carbon Doping Control | Good[14]                                  | Lacking[14]                       |

| Real-time Observation | Possible[14]                              | Not possible[14]                  |

| Productivity          | High[14]                                  | Lower[14]                         |

| Cost                  | High investment and operational costs[14] | Lower costs[14]                   |

**Table 2: Effects of Common Impurities on GaAs**

**Electrical Properties**

| Impurity     | Common<br>Source                   | Typical Site | Electrical<br>Activity      | Effect on<br>Properties                                                                                                                                              |

|--------------|------------------------------------|--------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Silicon (Si) | Quartz (SiO2)<br>furnace parts[10] | Ga or As     | Amphoteric (n or<br>p-type) | Can increase carrier concentration but high levels lead to compensation and reduced mobility.                                                                        |

| Carbon (C)   | Graphite furnace<br>parts[2]       | As           | Acceptor (p-type)           | Increases hole concentration. At very high concentrations (>4 x 10 <sup>18</sup> cm <sup>-3</sup> ), can lead to anomalous mobility enhancement at low temperatures. |

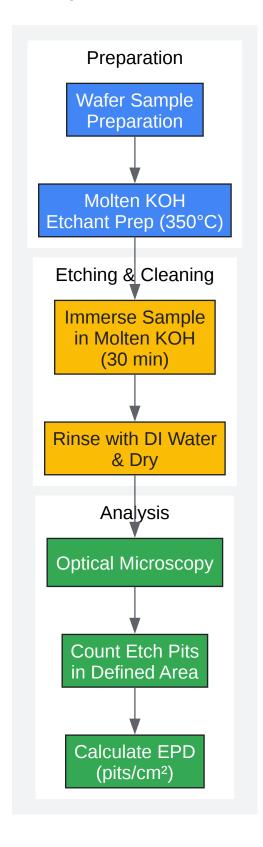

# Experimental Protocols Protocol 1: Etch Pit Density (EPD) Measurement using Molten KOH

This protocol describes the standard method for revealing dislocation defects on a GaAs wafer surface for EPD analysis.[17]

Materials and Equipment:

GaAs wafer sample

- Potassium Hydroxide (KOH) pellets

- High-purity crucibles (e.g., nickel or glassy carbon)

- Furnace or hot plate capable of reaching 350-450°C

- Deionized (DI) water

- Optical microscope with calibrated stage

- Personal Protective Equipment (PPE): heat-resistant gloves, safety glasses, lab coat

#### Procedure:

- Wafer Preparation: Cleave a representative sample from the GaAs wafer.

- Etchant Preparation: In a clean crucible, carefully place KOH pellets.

- Etching:

- Heat the crucible containing KOH to 350°C in a furnace or on a hot plate until the KOH is completely molten.[18]

- Using tweezers, carefully immerse the GaAs sample into the molten KOH.

- Etch for approximately 30 minutes.[18] The etch rate is typically around 0.08 μm/min.[18]

- Cleaning:

- Carefully remove the sample from the molten KOH and allow it to cool.

- Rinse the sample thoroughly with DI water to remove any residual KOH.

- Dry the sample with a gentle stream of nitrogen.

- Microscopy and Counting:

- Place the etched wafer on the microscope stage.

- Using a magnification that allows for clear identification of etch pits, count the number of pits within a defined area (e.g., 0.01 cm²).[17]

- Repeat the counting process at multiple locations across the wafer to obtain an average EPD value.

- EPD is calculated as the number of pits divided by the area of the measurement field.

# Protocol 2: Cross-Sectional Transmission Electron Microscopy (TEM) Sample Preparation

This protocol outlines a general procedure for preparing a cross-sectional GaAs sample for TEM analysis to study defects and layer structures.

#### Materials and Equipment:

- GaAs wafer

- Dummy wafer (e.g., silicon)

- Diamond scribe

- Epoxy (e.g., M-Bond)

- Clamping device

- Grinding/polishing equipment with various grit papers and polishing cloths

- Dimple grinder

- Ion mill

- TEM grid (e.g., copper)

#### Procedure:

Scribing and Cleaving: Scribe and cleave two small pieces (e.g., 1.5 mm x 4 mm) from the GaAs wafer.[1]

- Sample Sandwiching:

- Glue the two GaAs pieces together face-to-face (epitaxial layer to epitaxial layer) using a thin layer of epoxy.

- For mechanical support, glue dummy wafer pieces to the outer sides of the GaAs sandwich.[1]

- Clamp the "sandwich" and cure the epoxy according to the manufacturer's instructions (e.g., 24 hours at room temperature).[19]

- Mechanical Thinning:

- Mount the sample onto a polishing stub.

- Mechanically grind and polish the cross-section of the sample using progressively finer grit papers and polishing cloths until the sample is approximately 20 μm thick.[1]

- Dimpling: Use a dimple grinder to create a concave depression in the center of the sample, thinning the central area to a few micrometers.

- Ion Milling:

- Mount the dimpled sample onto a TEM grid.[19]

- Use an ion mill with a low-energy argon ion beam to mill the sample at a shallow angle until a small perforation appears at the center of the dimple. The area around the perforation should be electron-transparent.

- A final, brief etching step with a solution like 0.5% Br₂/CH₃OH can be used to remove ion milling-induced surface damage.[20]

# Protocol 3: Atomic Force Microscopy (AFM) for Surface Roughness Analysis

This protocol provides a general workflow for measuring the surface roughness of a polished GaAs wafer.[21]

#### Materials and Equipment:

- GaAs wafer sample

- Atomic Force Microscope (AFM)

- Appropriate AFM cantilever/tip (a high-resolution tip is recommended for accurate quantitative measurements)[22]

- Sample mounting stage

#### Procedure:

- Sample Mounting: Securely mount the GaAs wafer onto the AFM sample stage. Ensure the surface to be analyzed is clean and free of particulates.

- System Setup:

- Install a suitable AFM tip into the cantilever holder.

- Load the holder into the AFM head.

- Align the laser onto the cantilever and adjust the photodetector to obtain a strong signal.

- Imaging Parameters:

- Select the appropriate imaging mode (e.g., tapping mode is often preferred for delicate surfaces to minimize damage).

- Set the scan size (e.g., 1 μm x 1 μm), scan rate, and feedback loop gains.

- Engage and Scan:

- Approach the tip to the wafer surface until it begins to interact.

- Start the scan and acquire the topography image.

- Data Analysis:

- Use the AFM software to process the image. This may include plane fitting to remove tilt.

- Calculate the desired roughness parameters from the topography data. A common parameter is the root mean square (RMS) roughness (Sq).

- For a comprehensive analysis, perform measurements at multiple locations on the wafer.

[21]

## **Visualizations**

Click to download full resolution via product page

Caption: Troubleshooting workflow for high dislocation density in GaAs wafers.

Click to download full resolution via product page

Caption: Logical relationship between growth method and resulting wafer quality.

Click to download full resolution via product page

Caption: Experimental workflow for Etch Pit Density (EPD) measurement.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. apps.dtic.mil [apps.dtic.mil]

- 2. researchgate.net [researchgate.net]

- 3. powerwaywafer.com [powerwaywafer.com]

- 4. researchgate.net [researchgate.net]

- 5. mdpi.com [mdpi.com]

- 6. mdpi.com [mdpi.com]

- 7. GaAs Wafer Technologie Freiberger Compound Materials [freiberger.com]

- 8. str-soft.com [str-soft.com]

- 9. cpb.iphy.ac.cn [cpb.iphy.ac.cn]

- 10. osti.gov [osti.gov]

- 11. pubs.aip.org [pubs.aip.org]

- 12. pubs.aip.org [pubs.aip.org]

- 13. pubs.aip.org [pubs.aip.org]

- 14. youtube.com [youtube.com]

- 15. Semiconductors Ingot Growing | Occupational Safety and Health Administration [osha.gov]

- 16. chem.libretexts.org [chem.libretexts.org]

- 17. powerwaywafer.com [powerwaywafer.com]

- 18. KOH:NaOH GaAs Wet Etchant by Chemical Composition [steeldata.info]

- 19. rrc.uic.edu [rrc.uic.edu]

- 20. A technique for the preparation of cross-sectional TEM samples of ZnSe/GaAs heterostructures which eliminates process-induced defects - PubMed [pubmed.ncbi.nlm.nih.gov]

- 21. theengineer.markallengroup.com [theengineer.markallengroup.com]

- 22. How to Choose AFM Tips for Measuring Silicon Wafer Roughness [spmtips.com]

- To cite this document: BenchChem. [common challenges in the synthesis of gallium arsenide (GaAs) wafers]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b148102#common-challenges-in-the-synthesis-of-gallium-arsenide-gaas-wafers]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com