# Unlocking Architectural Insights: A Technical Guide to GEM-5 Statistics and Output Analysis

Author: BenchChem Technical Support Team. Date: December 2025

For Researchers, Scientists, and Drug Development Professionals

In the intricate world of computer architecture research and its application in fields like computational drug discovery, the ability to accurately model and analyze system performance is paramount. The **GEM-5** simulator stands as a cornerstone for such exploration, offering a powerful and flexible platform for detailed microarchitectural investigation. However, the wealth of data generated by **GEM-5** can be as daunting as it is valuable. This in-depth technical guide provides a comprehensive walkthrough of **GEM-5**'s statistical output, empowering researchers to harness this data for robust analysis and informed decision-making.

# **Deconstructing the GEM-5 Output: m5out Directory**

Upon completion of a **GEM-5** simulation, a directory named m5out is generated, containing the primary results of the experiment.[1][2] For the discerning researcher, two files within this directory are of immediate importance: config.ini and stats.txt.

- config.ini: This file serves as the definitive record of the simulated system's configuration.[1]

[2] It meticulously lists every simulation object (SimObject) created and their corresponding parameter values, including those set by default.[1][2] It is considered a best practice to always review this file as a sanity check to ensure the simulation environment aligns with the intended experimental setup.[2]

- stats.txt: This is the focal point of our analysis, containing a detailed dump of all registered statistics for every SimObject in the simulation.[1][2] The data is presented in a human-

readable text format, with each line representing a specific statistic.

The structure of a line in stats.txt typically follows this format:

.#

# **Core Performance Indicators: A Quantitative Overview**

The stats.txt file is rich with data. The following tables summarize key performance indicators (KPIs) that are fundamental for most research analyses.

## **Global Simulation Statistics**

These statistics provide a high-level summary of the entire simulation run.

| Statistic      | Description                                                                                                                          |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| sim_seconds    | The total simulated time, representing the time elapsed in the simulated world.[2][3]                                                |

| sim_ticks      | The total number of simulated clock ticks.                                                                                           |

| host_inst_rate | The rate at which the host machine executed simulation instructions, indicating the performance of the GEM-5 simulator itself.[2][3] |

| host_op_rate   | The rate at which the host machine executed simulation operations.                                                                   |

## **CPU Core Statistics (e.g., O3CPU)**

The Out-of-Order (O3) CPU model in **GEM-5** provides a wealth of statistics for detailed pipeline analysis.[4]

| Statistic Category            | Key Statistics                                                              | Description                                                         |

|-------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------|

| Instruction-Level Parallelism | ipc                                                                         | Instructions Per Cycle, a primary measure of processor performance. |

| срі                           | Cycles Per Instruction, the reciprocal of IPC.                              |                                                                     |

| committedInsts                | The total number of instructions committed.                                 |                                                                     |

| Branch Prediction             | branchPred.lookups                                                          | The total number of branch predictor lookups.                       |

| branchPred.condPredicted      | The number of conditional branches correctly predicted.                     |                                                                     |

| branchPred.condIncorrect      | The number of conditional branches incorrectly predicted.                   | _                                                                   |

| Pipeline Stages               | fetch.Insts                                                                 | Number of instructions fetched.                                     |

| decode.DecodedInsts           | Number of instructions decoded.                                             |                                                                     |

| rename.RenamedInsts           | Number of instructions renamed.                                             | _                                                                   |

| iew.InstsIssued               | Number of instructions issued to the execution units.                       | _                                                                   |

| commit.CommittedInsts         | Number of instructions committed.                                           | <del>-</del>                                                        |

| Resource Stalls               | rename.RenameStalls                                                         | Number of cycles the rename stage was stalled.                      |

| iew.IssueStalls               | Number of cycles the issue stage was stalled due to full instruction queue. |                                                                     |

| commit.ROBStalls              | Number of cycles the commit stage was stalled due to a full                 | _                                                                   |

reorder buffer.

# **Memory Hierarchy Statistics**

Understanding the memory system's behavior is critical for performance analysis.

| Statistic Category             | Key Statistics                                                    | Description                                               |

|--------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------|

| L1 Caches (Instruction & Data) | icache.overall_miss_rate                                          | The miss rate of the L1 instruction cache.                |

| dcache.overall_miss_rate       | The miss rate of the L1 data cache.                               |                                                           |

| icache.avg_miss_latency        | The average latency for an instruction cache miss.                |                                                           |

| dcache.avg_miss_latency        | The average latency for a data cache miss.                        |                                                           |

| L2 Cache                       | l2.overall_miss_rate                                              | The overall miss rate of the L2 cache.                    |

| l2.avg_miss_latency            | The average latency for an L2 cache miss.                         |                                                           |

| DRAM Controller                | dram.readReqs                                                     | The total number of read requests to the DRAM controller. |

| dram.writeReqs                 | The total number of write requests to the DRAM controller.        |                                                           |

| dram.avgMemAccLat              | The average memory access latency as seen by the DRAM controller. | _                                                         |

| dram.bwTotal                   | The total bandwidth utilized for the DRAM.                        |                                                           |

# **Experimental Protocols for Research Analysis**

A structured approach is essential for meaningful analysis of **GEM-5** data. The following protocols outline common experimental workflows.

## **Protocol 1: Baseline Performance Characterization**

Objective: To establish a baseline performance profile of an application on a specific architecture.

#### Methodology:

- Configuration: Define a baseline system configuration using a GEM-5 Python configuration script. Specify the CPU model (e.g., O3CPU), cache hierarchy (sizes, associativities), and memory technology.

- Simulation: Run the target application workload on the configured system.

- Data Extraction: From stats.txt, extract key performance indicators, including sim\_seconds, system.cpu.ipc, system.cpu.cpi, and the miss rates for all cache levels.

- Analysis: Document these baseline metrics. They will serve as the reference point for all future architectural explorations.

## **Protocol 2: Analyzing the Impact of Cache Size**

Objective: To quantify the effect of L2 cache size on application performance.

### Methodology:

- Iterative Configuration: Create a series of GEM-5 configuration scripts, each identical to the baseline except for the L2 cache size. For example, you might test sizes of 256kB, 512kB, 1MB, and 2MB.

- Batch Simulation: Execute the simulation for each configuration.

- Targeted Data Extraction: For each run, parse the stats.txt file to extract system.cpu.ipc, system.l2.overall miss rate, and system.dram.readReqs.

Comparative Analysis: Create a table comparing the extracted metrics across the different L2 cache sizes. Visualize the relationship between L2 cache size, miss rate, and IPC to identify the point of diminishing returns.

## **Protocol 3: Power and Energy Estimation**

Objective: To estimate the power and energy consumption of the simulated system.

### Methodology:

- Enable Power Modeling: In your GEM-5 configuration, enable power modeling. This can be

done using GEM-5's native MathExprPowerModel, which allows you to define power

consumption as a mathematical expression of other statistics.[5] For more detailed analysis,

GEM-5 can be integrated with external tools like McPAT.[1][6]

- Simulation: Run the simulation with power modeling enabled.

- Power Statistics Extraction: The stats.txt file will now contain power and energy-related statistics, such as system.cpu.power\_model.dynamic\_power and system.cpu.power model.static power.

- Energy Calculation: Calculate the total energy consumption by integrating the power over the simulated time. Analyze the energy breakdown between different components to identify power hotspots.

## **Mandatory Visualizations**

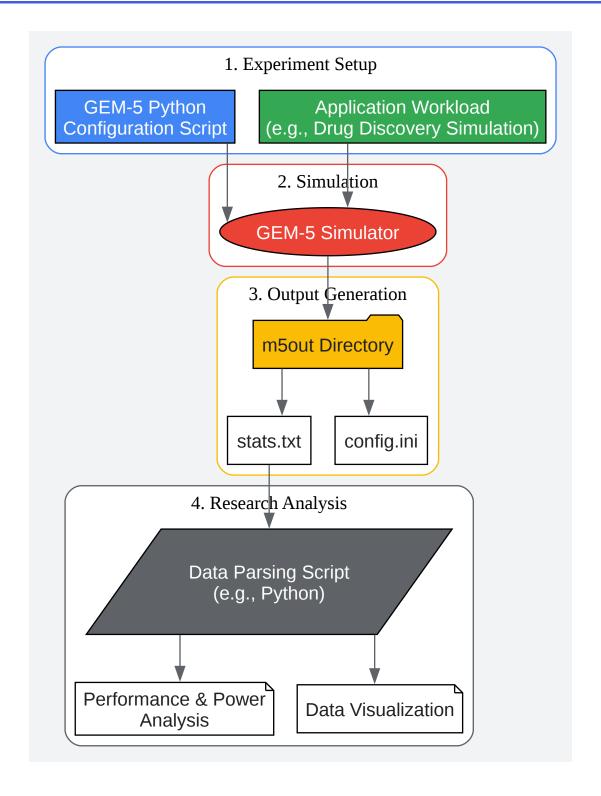

Visual diagrams are indispensable for communicating complex architectural concepts and experimental workflows. The following diagrams are rendered using the DOT language for Graphviz.

Click to download full resolution via product page

**GEM-5** Experimental Workflow

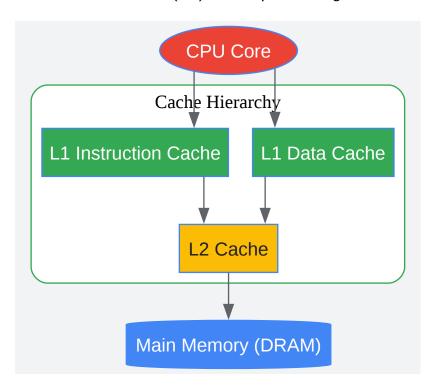

## Click to download full resolution via product page

### Out-of-Order (O3) CPU Pipeline Stages

Click to download full resolution via product page

### Typical Memory Hierarchy in **GEM-5**

By leveraging the detailed statistics provided by **GEM-5** and following structured experimental protocols, researchers can gain profound insights into the performance and power characteristics of novel computer architectures. This guide serves as a foundational resource for navigating the complexities of **GEM-5**'s output, enabling more efficient and impactful research in computationally intensive domains.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. How to get power consumption in gem5? · gem5 · Discussion #980 · GitHub [github.com]

- 2. gem5: Understanding gem5 statistics and output [gem5.org]

- 3. What is the difference between the gem5 CPU models and which one is more accurate for my simulation? - Stack Overflow [stackoverflow.com]

- 4. gem5: Out of order CPU model [gem5.org]

- 5. gem5: ARM Power Modelling [gem5.org]

- 6. eprints.soton.ac.uk [eprints.soton.ac.uk]

- To cite this document: BenchChem. [Unlocking Architectural Insights: A Technical Guide to GEM-5 Statistics and Output Analysis]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b12410503#understanding-gem-5-statistics-and-output-files-for-research-analysis]

### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com