# Troubleshooting guide for low mobility in TIPS-TAP OFETs

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |

|----------------------|-----------|-----------|

| Compound Name:       | Tips-tap  |           |

| Cat. No.:            | B14037076 | Get Quote |

## **Technical Support Center: TIPS-TAP OFETs**

Welcome to the technical support center for 6,13-bis(triisopropylsilylethynyl) pentacene (**TIPS-TAP** or TIPS-Pentacene) Organic Field-Effect Transistors (OFETs). This resource provides troubleshooting guidance and frequently asked questions (FAQs) to help researchers, scientists, and drug development professionals overcome common challenges during experimentation and achieve high-performance devices.

# Frequently Asked Questions (FAQs) & Troubleshooting Guide

1. Why is the hole mobility of my TIPS-TAP OFET exceptionally low?

Low carrier mobility is a frequent issue in solution-processed **TIPS-TAP** OFETs and can stem from several factors throughout the fabrication process. The primary reasons often relate to suboptimal morphology of the **TIPS-TAP** thin film, poor substrate preparation, or issues with the solution itself.

## Potential Causes and Solutions:

Poor Film Crystallinity and Morphology: The charge transport in TIPS-TAP OFETs is highly

dependent on the crystalline structure of the thin film. Disordered films with small crystal

grains or the presence of cracks perpendicular to the channel length can act as charge traps

and scattering sites, significantly reducing mobility.[1][2]

## Troubleshooting & Optimization

- Solution: Optimize the deposition technique and solvent evaporation rate. Slow solvent evaporation generally promotes the growth of larger, more ordered crystals.[1] Techniques like drop casting in a solvent-saturated atmosphere or off-center spin coating can improve film crystallinity.[1][3] Blending TIPS-TAP with an insulating polymer like polystyrene (PS) has also been shown to improve crystal alignment and film morphology.[4][5]

- Inappropriate Solvent Choice: The choice of solvent affects the solubility of TIPS-TAP and the drying dynamics, which in turn dictates the film morphology.

- Solution: High-boiling-point solvents such as toluene, chlorobenzene, or anisole are often preferred as they allow for slower crystallization and better molecular ordering.[3][6][7] The concentration of the TIPS-TAP solution is also a critical parameter to optimize.[3]

- Substrate Surface Contamination or Inadequate Treatment: The interface between the

dielectric and the semiconductor layer is crucial for efficient charge accumulation and

transport. A contaminated or high-energy surface can lead to poor film formation and a high

density of trap states.

- Solution: Thoroughly clean the substrates using a sequence of solvents (e.g., acetone, isopropanol) and treat them with a self-assembled monolayer (SAM) to passivate surface traps and modify the surface energy.[8][9] Common SAMs for SiO2 surfaces include octadecyltrichlorosilane (OTS), trichloro(phenyl)silane (PTS), or hexamethyldisilazane (HMDS).[1][8][10] This treatment typically makes the surface more hydrophobic, which is favorable for TIPS-TAP crystallization.[8]

- 2. My device performance is inconsistent across different batches. What could be the cause?

Device-to-device variation is a common challenge in OFET fabrication, often pointing to a lack of precise control over critical experimental parameters.

#### Potential Causes and Solutions:

Variations in Solution Preparation: The age and storage conditions of the TIPS-TAP solution

can affect its properties. Over time, solutions can degrade or absorb moisture, leading to

inconsistent film quality.[1]

- Solution: Prepare fresh solutions for each fabrication run, preferably inside a glovebox to minimize exposure to oxygen and water.[1][4] Ensure the TIPS-TAP is fully dissolved, which may require gentle heating and stirring.[4][8]

- Inconsistent Deposition Parameters: Small variations in spin speed, coating time, substrate

temperature, or the volume of solution dispensed can lead to significant differences in film

thickness and morphology.[6][11]

- Solution: Carefully control all deposition parameters. For spin coating, ensure the spin coater is calibrated and the parameters are kept constant. For drop casting, control the droplet volume and the substrate temperature during evaporation.[1][6]

- Environmental Fluctuations: Changes in ambient humidity and temperature can affect solvent evaporation rates and film formation.

- Solution: Whenever possible, conduct the solution processing steps in a controlled environment, such as a nitrogen-filled glovebox.[1][4]

- 3. I'm observing a high off-current in my OFETs. How can I reduce it?

A high off-current (I\_off) leads to a low on/off ratio, which is detrimental for switching applications. This issue can arise from charge trapping at the dielectric interface or bulk leakage currents.

## Potential Causes and Solutions:

- Dielectric Surface Traps: Silanol groups (Si-OH) on the surface of SiO2 dielectrics are notorious for trapping electrons, which can contribute to a higher off-current.[8]

- Solution: As mentioned previously, treating the dielectric surface with a SAM like OTS or

HMDS is highly effective in passivating these trap states.[8][10]

- Semiconductor Film Morphology: Cracks or a very rough semiconductor film can create pathways for leakage currents.

- Solution: Optimize the deposition process to achieve a more uniform and continuous film.

Annealing the film at an optimal temperature can sometimes help to improve the

morphology and reduce defects.[6] However, excessive annealing temperatures can degrade the material.[12]

4. What is the role of post-deposition annealing and how do I optimize it?

Post-deposition annealing can be a critical step to improve the crystallinity and morphology of the **TIPS-TAP** film, thereby enhancing device mobility. However, the annealing temperature must be carefully optimized.

#### Experimental Protocol:

- Objective: To determine the optimal annealing temperature for improving TIPS-TAP film quality and OFET performance.

- Methodology:

- Fabricate a series of OFETs under identical conditions.

- Anneal different sets of devices on a hotplate at various temperatures (e.g., 50°C, 80°C, 100°C, 120°C, 150°C) for a fixed duration (e.g., 10-30 minutes) in a controlled atmosphere (e.g., nitrogen).[6][12]

- Characterize the electrical properties (mobility, on/off ratio, threshold voltage) of the annealed devices.

- Analyze the film morphology of each set using Atomic Force Microscopy (AFM) and the crystallinity using X-ray Diffraction (XRD).

- Correlate the device performance with the morphological and structural changes to identify

the optimal annealing temperature.[6] Studies have shown that for TIPS-pentacene,

annealing temperatures in the range of 50°C to 120°C can be beneficial, while higher

temperatures may lead to performance degradation.[6][12]

## **Quantitative Data Summary**

The performance of **TIPS-TAP** OFETs is highly dependent on the fabrication parameters. The following table summarizes typical mobility values achieved with different deposition techniques and solvents.

| Deposition<br>Technique     | Solvent                     | Mobility<br>(cm²/Vs)                   | On/Off Ratio | Reference |

|-----------------------------|-----------------------------|----------------------------------------|--------------|-----------|

| Drop Casting                | Toluene                     | ~0.92                                  | > 10^5       | [1]       |

| Drop Casting                | High boiling point solvents | > 1                                    | > 10^5       | [3]       |

| Dip Coating                 | Chlorobenzene               | 0.1 - 0.6                              | -            | [3]       |

| Spin Coating                | Chlorobenzene               | 0.05 - 0.2                             | -            | [3]       |

| Spin Coating                | Toluene                     | 4.5 x 10^-3<br>(annealed at<br>150°C)  | -            | [6]       |

| Spin Coating                | Tetrahydrofuran             | 1.43 x 10^-3<br>(annealed at<br>120°C) | -            | [6]       |

| Bar Coating (with PS blend) | Toluene                     | up to 1.215                            | -            | [4]       |

| Inkjet Printing             | -                           | 0.198                                  | ~1.4 x 10^5  | [12]      |

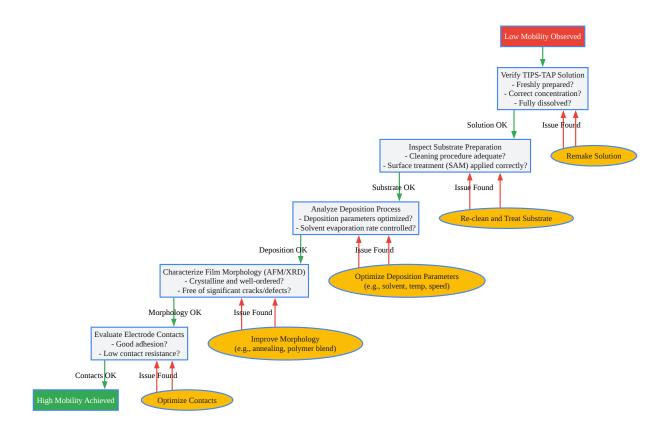

# **Troubleshooting Workflow**

The following diagram illustrates a logical workflow for troubleshooting low mobility in **TIPS-TAP** OFETs.

Click to download full resolution via product page

Caption: Troubleshooting workflow for low mobility in TIPS-TAP OFETs.

## **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. ossila.com [ossila.com]

- 2. researchgate.net [researchgate.net]

- 3. pubs.aip.org [pubs.aip.org]

- 4. Engineered molecular stacking crystallinity of bar-coated TIPS-pentacene/polystyrene films for organic thin-film transistors - RSC Advances (RSC Publishing)

DOI:10.1039/D2RA05924J [pubs.rsc.org]

- 5. Effects of TIPS-Pentacene/PS Blends on OFETs Performance and \$\text{NO}\_{2}\$ Gas Responsiveness | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 6. Optimization of 6,13Bis(triisopropylsilylethynyl)pentacene (TIPS-Pentacene) Organic Field Effect Transistor: Annealing Temperature and Solvent Effects [scirp.org]

- 7. sigmaaldrich.com [sigmaaldrich.com]

- 8. pubs.aip.org [pubs.aip.org]

- 9. Engineered molecular stacking crystallinity of bar-coated TIPS-pentacene/polystyrene films for organic thin-film transistors PMC [pmc.ncbi.nlm.nih.gov]

- 10. Fabrication and Evaluation of Organic Field-Effect Transistors (OFET) : TIPS Pentacene | Tokyo Chemical Industry Co., Ltd.(JP) [tcichemicals.com]

- 11. scielo.br [scielo.br]

- 12. repositorium.uminho.pt [repositorium.uminho.pt]

- To cite this document: BenchChem. [Troubleshooting guide for low mobility in TIPS-TAP OFETs]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b14037076#troubleshooting-guide-for-low-mobility-in-tips-tap-ofets]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com