Check Availability & Pricing

# Techniques for reducing wafer breakage during SiC processing

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                 |           |  |  |  |

|----------------------|-----------------|-----------|--|--|--|

| Compound Name:       | Silicon carbide |           |  |  |  |

| Cat. No.:            | B1214593        | Get Quote |  |  |  |

## **SiC Wafer Processing Technical Support Center**

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in mitigating wafer breakage during **Silicon Carbide** (SiC) processing.

## **Troubleshooting Guides and FAQs**

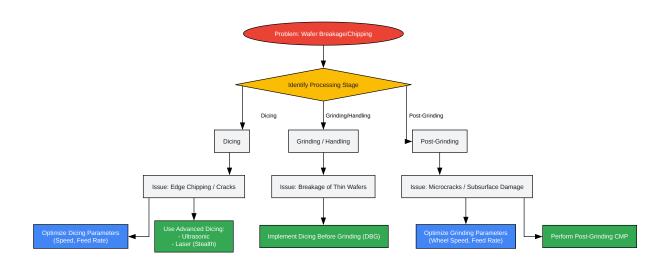

This section addresses common issues encountered during SiC wafer processing that can lead to breakage, chipping, and other defects.

Q1: We are experiencing significant edge chipping and cracking during wafer dicing. What are the likely causes and how can we resolve this?

A1: Edge chipping and cracking during dicing are common issues with SiC due to its hardness and brittle nature.[1] The primary causes are typically high mechanical stress and improper process parameters.

- Mechanical Stress: Conventional blade dicing induces significant mechanical stress, which can lead to chipping and microcracks.[2]

- Improper Parameters: High feed rates or inappropriate blade selection can exacerbate these issues.[3]

**Troubleshooting Steps:**

### Troubleshooting & Optimization

- Optimize Dicing Parameters: Reduce the feed speed and ensure the spindle speed is

optimized for your specific wafer thickness and dicing blade. For a resin-bonded blade,

optimal parameters might be a spindle speed of 20,000 rpm, a feed speed of 4 mm/s, and a

cutting depth of 0.1 mm.[3]

- Blade Selection: Ensure you are using a dicing blade appropriate for SiC. Resin-bonded blades have been shown to perform better than metal-bonded blades in some applications.

- Consider Advanced Dicing Techniques: If chipping persists, consider alternative dicing methods that impart less mechanical stress:

- Ultrasonic Dicing: This technique applies ultrasonic vibration to the blade, which reduces the processing load and can prevent chipping and cracks even at higher processing speeds (e.g., 10 mm/s).[1]

- Laser Dicing (Stealth Dicing): A laser is used to create a modified layer within the SiC, allowing for separation with minimal surface damage. This method can be significantly faster and result in higher die strength.[1][4]

- Thermal Laser Separation (TLS-Dicing<sup>™</sup>): This technique uses a laser to induce thermal stress for cleaving, which can eliminate chipping and microcracks.[5]

Q2: Our thin SiC wafers are breaking during handling and transport after backgrinding. What can we do to prevent this?

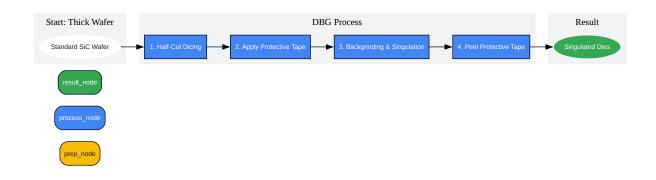

A2: Thin wafers are highly susceptible to breakage from mechanical stress. The "Dicing Before Grinding" (DBG) process is a highly effective solution to this problem.

Explanation: In a conventional workflow, the wafer is thinned first, then diced. The thinned wafer is very fragile and can easily break during transfer and dicing.[6] In the DBG process, the wafer is first partially diced (half-cut) while it is still thick and robust. Then, the wafer is thinned from the backside. The individual dies separate when the grinding depth surpasses the initial cut depth. This process avoids the handling of thin, fragile wafers, significantly reducing the risk of breakage.[7][8]

### Troubleshooting & Optimization

Recommendation: Implement a Dicing Before Grinding (DBG) workflow. This has been shown to greatly reduce wafer-level breakage and minimize backside chipping.[7][8]

Q3: We are observing microcracks and subsurface damage after the grinding process. How can we minimize this?

A3: Grinding is an abrasive process that inherently introduces stress and can create a damaged layer on the wafer surface. Optimizing grinding parameters is crucial to minimizing this damage.

#### **Troubleshooting Steps:**

- Adjust Grinding Parameters:

- Increase Grinding Wheel Speed: A higher rotational speed generally leads to increased wafer strength.[9][10]

- Decrease Feed Rate: A lower feed rate reduces the mechanical stress applied to the wafer, resulting in higher fracture strength.[9][10]

- Use Finer Grit Wheels: For the final grinding steps, use a fine-grit wheel (e.g., #2000 grit) to reduce the depth of the damaged layer. Coarse grinding (e.g., #320 grit) can create a defect layer up to 5 µm deep, while fine grinding can reduce this to around 200 nm.[11]

- Post-Grinding Treatment: Implement a post-grinding process to remove the damaged layer.

Chemical Mechanical Polishing (CMP) is highly effective at removing the stress-induced damage layer and can result in a higher bending strength for the thinned chips.[12]

Q4: We need to increase our dicing throughput without sacrificing quality. What are our options?

A4: Balancing speed and quality is a key challenge in SiC dicing. Advanced dicing technologies offer significant improvements in throughput while maintaining or even enhancing die quality.

Ultrasonic Dicing: Can increase processing speed by up to 4x compared to conventional sawing while reducing die chipping.[13]

- Stealth Dicing™: This laser-based method is significantly faster than blade dicing, with processing speeds of 350 mm/s or more per pass. It is particularly effective for high-volume production.[1] Under certain experimental conditions, it has been shown to reduce processing time by approximately 91% compared to conventional methods.[4]

- Laser Full-Cut: While it may require multiple passes, this technique's productivity improves as wafer thickness decreases, making it a strong candidate for thin SiC wafers.[4]

- Scribe and Break (SnB): This method can increase cutting speed by up to 100 times compared to conventional dicing. It also results in smoother sidewalls and can increase the number of dies per wafer by reducing the street width.[14]

#### **Data Presentation**

Table 1: Comparison of Dicing Techniques for SiC Wafers

| Dicing<br>Technique            | Typical<br>Processing<br>Speed                     | Key<br>Advantages                                                                        | Key<br>Disadvantages                                                | Die Strength                |

|--------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------|

| Conventional<br>Blade Dicing   | Low (dependent on quality requirements)            | Simple process                                                                           | High risk of<br>chipping and<br>cracks, high<br>blade wear.[5]      | Lower                       |

| Ultrasonic Dicing              | 10 mm/s[1] (up to 4x faster than conventional)[13] | Reduced<br>chipping and<br>cracks, improved<br>processing<br>quality.[1]                 | Still a mechanical process, potential for some stress.              | Higher than conventional[1] |

| Stealth Dicing™<br>(Laser)     | ≥ 350 mm/s per<br>pass[1]                          | Very high<br>throughput, high<br>die strength,<br>suitable for mass<br>production.[1][4] | May not be suitable for wafers with metal in the dicing streets.[4] | Highest[4]                  |

| TLS-Dicing™<br>(Thermal Laser) | 50 - 200 mm/s[5]                                   | No chipping or microcracks, smooth separation of backside metal.                         | Requires specific<br>laser setup.                                   | High                        |

| Scribe and Break<br>(SnB)      | Up to 100x faster<br>than dicing[14]               | Extremely fast,<br>smooth<br>sidewalls,<br>increases die<br>yield per wafer.<br>[14]     | Relies on crystal<br>cleavage<br>properties.                        | High                        |

## **Experimental Protocols**

# Protocol 1: Dicing Before Grinding (DBG) for Thin SiC Wafers

Objective: To singulate thin SiC wafers with minimal breakage and backside chipping.

#### Methodology:

- Wafer Preparation: Start with a standard thickness SiC wafer with the device side facing up.

- Half-Cut Dicing:

- Mount the wafer onto a dicing frame with appropriate dicing tape.

- Using a dicing saw, perform a partial cut along the dicing streets. The depth of this cut should be greater than the final target die thickness. For a target thickness of 50 μm, a partial cut depth of 55-60 μm is a reasonable starting point.[6]

- Use a spindle revolution of 40k to 50k rpm to achieve good top-side chipping performance.

[6]

- Protective Lamination: Apply a protective backgrinding tape over the device side of the wafer, covering the half-cut streets.

- Backgrinding:

- Mount the wafer, device side down, onto the grinder chuck.

- Grind the backside of the wafer. The grinding process will remove material until the thickness is reduced to the final target.

- As the grinder thins the wafer past the depth of the half-cuts, the individual dies will be singulated.

- Tape Removal:

- Mount the singulated dies, still on the protective tape, to a mounter.

- Gently peel off the protective grinding tape to release the individual dies.

### **Protocol 2: Ultrasonic-Assisted Dicing of SiC Wafers**

Objective: To improve dicing quality and throughput by reducing mechanical stress.

#### Methodology:

- Equipment Setup:

- Use a dicing saw equipped with an ultrasonic-wave unit.

- Ensure the ultrasonic power can be effectively delivered to the dicing blade.[13]

- Wafer Mounting: Mount the SiC wafer on a standard dicing frame and tape.

- Dicing Parameters:

- Blade Selection: Choose a blade optimized for ultrasonic dicing of SiC.

- Ultrasonic Power: Apply ultrasonic power to the blade during the dicing process. The specific frequency and amplitude will depend on the equipment and wafer characteristics.

- Feed Speed: A higher feed speed (e.g., up to 10 mm/s) can be used compared to conventional dicing due to the reduced processing load.[1]

- Spindle Speed: Adjust the spindle speed as recommended for the specific blade and ultrasonic setup.

- Coolant: Ensure adequate deionized water flow to the processing point to cool the blade and workpiece and remove debris.[1]

- Execution: Perform the dicing process through the entire thickness of the wafer.

- Post-Dicing Cleaning: Clean the singulated dies to remove any remaining particles.

# Visualizations Troubleshooting Workflow for SiC Wafer Breakage

Click to download full resolution via product page

Caption: Troubleshooting workflow for SiC wafer breakage.

# Experimental Workflow for Dicing Before Grinding (DBG)

Click to download full resolution via product page

Caption: Workflow for the Dicing Before Grinding (DBG) process.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. disco.co.jp [disco.co.jp]

- 2. researchgate.net [researchgate.net]

- 3. pubs.aip.org [pubs.aip.org]

- 4. disco.co.jp [disco.co.jp]

- 5. 3d-micromac.com [3d-micromac.com]

- 6. cmapspublic.ihmc.us [cmapspublic.ihmc.us]

- 7. DBG (Dicing Before Grinding) Process | DBG (Dicing Before Grinding) Process |

DBG/SDBG | Solutions | DISCO CORPORATION [disco.co.jp]

- 8. Dicing Before Grinding (DBG) | DISCO Technology Advancing the Cutting Edge [technology.discousa.com]

- 9. researchgate.net [researchgate.net]

- 10. Impacts of back-grinding process parameters on the strength of thinned silicon wafer |

Semantic Scholar [semanticscholar.org]

- 11. researchgate.net [researchgate.net]

- 12. researchgate.net [researchgate.net]

- 13. csmantech.org [csmantech.org]

- 14. eetimes.com [eetimes.com]

- To cite this document: BenchChem. [Techniques for reducing wafer breakage during SiC processing]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1214593#techniques-for-reducing-wafer-breakage-during-sic-processing]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com