# **Technical Support Center: WTe2 Device Performance and Substrate Effects**

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                           |           |

|----------------------|---------------------------|-----------|

| Compound Name:       | Tungsten telluride (WTe2) |           |

| Cat. No.:            | B082480                   | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions for researchers and scientists working with Tungsten Ditelluride (WTe<sub>2</sub>) devices. The following information addresses common issues encountered during experimentation, with a focus on the influence of different substrates on device performance.

## Frequently Asked Questions (FAQs)

Q1: What are the most common substrates used for WTe2 device fabrication?

A1: The most commonly used substrates for WTe<sub>2</sub> device fabrication are silicon dioxide (SiO<sub>2</sub>), hexagonal boron nitride (h-BN), sapphire, and flexible substrates like poly(methyl methacrylate) (PMMA). The choice of substrate significantly impacts the material's properties and the final device performance.

Q2: How does the substrate affect the electronic properties of WTe<sub>2</sub>?

A2: The substrate can influence the electronic properties of WTe<sub>2</sub> through several mechanisms. Substrate-induced strain can alter the band structure of WTe<sub>2</sub>. The dielectric environment of the substrate affects carrier scattering and mobility. For instance, h-BN is known to provide a cleaner and more uniform interface, reducing charge trapping and leading to higher carrier mobility compared to SiO<sub>2</sub>.

Q3: Why is h-BN often preferred as a substrate or encapsulation layer for WTe2 devices?

A3: Hexagonal boron nitride (h-BN) is an atomically flat, insulating material with a low density of dangling bonds and trapped charges. When used as a substrate or encapsulation layer, h-BN minimizes substrate-induced scattering and provides a clean dielectric environment, which can significantly enhance the carrier mobility and overall performance of WTe<sub>2</sub> devices.[1] Encapsulation with h-BN also protects the WTe<sub>2</sub> from degradation in ambient conditions.

Q4: What is the impact of substrate choice on the thermal properties of WTe2 devices?

A4: The substrate plays a crucial role in heat dissipation from WTe<sub>2</sub> devices. The thermal conductivity of the substrate material affects the operating temperature of the device. Studies have shown that the thermal conductivity of WTe<sub>2</sub> can vary depending on the substrate, with higher thermal conductivity observed on substrates like SiO<sub>2</sub>/Si compared to PMMA.[2][3]

Q5: Can WTe2 be grown directly on different substrates?

A5: Yes, WTe<sub>2</sub> can be grown on various substrates using techniques like chemical vapor deposition (CVD). The choice of substrate can influence the growth dynamics, crystal quality, and morphology of the resulting WTe<sub>2</sub> films. For example, the formation of continuous WTe<sub>2</sub> films can be more challenging on SiO<sub>2</sub> compared to sapphire substrates.

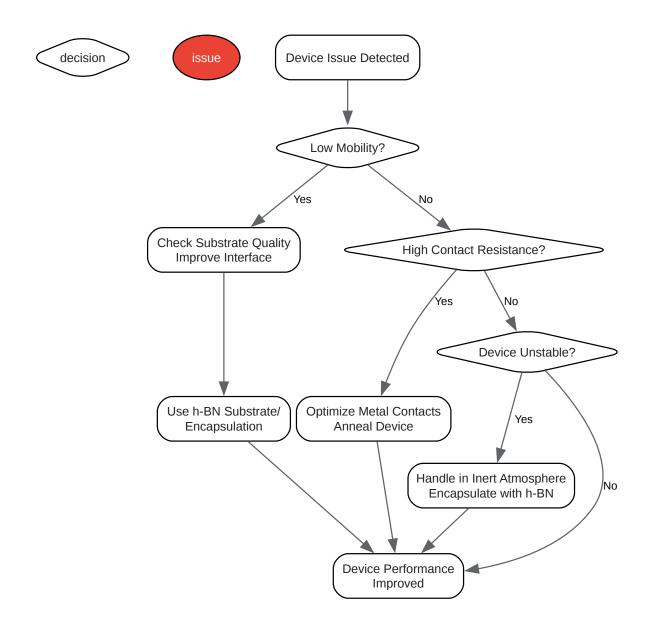

### **Troubleshooting Guide**

Problem 1: My WTe2 device performance degrades quickly when exposed to air.

- Question: Why is my WTe2 device unstable in ambient conditions, and how can I prevent this?

- Answer: WTe<sub>2</sub> is known to be sensitive to air and can oxidize, leading to a rapid degradation of its electronic properties. This is a common issue, especially for thin-layer WTe<sub>2</sub>. To prevent this, it is crucial to handle and process WTe<sub>2</sub> in an inert atmosphere (e.g., a glovebox). For long-term stability, encapsulating the WTe<sub>2</sub> flake with an inert material like hexagonal boron nitride (h-BN) is a highly effective strategy. Another approach is to use a capping layer, such as a thin layer of PHPS which can be converted to SiO<sub>2</sub>.

Problem 2: I'm observing low carrier mobility in my WTe2 device on a SiO2 substrate.

### Troubleshooting & Optimization

- Question: What are the potential reasons for low mobility in my WTe2 device on SiO2, and how can I improve it?

- Answer: Low carrier mobility on SiO<sub>2</sub> substrates is often attributed to charge traps and surface roughness at the SiO<sub>2</sub>/WTe<sub>2</sub> interface, which can lead to increased carrier scattering. To improve mobility, consider the following:

- Substrate Cleaning: Ensure the SiO<sub>2</sub> substrate is meticulously cleaned to remove any organic residues or contaminants before WTe<sub>2</sub> transfer.

- Annealing: Annealing the device after fabrication can sometimes improve the interface quality and reduce scattering.

- h-BN Encapsulation: The most effective method to significantly boost mobility is to use an h-BN substrate or fully encapsulate the WTe<sub>2</sub> flake with h-BN. This provides a much cleaner and smoother interface.

Problem 3: I'm having difficulty achieving good ohmic contacts to my WTe2 device.

- Question: What are the common causes of high contact resistance in WTe2 devices, and what are the solutions?

- Answer: High contact resistance is a frequent challenge in fabricating 2D material devices and can arise from several factors, including the presence of a Schottky barrier at the metal-WTe<sub>2</sub> interface, contamination at the contact region, or a van der Waals gap between the metal and WTe<sub>2</sub>. To achieve better ohmic contacts:

- Metal Selection: Choose metals with appropriate work functions to minimize the Schottky barrier height.

- Interface Cleaning: Ensure the WTe<sub>2</sub> surface is clean before metal deposition. An in-situ argon plasma cleaning step can sometimes be used, but with caution to avoid damaging the WTe<sub>2</sub>.

- Contact Annealing: Post-deposition annealing can promote better adhesion and interdiffusion at the metal-WTe2 interface, potentially lowering the contact resistance.

### Troubleshooting & Optimization

2D Metal Contacts: Using another 2D material, like graphene or a metallic transition metal dichalcogenide, as a contact material can sometimes lead to improved, cleaner interfaces and lower contact resistance.

Problem 4: My WTe<sub>2</sub> device on a SiO<sub>2</sub> substrate shows significant gate leakage current.

- Question: What causes high gate leakage in my WTe2 device, and how can I reduce it?

- Answer: High gate leakage current in a field-effect transistor can be due to a thin or poorquality gate dielectric. While thermally grown SiO<sub>2</sub> is generally a good insulator, defects or pinholes in the oxide layer can lead to leakage.[5] To address this:

- Dielectric Quality: Verify the quality of your SiO<sub>2</sub> layer. You can test the leakage current of the bare SiO<sub>2</sub>/Si wafer before device fabrication.

- Thicker Dielectric: Using a thicker SiO<sub>2</sub> layer can reduce leakage, but it will also decrease the gate capacitance, requiring higher gate voltages for device operation.

- Alternative Dielectrics: Consider using alternative high-quality dielectrics like h-BN, which can provide excellent insulation even at a few nanometers thickness.

Problem 5: My WTe<sub>2</sub> device has failed unexpectedly during measurement.

- Question: What are the common failure modes for WTe2 devices under electrical stress?

- Answer: WTe<sub>2</sub> devices can fail under high electrical stress primarily due to thermal overload.

[6] The high current density can lead to significant Joule heating, and if the heat is not dissipated effectively through the substrate, it can cause the WTe<sub>2</sub> to break down.

[7] To mitigate this:

- Current Limiting: Use a current compliance in your measurement setup to prevent excessive current flow.

- Substrate Choice: Substrates with higher thermal conductivity can help in dissipating heat more effectively.

- Device Geometry: The geometry of the device can also influence heat dissipation.

## **Quantitative Data Presentation**

The following table summarizes key performance metrics of WTe<sub>2</sub> devices on different substrates. Note that these values are compiled from various sources, and direct comparison should be made with caution as experimental conditions may vary.

| Substrate | Carrier<br>Mobility<br>(cm²/Vs) | On/Off Ratio | Contact<br>Resistance<br>(kΩ·μm) | Notes                                                                         |

|-----------|---------------------------------|--------------|----------------------------------|-------------------------------------------------------------------------------|

| SiO2      | ~10 - 1,000                     | ~1 - 10      | ~10 - 100                        | Performance is highly sensitive to interface quality and WTe2 thickness.      |

| h-BN      | > 1,000 -<br>167,000            | > 10         | ~1 - 10                          | h-BN encapsulation significantly reduces scattering and improves mobility.[8] |

| РММА      | Lower than SiO2                 | -            | -                                | Lower thermal conductivity can be a limiting factor.[2][3]                    |

| Sapphire  | -                               | -            | -                                | Can promote better quality growth of WTe2 compared to SiO2.                   |

# **Experimental Protocols**

# Protocol 1: Fabrication of Exfoliated WTe<sub>2</sub> Device on SiO<sub>2</sub> Substrate

- Substrate Preparation:

- Start with a highly doped silicon wafer with a 285-300 nm thermally grown SiO2 layer.

- Clean the substrate by sonicating in acetone, then isopropanol, each for 5 minutes.

- Dry the substrate with a nitrogen gun.

- Perform an oxygen plasma ash for 3-5 minutes to remove any remaining organic residues.

- Mechanical Exfoliation of WTe2:

- Use high-quality WTe2 bulk crystals.

- Cleave the crystal using dicing tape to expose a fresh surface.

- Gently press a piece of blue Nitto tape onto the freshly cleaved surface.

- Repeatedly peel the tape apart to thin the crystal.

- Press the tape with the thin WTe2 flakes onto the cleaned SiO2/Si substrate.

- Slowly peel back the tape, leaving behind exfoliated WTe2 flakes of varying thicknesses.

- Flake Identification and Characterization:

- Use an optical microscope to locate thin WTe<sub>2</sub> flakes. Monolayer and few-layer flakes have a distinct optical contrast.

- Use Atomic Force Microscopy (AFM) to confirm the thickness of the desired flakes.

- Device Patterning and Metallization:

- Spin-coat a layer of electron-beam resist (e.g., PMMA) over the substrate.

- Use electron-beam lithography (EBL) to define the source and drain electrode patterns over the selected WTe<sub>2</sub> flake.

- Develop the resist to create openings for metal deposition.

- Immediately transfer the sample to a high-vacuum electron-beam evaporator.

- Deposit a metal stack for the contacts (e.g., 5 nm Cr / 50 nm Au).

- Perform lift-off in a suitable solvent (e.g., acetone) to remove the excess metal and resist, leaving the patterned electrodes.

- Device Annealing (Optional):

- Anneal the device in a vacuum or inert atmosphere (e.g., Ar/H<sub>2</sub>) at 150-200°C for a few hours to improve contact quality.

# Protocol 2: Fabrication of h-BN Encapsulated WTe<sub>2</sub> Device

- Substrate and Material Preparation:

- Prepare a SiO<sub>2</sub>/Si substrate as described in Protocol 1.

- Exfoliate WTe2 and h-BN flakes onto separate SiO2/Si substrates.

- Creating the h-BN/WTe<sub>2</sub>/h-BN Stack (Dry Transfer):

- This process is typically done using a micromanipulator setup with a glass slide coated with a polymer stamp (e.g., PPC or PDMS).

- Pick up the top h-BN: Bring the polymer stamp into contact with a suitable top h-BN flake and slowly retract to pick it up.

- Pick up the WTe<sub>2</sub>: Align the top h-BN flake over the desired WTe<sub>2</sub> flake and bring them into contact. The van der Waals forces will cause the WTe<sub>2</sub> to adhere to the h-BN.

- Pick up the bottom h-BN: Similarly, pick up a suitable bottom h-BN flake.

- Release the stack: Align the completed h-BN/WTe<sub>2</sub>/h-BN stack over the target area on the final device substrate and gently bring it into contact. Slowly heat the substrate to release the stack from the polymer stamp.

- Device Patterning and Metallization:

- Follow the same EBL and metallization steps as described in Protocol 1 to define the source and drain contacts to the encapsulated WTe2. It is common to use an etching step (e.g., with CHF3/O2 plasma) to create contact vias through the top h-BN layer before metal deposition.

#### **Visualizations**

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

• 1. researchgate.net [researchgate.net]

- 2. substrate-dependent-thermal-conductivity-in-td-wte2-using-micro-raman-spectroscopy -Ask this paper | Bohrium [bohrium.com]

- 3. researchgate.net [researchgate.net]

- 4. researchgate.net [researchgate.net]

- 5. arxiv.org [arxiv.org]

- 6. Common Failure Modes in Power Semiconductors [eureka.patsnap.com]

- 7. researchgate.net [researchgate.net]

- 8. Troubleshooting Chapter Three. Failure Modes. [angelfire.com]

- To cite this document: BenchChem. [Technical Support Center: WTe2 Device Performance and Substrate Effects]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b082480#effects-of-substrate-on-wte2-device-performance]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com