# Technical Support Center: Troubleshooting Low Carrier Lifetime in SiC Materials

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                 |           |

|----------------------|-----------------|-----------|

| Compound Name:       | Silicon carbide |           |

| Cat. No.:            | B1214593        | Get Quote |

Welcome to the technical support center for troubleshooting low carrier lifetime in **Silicon Carbide** (SiC) materials. This resource is designed for researchers, scientists, and engineers working with SiC to provide clear, actionable guidance on identifying and resolving issues related to reduced carrier lifetime in their experiments.

## Frequently Asked Questions (FAQs)

Q1: What is carrier lifetime and why is it important in SiC?

A1: Carrier lifetime is the average time an excess minority carrier exists before recombining with a majority carrier. In SiC devices, particularly bipolar devices like PiN diodes and IGBTs, a long carrier lifetime is crucial for achieving low on-state resistance and reducing conduction losses through a phenomenon known as conductivity modulation.[1] However, for high-frequency switching applications, a shorter, controlled lifetime may be desirable to minimize switching losses.

Q2: What are the primary causes of low carrier lifetime in our 4H-SiC epilayers?

A2: Low carrier lifetime in 4H-SiC is predominantly caused by defects within the material that act as recombination centers. The most significant of these are:

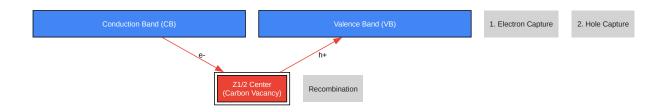

• Point Defects: The Z1/2 center, which is associated with carbon vacancies (VC), is widely recognized as the primary lifetime-killing defect in n-type 4H-SiC.[1][2][3][4] Other deep-level defects can also contribute to recombination.

- Extended Defects: Dislocations and stacking faults can also act as recombination sites, locally reducing carrier lifetime.

- Surface Recombination: Recombination of carriers at the surface of the SiC wafer or at the interface between the epilayer and the substrate can be a significant factor, especially in materials with low bulk defect concentrations.[5][6]

Q3: We are observing a shorter-than-expected carrier lifetime in our as-grown SiC wafers. What should be our initial troubleshooting steps?

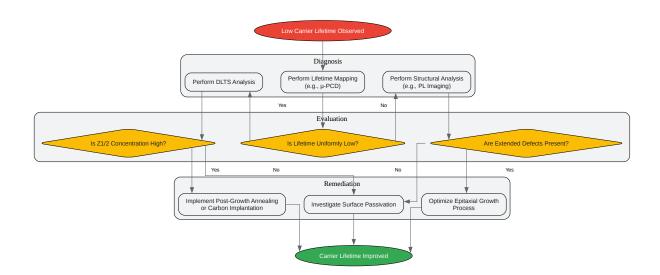

A3: A logical first step is to characterize the material to identify the dominant recombination mechanism. We recommend the following approach:

- Initial Lifetime Measurement: Perform a non-destructive, wafer-level carrier lifetime measurement using a technique like Microwave Photoconductivity Decay (μ-PCD) to confirm the low lifetime and map its uniformity across the wafer.

- Defect Spectroscopy: Employ Deep Level Transient Spectroscopy (DLTS) to identify and quantify the concentration of deep-level defects, particularly the Z1/2 center. A high concentration of this defect is a strong indicator of the cause of the low lifetime.

- Structural Defect Analysis: Use techniques like photoluminescence (PL) imaging or X-ray topography to identify the presence and density of extended defects such as stacking faults and dislocations.

This initial characterization will help you determine whether the issue is primarily related to point defects, extended defects, or potentially surface-related issues.

## **Troubleshooting Guides**

## Issue 1: Low Carrier Lifetime Correlated with High Z1/2 Defect Concentration

If DLTS analysis reveals a high concentration of the Z1/2 center (typically >  $1 \times 10^{13}$  cm<sup>-3</sup>), this is the most likely cause of the reduced carrier lifetime.

Recommended Actions:

- Post-Growth Annealing: High-temperature annealing in an appropriate atmosphere can reduce the concentration of carbon vacancies. The effectiveness of annealing is temperature-dependent.

- Carbon Implantation followed by Annealing: Introducing excess carbon into the near-surface region through ion implantation, followed by a high-temperature anneal, can effectively annihilate carbon vacancies and significantly increase carrier lifetime.[2][3]

- Thermal Oxidation: A high-temperature oxidation process can also lead to a reduction in the Z1/2 center concentration and an improvement in carrier lifetime.[1]

| Treatment Method                | Typical<br>Annealing/Process<br>Temperature (°C) | Resulting Carrier<br>Lifetime<br>Improvement                                   | Reference |

|---------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------|-----------|

| High-Temperature<br>Annealing   | 1600 - 1750                                      | Can increase or decrease Z1/2 concentration depending on initial concentration | [7]       |

| Carbon Implantation + Annealing | >1600                                            | Can significantly increase carrier lifetime                                    | [2]       |

| Thermal Oxidation               | 1100 - 1400                                      | Can lead to a significant increase in carrier lifetime                         | [1][8]    |

| Hydrogen Annealing              | High Temperature                                 | Can significantly reduce carbon vacancy defects                                | [8]       |

### **Issue 2: Spatially Non-Uniform Low Carrier Lifetime**

If lifetime mapping reveals localized areas of very low lifetime, this often points to the influence of extended defects.

**Recommended Actions:**

- Correlative Analysis: Compare the lifetime map with PL imaging or defect etching to correlate

the low lifetime regions with specific extended defects like stacking faults or dislocation

clusters.

- Epitaxial Growth Optimization: Review and optimize the epitaxial growth process. Factors such as C/Si ratio, growth temperature, and substrate quality can influence the formation of extended defects.

- Substrate Inspection: The quality of the SiC substrate is critical, as defects in the substrate can propagate into the epitaxial layer.

## **Experimental Protocols**

## Time-Resolved Photoluminescence (TRPL) for Carrier Lifetime Measurement

Time-Resolved Photoluminescence (TRPL) is a powerful non-destructive optical technique to measure the minority carrier lifetime. It involves exciting the SiC sample with a short-pulsed laser and measuring the decay of the subsequent photoluminescence signal over time.

#### Materials and Equipment:

- Pulsed laser source with a wavelength that can generate carriers in SiC (e.g., UV laser).

- Optical system for focusing the laser onto the sample and collecting the emitted luminescence.

- Monochromator to select the desired luminescence wavelength.

- Fast photodetector (e.g., photomultiplier tube or avalanche photodiode).

- Time-correlated single-photon counting (TCSPC) system or a fast oscilloscope.

- Cryostat for temperature-dependent measurements (optional).

#### Procedure:

• Sample Preparation: Ensure the surface of the SiC wafer is clean and free of contaminants.

#### · System Setup:

- Align the laser to excite the desired area on the sample.

- Position the collection optics to efficiently gather the photoluminescence.

- Set the monochromator to the band-edge emission wavelength of 4H-SiC (around 390 nm).

#### Data Acquisition:

- Excite the sample with a short laser pulse.

- Record the decay of the photoluminescence intensity over time using the TCSPC system or oscilloscope.

- Accumulate the signal for a sufficient duration to achieve a good signal-to-noise ratio.

#### Data Analysis:

- The recorded decay curve is typically fitted with an exponential function (or a sum of exponentials) to extract the decay time constant, which corresponds to the carrier lifetime.

- For non-exponential decays, more complex models may be needed to account for different recombination mechanisms.

## Deep Level Transient Spectroscopy (DLTS) for Defect Characterization

DLTS is a highly sensitive technique for detecting and characterizing deep-level defects in semiconductors. It involves measuring the capacitance transient of a Schottky diode or a p-n junction at different temperatures.

#### Materials and Equipment:

SiC sample with a fabricated Schottky contact or p-n junction.

- Cryostat with a temperature controller (capable of scanning from low temperatures, e.g., 77

K, to high temperatures, e.g., 700 K).

- · Capacitance meter.

- Pulse generator.

- DLTS signal processing unit (or a system that integrates these components).

#### Procedure:

- Sample Preparation: Fabricate Schottky diodes on the SiC epilayer. This typically involves metal deposition (e.g., Ni, Ti) to form the Schottky contact and a backside ohmic contact.

- System Setup:

- Mount the sample in the cryostat.

- Connect the Schottky diode to the capacitance meter and pulse generator.

- · Measurement:

- Apply a reverse bias to the Schottky diode to create a depletion region.

- Apply a filling pulse (reducing the reverse bias or applying a forward bias) to fill the deep levels with majority carriers.

- Return to the initial reverse bias and record the capacitance transient as the trapped carriers are thermally emitted.

- Repeat this process while sweeping the temperature of the sample.

- Data Analysis:

- The capacitance transient data is processed to generate a DLTS spectrum, which shows peaks corresponding to different deep levels.

- From the peak positions at different rate windows, an Arrhenius plot can be constructed to determine the activation energy (energy level) and capture cross-section of the defect.

- The peak height is proportional to the defect concentration.

### **Visualizations**

Check Availability & Pricing

#### Click to download full resolution via product page

Caption: Troubleshooting workflow for low carrier lifetime in SiC.

Click to download full resolution via product page

Caption: Recombination pathway via the Z1/2 center in 4H-SiC.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. powerwaywafer.com [powerwaywafer.com]

- 2. research-collection.ethz.ch [research-collection.ethz.ch]

- 3. pubs.aip.org [pubs.aip.org]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. apps.dtic.mil [apps.dtic.mil]

- 7. pubs.aip.org [pubs.aip.org]

- 8. [2411.10777] Prolonging Carrier Lifetime in P-type 4H-SiC Epilayer by Thermal Oxidation and Hydrogen Annealing [arxiv.org]

- To cite this document: BenchChem. [Technical Support Center: Troubleshooting Low Carrier Lifetime in SiC Materials]. BenchChem, [2025]. [Online PDF]. Available at:

[https://www.benchchem.com/product/b1214593#troubleshooting-low-carrier-lifetime-in-sic-materials]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com