# Technical Support Center: SiC Film Deposition from TMS Precursors

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                   |           |

|----------------------|-------------------|-----------|

| Compound Name:       | Tetramethylsilane |           |

| Cat. No.:            | B1202638          | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with silicon carbide (SiC) film deposition using trimethylsilane (TMS) precursors. The information is designed to help users identify and resolve issues related to void formation in their experiments.

## **Troubleshooting Guide: Void Formation**

Question: We are observing significant void formation at the SiC/Si interface in our films grown using a TMS precursor. What are the primary causes?

#### Answer:

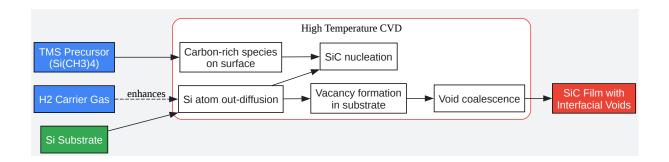

Void formation at the SiC/Si interface is a common issue when using TMS as a precursor for SiC film growth on a silicon substrate. The primary mechanism is the out-diffusion of silicon atoms from the substrate.[1][2] This occurs because the carbon-rich environment created by the decomposition of TMS promotes the reaction of surface silicon atoms to form SiC nuclei. The depletion of silicon from the substrate leads to the formation of vacancies, which then coalesce into voids.[1][2]

Several factors can exacerbate this issue:

High Growth Temperatures: Elevated temperatures increase the rate of silicon out-diffusion, leading to a higher density and size of voids.[3][4][5]

## Troubleshooting & Optimization

- Inadequate Surface Preparation: Defects on the silicon substrate, such as those related to oxygen, can act as nucleation sites for void formation.[1][6]

- Sub-optimal Process Parameters: The flow rate of TMS, the carrier gas (typically H<sub>2</sub>), the heating ramp rate, and the pressure within the reactor all play a crucial role in film quality and void formation.[7][8]

Question: What steps can we take to minimize or eliminate void formation in our SiC films?

#### Answer:

To mitigate void formation, a multi-faceted approach focusing on process optimization and substrate preparation is necessary. Here are some recommended strategies:

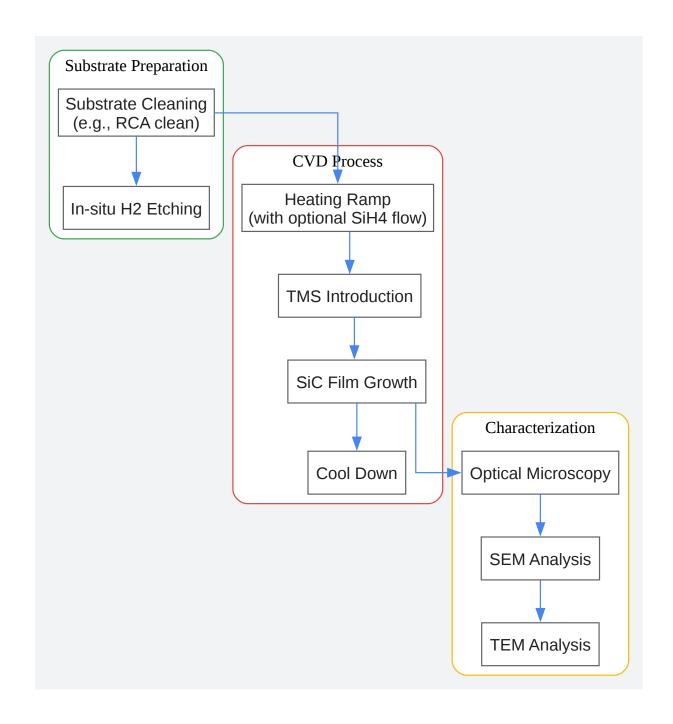

- Optimize the Heating Procedure: Instead of pre-heating the substrate to the growth temperature before introducing TMS, consider introducing the TMS flow at a lower temperature and then ramping up to the desired growth temperature. A slower heating ramp, particularly at temperatures above 1250°C, can help reduce the formation of voids.[1]

- Adjust the TMS Flow Rate: Increasing the TMS flow rate can sometimes lead to the growth

of void-free SiC films.[8] However, this must be balanced, as an excessively high flow rate

can negatively impact the crystallinity of the film, potentially leading to polycrystalline growth.

[8]

- Control the Growth Temperature: Lowering the substrate temperature can effectively reduce the rate of silicon out-diffusion. Void-free single crystalline SiC films have been successfully grown at temperatures below 1000°C.[4]

- Introduce a Silicon Source During Carbonization: The introduction of a silicon-containing gas, such as silane (SiH<sub>4</sub>), during the initial carbonization step can create a silicon overpressure.

This helps to suppress the out-diffusion of silicon from the substrate, thereby significantly reducing or even eliminating void formation.[1]

- Thorough Substrate Surface Preparation: Ensure the silicon substrate is meticulously cleaned to remove any contaminants and native oxide layers. In-situ etching with hydrogen (H<sub>2</sub>) prior to deposition can help create a pristine surface, although the etching process itself

must be carefully controlled to avoid creating excessive etch pits that can act as void nucleation sites.[1][9]

Utilize a Buffer Layer: The growth of a thin, high-quality buffer layer prior to the main SiC film deposition can help to accommodate the lattice mismatch between SiC and Si and can reduce the density of defects, including interfacial voids.[10]

# **Frequently Asked Questions (FAQs)**

Q1: What is the underlying mechanism of void formation when using TMS?

A1: The decomposition of the TMS precursor creates a carbon-rich environment on the silicon substrate surface. This abundance of carbon drives a reaction with the silicon atoms on the substrate to form SiC nuclei. To fuel the growth of these nuclei, more silicon atoms diffuse out from the substrate, leaving behind vacancies. These vacancies agglomerate to form microscopic voids at the interface between the SiC film and the silicon substrate.[1][2]

Q2: How does the temperature affect the shape and size of the voids?

A2: The growth temperature has a significant impact on both the size and shape of the voids. Higher temperatures provide more energy for silicon atoms to diffuse out of the substrate, which can lead to the formation of larger voids.[3][4][5] The shape of the voids is determined by the crystallography of the silicon substrate and the energetically favorable planes at a given temperature. For example, on Si(111) substrates, triangular voids are often observed at lower temperatures (e.g., 850°C), while hexagonal shapes may appear at higher temperatures (e.g., 1050°C) as higher energy facets become more stable.[3][4][5]

Q3: Can the carrier gas influence void formation?

A3: Yes, the carrier gas, which is often hydrogen (H<sub>2</sub>), can influence void formation. Hydrogen can etch the silicon surface at high temperatures, creating etch pits. These pits can then serve as preferential sites for the initiation of voids.[1] Therefore, optimizing the H<sub>2</sub> flow rate and the pre-deposition etching step is crucial for achieving a smooth interface with minimal voids. Reducing the H<sub>2</sub> flow rate can sometimes increase the filling rate in trench structures and reduce the risk of void formation.[11]

Q4: What techniques can be used to characterize and analyze void formation?

A4: Several microscopy techniques are essential for characterizing voids in SiC films:

- Optical Microscopy: Can be used for a preliminary inspection of the SiC/Si interface, as the SiC film is transparent. Voids are often visible with this technique.[3][9]

- Scanning Electron Microscopy (SEM): Provides high-resolution images of the surface morphology of the SiC film. It is particularly useful for observing voids on patterned substrates or after the SiC film has been removed.[1][9]

- Transmission Electron Microscopy (TEM): Offers cross-sectional views of the SiC/Si interface, allowing for detailed analysis of the size, shape, and distribution of voids.[2][4][5]

## **Data Summary**

The following table summarizes the influence of key experimental parameters on void formation in SiC films grown from TMS precursors.

| Parameter              | Influence on Void<br>Formation                                                                              | Recommended Action for<br>Void Reduction                                                                                      |

|------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Growth Temperature     | Higher temperatures increase<br>Si out-diffusion, leading to<br>more and larger voids.[3][4][5]             | Lower the growth temperature, ideally below 1000°C.[4]                                                                        |

| TMS Flow Rate          | Increasing the flow rate can lead to void-free films, but excessive flow may reduce crystallinity.[8]       | Optimize the flow rate to achieve a balance between a void-free interface and good film quality.                              |

| Heating Ramp Rate      | A rapid heating ramp to high temperatures can promote void formation.[1]                                    | Employ a slower, controlled heating ramp, especially at temperatures above 1250°C. [1]                                        |

| Carrier Gas (H₂) Flow  | High H <sub>2</sub> flow can lead to<br>surface etching and the<br>creation of void nucleation<br>sites.[1] | Optimize the H <sub>2</sub> flow rate to<br>minimize surface etching while<br>maintaining a stable deposition<br>process.[11] |

| Substrate Surface      | Surface defects and contaminants act as nucleation sites for voids.[1][6]                                   | Ensure meticulous cleaning<br>and preparation of the Si<br>substrate before growth.[9]                                        |

| Silane (SiH4) Addition | The absence of a gas-phase Si source encourages Si out- diffusion from the substrate.                       | Introduce a controlled flow of SiH4 during the initial carbonization to suppress Si out-diffusion.[1]                         |

# **Experimental Protocols**

Methodology for Characterizing Voids in SiC Films

- Initial Inspection with Optical Microscopy:

- Place the SiC-on-Si wafer on the stage of a differential interference contrast (DIC) or Nomarski microscope.

- Since the SiC film is transparent, focus through the film to the SiC/Si interface.

- Scan the sample to get a qualitative assessment of the presence, density, and distribution

of voids across the wafer.

- Surface and Interface Morphology with Scanning Electron Microscopy (SEM):

- For plan-view analysis, a small piece of the wafer can be directly mounted on an SEM stub using carbon tape.

- To observe the voids at the interface more clearly, the SiC film can be chemically or mechanically removed.

- For cross-sectional analysis, the wafer piece needs to be cleaved or prepared using a focused ion beam (FIB) to expose the SiC/Si interface.

- The sample is then mounted vertically on an SEM stub.

- Obtain images at various magnifications to analyze the shape and size of the voids.

- Detailed Structural Analysis with Transmission Electron Microscopy (TEM):

- Prepare a thin cross-sectional lamella of the SiC/Si interface using standard TEM sample preparation techniques, such as mechanical polishing followed by ion milling or using a FIB.

- The lamella should be electron-transparent (typically <100 nm thick).

- Perform bright-field and dark-field imaging in the TEM to visualize the voids and other crystalline defects at the interface.

- High-resolution TEM (HRTEM) can be used to study the atomic structure of the interface and the facets of the voids.

## **Visualizations**

Click to download full resolution via product page

Caption: Experimental workflow for SiC film deposition and characterization.

#### Click to download full resolution via product page

Caption: Signaling pathway illustrating the mechanism of void formation.

## **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. publications.cnr.it [publications.cnr.it]

- 2. scilit.com [scilit.com]

- 3. ias.ac.in [ias.ac.in]

- 4. uni-ulm.de [uni-ulm.de]

- 5. researchgate.net [researchgate.net]

- 6. raw.githubusercontent.com [raw.githubusercontent.com]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- 9. researchgate.net [researchgate.net]

- 10. tms.org [tms.org]

- 11. DOT Language | Graphviz [graphviz.org]

- To cite this document: BenchChem. [Technical Support Center: SiC Film Deposition from TMS Precursors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1202638#troubleshooting-void-formation-in-sic-films-from-tms-precursors]

### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com