# Technical Support Center: Reducing Stacking Faults in Cadmium Telluride (CdTe) Thin Films

Author: BenchChem Technical Support Team. Date: December 2025

This technical support center provides troubleshooting guidance and answers to frequently asked questions for researchers, scientists, and drug development professionals working with Cadmium Telluride (CdTe) thin films. The focus is on understanding and mitigating stacking faults to improve device performance.

# **Frequently Asked Questions (FAQs)**

Q1: What are stacking faults in CdTe thin films and why are they problematic?

A1: Stacking faults are crystallographic defects, or irregularities, in the stacking sequence of atomic planes within the CdTe crystal lattice. In as-deposited CdTe thin films, these defects are present in high densities.[1][2] They are problematic because they can act as charge carrier traps, which hinders the collection of photo-generated carriers and limits the overall efficiency of photovoltaic devices.[2][3][4] Some higher-energy stacking faults are predicted to be hole traps.[2][3][4]

Q2: What is the most effective method for removing stacking faults in CdTe thin films?

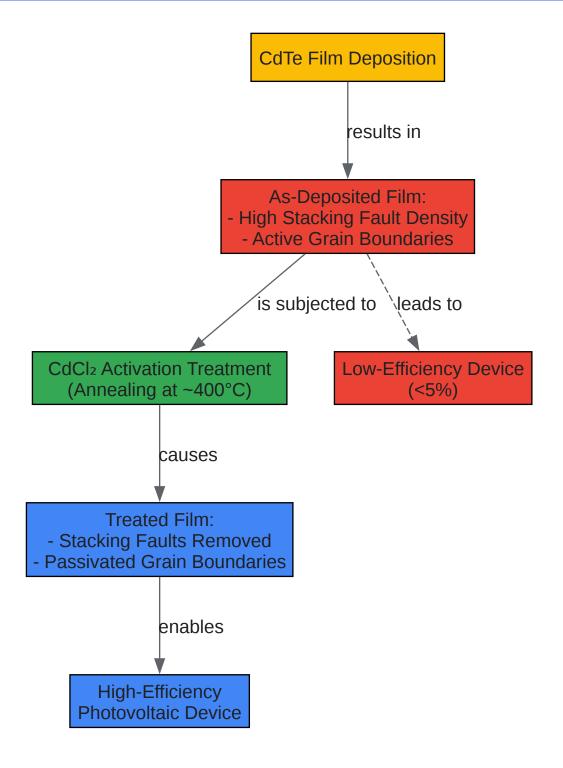

A2: The most crucial and widely documented method for removing stacking faults is a post-deposition annealing treatment in the presence of Cadmium Chloride (CdCl<sub>2</sub>).[1][2][3][4] This "activation" process is essential for producing high-efficiency CdTe solar cells.[2][3][4][5]

Q3: How does the Cadmium Chloride (CdCl<sub>2</sub>) treatment work to remove stacking faults?

A3: During the CdCl<sub>2</sub> treatment at elevated temperatures (typically around 400-420°C), chlorine diffuses into the CdTe layer, with a notable presence along the grain boundaries.[1][6][7] This process facilitates the recrystallization of the CdTe grains, which in turn removes the high density of stacking faults.[1][8] The removal of stacking faults is a key indicator that the chlorine treatment has been successful.[9][10]

Q4: Is the removal of stacking faults the direct cause of improved device efficiency?

A4: While the removal of stacking faults is strongly correlated with improved efficiency, recent studies suggest it is a byproduct of a more critical process: the passivation of grain boundaries by chlorine.[6][7][10] Chlorine deactivates electron traps at the grain boundaries, making them less active recombination centers.[9][10] The disappearance of stacking faults serves as a clear signal that sufficient chlorine is present to achieve this vital passivation.[6][7][10]

Q5: What is the impact of substrate temperature during deposition on stacking faults?

A5: The substrate temperature during the deposition of the CdTe film influences the initial crystal quality, grain size, and defect density.[11][12][13] As the substrate temperature increases, the crystallization quality of the film generally improves, and the grain size tends to increase.[11][12][13] However, high deposition temperatures can also promote the formation and expansion of stacking faults due to thermal activation energy and stress from differing thermal expansion coefficients between the substrate and the film.[11][12]

Q6: Can the effects of the CdCl<sub>2</sub> treatment be reversed?

A6: Yes. Post-activation annealing at high temperatures (e.g., 400°C to 480°C) after the CdCl<sub>2</sub> treatment can drive chlorine out of the device.[5] This removal of chlorine from the grain boundaries leads to the reappearance of a high density of stacking faults and a corresponding sharp decrease in solar cell efficiency.[5]

# **Troubleshooting Guide**

# Troubleshooting & Optimization

Check Availability & Pricing

| Issue                                                                | Potential Causes                                                                                                                                                                                                                                                                                                                                                      | Recommended Actions                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High density of stacking faults remains after CdCl2 treatment.       | 1. Insufficient Annealing Temperature: The temperature may not have been high enough for effective chlorine diffusion and recrystallization. 2. Inadequate Annealing Time: The duration of the anneal may have been too short. 3. Uneven CdCl <sub>2</sub> Coating: A non- uniform layer of CdCl <sub>2</sub> can lead to incomplete treatment in some areas.         | 1. Optimize the annealing temperature. A common range is 400°C to 420°C.[9] 2. Increase the annealing time. Durations of 8 to 20 minutes are often cited.[1][9] 3. Ensure a uniform deposition of the CdCl <sub>2</sub> layer prior to annealing.                                     |

| Solar cell efficiency is low despite the removal of stacking faults. | 1. Suboptimal Chlorine Concentration: While stacking faults are removed, the grain boundaries may not be optimally passivated. 2. Inter- diffusion at the CdTe/CdS junction: The treatment can cause sulfur to migrate into the CdTe, which can affect the junction properties.[1] 3. Back Contact Issues: The back contact may not be optimal for charge extraction. | 1. Fine-tune the amount of CdCl <sub>2</sub> and the annealing parameters to achieve optimal grain boundary passivation. 2. Characterize the CdTe/CdS junction to assess interdiffusion and its impact. 3. Investigate and optimize the back contact material and deposition process. |

| Stacking faults have reappeared in a previously treated film.        | 1. Excessive Post-Activation Annealing: The device may have been subjected to high temperatures after the initial CdCl <sub>2</sub> treatment.[5]                                                                                                                                                                                                                     | 1. Avoid exposing the device to high temperatures after the activation step. If a post-activation anneal is necessary, carefully control the temperature and duration. A second CdCl2 treatment can restore efficiency by again removing the stacking faults.[5]                      |

# **Quantitative Data Summary**

Table 1: Impact of CdCl2 Treatment on CdTe Solar Cell Performance

| Parameter              | Untreated Cell | CdCl <sub>2</sub> Treated Cell | Reference        |

|------------------------|----------------|--------------------------------|------------------|

| Conversion Efficiency  | ~0.1% - <5%    | 11.77% - >12%                  | [1][2][4][9][10] |

| Stacking Fault Density | High           | Completely Removed             | [1][2]           |

Table 2: Effect of Post-Activation Annealing on CdCl2 Treated CdTe Solar Cells

| Annealing<br>Temperature    | Resulting Efficiency | Key Microstructural<br>Change                        | Reference |

|-----------------------------|----------------------|------------------------------------------------------|-----------|

| No Post-Anneal<br>(Initial) | ~12%                 | Stacking faults<br>absent, CI at grain<br>boundaries | [5]       |

| 400°C for 35s               | Reduced              | -                                                    | [5]       |

| 480°C for 35s               | ~3%                  | Re-appearance of stacking faults, CI removed         | [5]       |

Table 3: Influence of Substrate Temperature on CdTe Thin Film Properties (General Trends)

| Substrate<br>Temperature  | Grain Size | Crystallization<br>Quality | Reference            |

|---------------------------|------------|----------------------------|----------------------|

| Increasing<br>Temperature | Increases  | Improves                   | [11][12][13][14][15] |

# **Experimental Protocols**

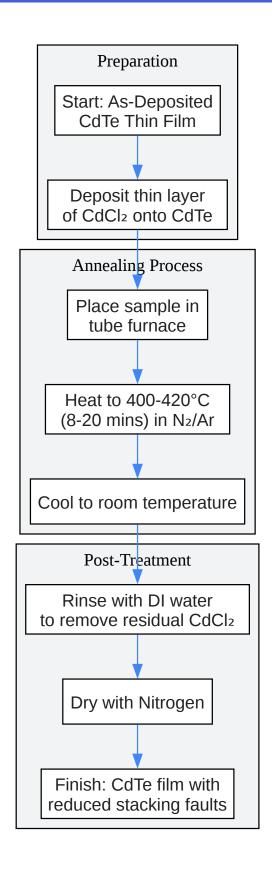

Protocol 1: Cadmium Chloride (CdCl2) Activation Treatment

Objective: To remove stacking faults and passivate grain boundaries in as-deposited CdTe thin films.

#### Materials:

- As-deposited CdTe thin film on a suitable substrate (e.g., FTO/glass with a CdS layer).

- Cadmium Chloride (CdCl<sub>2</sub>), high purity.

- Deionized water or a suitable solvent for creating a saturated solution, or a thermal evaporator.

- Tube furnace with temperature control and inert gas (e.g., Nitrogen or Argon) supply.

## Methodology:

- CdCl<sub>2</sub> Deposition:

- Vapor Treatment (Common Method): Place the CdTe sample and a source of CdCl<sub>2</sub> in a closed environment, such as a tube furnace. Heat the source to sublimate the CdCl<sub>2</sub> which will then deposit on the CdTe surface.

- Solution Coating: Prepare a saturated solution of CdCl<sub>2</sub>. Deposit a thin layer of the solution onto the CdTe surface using a method like dip-coating or spin-coating. Allow the solvent to fully evaporate, leaving a thin film of CdCl<sub>2</sub>.

- Annealing:

- Place the CdCl<sub>2</sub>-coated CdTe sample into a tube furnace.

- Purge the furnace with an inert gas to create an oxygen-poor atmosphere.

- Ramp the temperature to the target annealing temperature (e.g., 400°C) at a controlled rate.

- Hold the temperature for the desired duration (e.g., 8 minutes).[1]

- After the annealing time has elapsed, turn off the furnace and allow the sample to cool down to room temperature naturally under the inert gas flow.

- Post-Anneal Cleaning:

- Once cooled, remove the sample from the furnace.

- Rinse the surface with deionized water to remove any residual CdCl<sub>2</sub>.

- Dry the sample thoroughly using a stream of dry nitrogen.

Protocol 2: Investigating the Effect of Substrate Temperature

Objective: To determine the influence of substrate temperature during deposition on the microstructure of CdTe thin films.

#### Materials:

- CdTe deposition system (e.g., Close-Spaced Sublimation (CSS), Vapor Transport Deposition (VTD)).

- High-purity CdTe source material.

- Substrates compatible with high temperatures.

- Substrate heater with accurate temperature control.

## Methodology:

• Substrate Preparation:

- Thoroughly clean the substrates.

- Mount the substrates onto the substrate holder in the deposition chamber.

- Deposition at Various Temperatures:

- Set the substrate heater to the first desired temperature (e.g., 490°C).[11]

- Allow the substrate to reach thermal equilibrium.

- Initiate the CdTe deposition process according to the specific parameters of your system (e.g., source temperature, pressure).

- Deposit a film of the desired thickness.

- After deposition, cool the substrate down in a controlled manner.

- Repeat the deposition process for a range of substrate temperatures (e.g., 520°C, 550°C, 580°C), keeping all other deposition parameters constant.[11]

- Characterization:

- Analyze the microstructure of the films deposited at different temperatures using techniques such as:

- Scanning Electron Microscopy (SEM): To observe grain size and surface morphology.

[11]

- X-Ray Diffraction (XRD): To determine crystal structure and preferred orientation.

- Transmission Electron Microscopy (TEM): To directly observe stacking faults and other defects within the crystal grains.[11]

## **Visualizations**

Click to download full resolution via product page

Caption: Workflow for CdCl2 Activation Treatment of CdTe Thin Films.

Click to download full resolution via product page

Caption: Relationship between CdCl2 treatment and device performance.

### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. pstorage-loughborough-53465.s3.amazonaws.com [pstorage-loughborough-53465.s3.amazonaws.com]

- 2. pubs.aip.org [pubs.aip.org]

- 3. researchgate.net [researchgate.net]

- 4. pubs.aip.org [pubs.aip.org]

- 5. scispace.com [scispace.com]

- 6. Chlorine activated stacking fault removal mechanism in thin film CdTe solar cells: the missing piece PubMed [pubmed.ncbi.nlm.nih.gov]

- 7. Chlorine activated stacking fault removal mechanism in thin film CdTe solar cells: the missing piece [ouci.dntb.gov.ua]

- 8. researchgate.net [researchgate.net]

- 9. taiyangnews.info [taiyangnews.info]

- 10. pv-magazine.com [pv-magazine.com]

- 11. arxiv.org [arxiv.org]

- 12. [2308.03318] The effect of substrate temperature on cadmium telluride films in high temperature vapor deposition process [arxiv.org]

- 13. researchgate.net [researchgate.net]

- 14. researchgate.net [researchgate.net]

- 15. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: Reducing Stacking Faults in Cadmium Telluride (CdTe) Thin Films]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b081085#reducing-stacking-faults-in-cadmium-telluride-thin-films]

## **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com