Check Availability & Pricing

# Technical Support Center: Reducing Defects and Variations in Silicon Wafers

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |          |           |

|----------------------|----------|-----------|

| Compound Name:       | Silicon  |           |

| Cat. No.:            | B1239273 | Get Quote |

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to help researchers, scientists, and drug development professionals identify and mitigate common defects and variations during **silicon** wafer fabrication.

# **Frequently Asked Questions (FAQs)**

Q1: What are the most common types of defects found on silicon wafers?

A1: Common **silicon** wafer defects can be broadly categorized into surface defects and crystal defects.[1]

- Surface Defects: These include scratches, pits (tiny missing spaces), and particles from contaminants like equipment, human contact, or chemical residues.[1] These imperfections can disrupt lithography patterns and obstruct layer deposition.[1]

- Crystal Defects: These are disruptions to the perfect crystalline structure of the silicon, which can reduce carrier mobility.[1]

- Patterned Wafer Defects: Specific to patterned wafers, these can include bridges/opens in the circuitry, overlay errors, and variations in line-edge roughness.

Q2: Why is it critical to reduce defects and variations in **silicon** wafer fabrication?

A2: Even minuscule defects can disrupt the performance of an entire electronic device, leading to device failures or degraded performance.[1][3] In semiconductor manufacturing, early defect

detection is crucial because the smallest imperfection can lead to significant recalls and financial losses.[3] Process variation, the naturally occurring variation in transistor attributes, can cause the performance of a circuit to fall outside of its required specification, reducing the overall yield.[4]

Q3: What are the primary causes of process variation?

A3: Process variation arises from the many steps in semiconductor manufacturing where imperfections, variability, and alignment issues can occur.[5] Key sources include variations in gate oxide thickness, random dopant fluctuations, and issues with device geometry and lithography, especially at smaller process nodes.[4]

Q4: What is the impact of wafer size on defect susceptibility?

A4: As wafers become smaller and thinner, they are more susceptible to defects.[6] On an ultra-thin wafer, even the smallest chip, which might not have been considered serious on a larger surface, can cause significant issues.[6] Manufacturing ultra-thin wafers presents challenges in handling, maintaining thickness uniformity, and controlling warpage and bowing. [7]

Q5: How has defect detection evolved with shrinking semiconductor sizes?

A5: As semiconductors have shrunk, the technology within traditional optical inspection systems has struggled to keep up.[6] This has led to an increasing need for inspection systems with better resolution and accuracy.[6] Modern approaches include e-beam inspection for higher resolution, Scanning Probe Microscopy (SPM) for atomic-level detection, and the integration of machine learning and Artificial Intelligence (AI) for automated defect classification.[3][8]

## **Troubleshooting Guides**

This section provides detailed troubleshooting for specific defects encountered during **silicon** wafer fabrication.

### Issue 1: Scratches on the Wafer Surface

## Troubleshooting & Optimization

Q: My wafers are exhibiting linear or curvy scratch marks. What is the root cause and how can I fix it?

A: Scratch defects are typically elongated linear patterns caused by contact between a foreign contaminant and the wafer surface.[9]

#### Potential Causes:

- Faulty Wafer Handling: The most common cause is the presence of foreign contaminants on wafer handling robots, buffer cassette components, or Front Opening Unified Pods (FOUPs).[9] Faulty robot handoffs can lead to physical impacts that scrape the delicate wafer surface.[6]

- Abrasive Particles: Scratches can be caused by large particles during brushing, scrubbing, and polishing processes.

- Contaminated Equipment: Debris or sharp edges within processing equipment can come into contact with the wafer.

#### Troubleshooting Steps:

- Inspect Wafer Handling Systems: Thoroughly examine all components that come into contact with the wafers, including robot end-effectors, cassettes, and FOUPs, for any foreign particles, fibers, or residues.[9]

- Use Investigation Wafers: It is recommended to use film-coated investigation wafers to help identify the repeatedly impacted region of the wafer, which can help pinpoint the source of the scratch.[9]

- Analyze Wafer Movement: Understanding the wafer's path through the manufacturing equipment is key to troubleshooting.[9] Correlate the location of the scratch with specific wafer touchpoints.[9]

- Clean Process Chambers: Ensure that all process chambers and associated components are free from particulate contamination.

Review Polishing/Cleaning Processes: Check the slurries, pads, and brushes used in chemical-mechanical planarization (CMP) and cleaning steps for abrasive contaminants.

# Issue 2: Circular or Ring-Like Defects in the Wafer Center

Q: I am observing defects concentrated in a circular or "bulls-eye" pattern near the center of my wafer. What could be causing this?

A: These are known as center-type defects and are commonly caused by abnormalities in various pieces of equipment during the fabrication process.[6]

#### Potential Causes:

- Equipment Abnormalities: An increase in radio frequency (RF) power, or an irregularity in liquid flow or pressure can cause these defects.

- Non-uniform Thin Film Deposition: Equipment-related issues leading to non-uniformities during thin film deposition can result in center-type defects.[6]

- pH Variation: Some studies suggest that a variation in pH that alters the surface charge can trigger particle agglomeration at the center of the wafer.

- Plasma Non-Uniformity: In plasma-based processes like etching or deposition, non-uniformity in the plasma can lead to defects concentrated at the center.

#### Troubleshooting Steps:

- Calibrate Equipment: Verify and calibrate equipment settings, including RF power, gas flow rates, and liquid pressure, to ensure they are within specified parameters.

- Inspect Showerheads: Check showerheads in deposition and etching tools for contamination or blockages that could cause non-uniform process gas distribution.

- Monitor Process Parameters: Implement statistical process control (SPC) to monitor

critical parameters in real-time and detect drifts that could lead to center defects.[10][11]

Analyze Deposition Uniformity: Use metrology tools to measure the uniformity of deposited thin films across the wafer. Address any center-high or center-low non-uniformities by adjusting the deposition recipe or performing equipment maintenance.

# **Issue 3: Randomly Distributed Particle Defects**

Q: My wafers show small particles scattered randomly across the entire surface. How can I identify the source and prevent this?

A: Random-type defects are distributed across the wafer surface and can be caused by contaminated pipes and abnormalities in equipment like showerheads.[6]

#### Potential Causes:

- Contaminated Process Tools: Particles can originate from the internal components of process equipment.

- Flaking from Chamber Walls: Films deposited on the walls of process chambers can flake

off and land on the wafer surface.

- Contaminated Chemicals or Gases: The gases and chemicals used in fabrication can contain particles.

- Environmental Contamination: Although modern fabs are extremely clean, particles can still be introduced from the environment or personnel if protocols are not strictly followed.

[12]

#### Troubleshooting Steps:

- Perform Tool Cleaning Cycles: Run regular cleaning cycles for process chambers to remove accumulated deposits.

- Check Gas and Chemical Purity: Verify the purity of all process gases and chemicals.

Ensure that all filters in the supply lines are functioning correctly.

- Monitor Cleanroom Environment: Ensure the cleanroom environment meets the required standards for particle counts.

Implement Particle Monitoring: Use in-situ particle monitors on equipment to detect particle events in real-time. This can help correlate particle additions to specific process steps.

# Data Presentation Table 1: Comparison of Common Wafer Inspection Techniques

| Inspection<br>Technique             | Principle                                                                                                         | Detectable<br>Defect Size                        | Throughput | Primary Use<br>Cases                                                                                 |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------|------------------------------------------------------------------------------------------------------|

| Brightfield<br>Inspection           | Uses a 193 nm<br>light source;<br>defects appear<br>as dark spots<br>against a bright<br>background.[13]          | Down to 30 nm. [13]                              | High       | Detecting various defects on patterned wafers.                                                       |

| Darkfield<br>Inspection             | Collects scattered light from defects; excels at identifying deviations in lithography, etch, and deposition. [8] | High sensitivity<br>for certain defect<br>types. | High       | Detecting defects<br>on both<br>patterned and<br>unpatterned<br>wafers with high<br>contrast.[8]     |

| E-Beam<br>Inspection                | A highly focused electron beam scans the wafer to find defects.                                                   | Down to 3 nm. [13]                               | Slow       | High-resolution detection of nanoscale defects, often used for engineering analysis.[3][13]          |

| Atomic Force<br>Microscopy<br>(AFM) | A physical probe scans the wafer surface to provide atomic-level resolution.                                      | Nanometer-<br>scale.[8]                          | Very Slow  | Detecting topographical variations and nanometer-scale defects; surface roughness quantification.[8] |

| Scanning<br>Electron                | A focused<br>electron beam<br>scans the                                                                           | High spatial resolution                          | Slow       | Detailed analysis<br>and<br>characterization                                                         |

of identified

defects.[14][15]

Microscopy surface, (nanometers).

(SEM) producing [15]

signals that reveal the

characteristics of surface defects.

[15]

# **Experimental Protocols**

# Protocol 1: Defect Inspection using Scanning Electron Microscopy (SEM)

This protocol outlines the general steps for characterizing surface defects on a **silicon** wafer using an SEM.

- Objective: To obtain high-resolution images of surface defects for morphological analysis.

- Materials:

- Silicon wafer with suspected defects.

- Wafer holder compatible with the SEM.

- Conductive tape or paint (if needed for non-conductive samples).

- Methodology:

- Sample Preparation: Carefully cleave a small piece of the wafer containing the defect of interest. Mount the sample securely on the SEM holder. For insulating layers, a thin conductive coating may be required to prevent charging.

- 2. System Preparation: Vent the SEM chamber and load the sample. Pump the chamber down to the required vacuum level.

- 3. Imaging:

- Turn on the electron beam and set an appropriate accelerating voltage (e.g., 5-15 kV).

- Navigate to the area of interest using low magnification.

- Increase magnification to focus on the specific defect.

- Adjust focus, astigmatism, and brightness/contrast to obtain a sharp image.

- Capture images of the defect using both secondary electron (SE) detectors for topography and back-scattered electron (BSE) detectors for compositional contrast if applicable.[15]

- 4. Data Analysis: Analyze the captured images to determine the size, shape, and characteristics of the defect. This information can help identify the root cause.[15]

# Protocol 2: Surface Roughness and Topography Analysis using Atomic Force Microscopy (AFM)

This protocol describes the use of AFM to quantify surface roughness at the nanoscale.

- Objective: To measure the surface topography and quantify roughness parameters like Ra (average roughness).

- Materials:

- Silicon wafer sample.

- AFM with appropriate cantilever/tip.

- Methodology:

- 1. Sample Preparation: Mount a small piece of the wafer onto the AFM sample stage.

- 2. System Setup:

- Load the sample into the AFM.

- Install a suitable AFM probe (cantilever with a sharp tip).

- Align the laser onto the cantilever and adjust the photodetector to zero the signal.

#### 3. Imaging:

- Engage the tip with the sample surface in tapping mode to minimize surface damage.

- Define the scan area (e.g., 1x1 μm, 5x5 μm) and scan rate.

- Initiate the scan. The AFM will raster the probe over the surface, recording height variations.[8]

#### 4. Data Analysis:

- The AFM software will generate a 3D topographical map of the surface.

- Use the software's analysis tools to level the image and calculate roughness parameters (e.g., Ra, Rq).

- Analyze the image for any specific topographical defects like pits or mounds.

### **Visualizations**

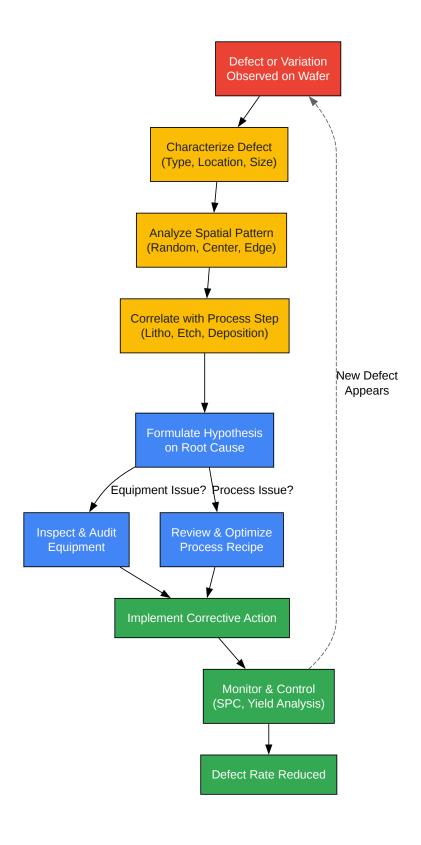

# **Logical Workflow for Troubleshooting Wafer Defects**

Click to download full resolution via product page

Caption: A flowchart for systematic defect troubleshooting.

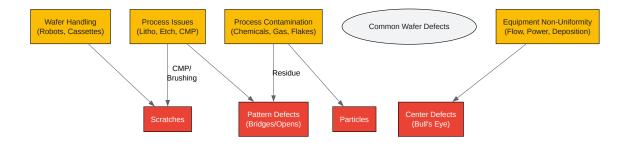

## **Common Wafer Defect Causation Pathways**

Click to download full resolution via product page

Caption: Mapping common defects to their primary sources.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. waferpro.com [waferpro.com]

- 2. Wafer Inspection Guide: Methods, Use Cases & Al Insights [averroes.ai]

- 3. Understanding Defect Detection in Patterned Wafers [silybwafers.com]

- 4. Process variation (semiconductor) Wikipedia [en.wikipedia.org]

- 5. semiengineering.com [semiengineering.com]

- 6. Common Mistakes During Silicon Wafer Processing [waferworld.com]

- 7. Challenges and Innovations in Manufacturing Thin Silicon Wafers [waferworld.com]

- 8. Top 5 Wafer Inspection Tools for Semiconductor... | Robovision [robovision.ai]

- 9. foamtecintlwcc.com [foamtecintlwcc.com]

- 10. thegrenze.com [thegrenze.com]

- 11. praxie.com [praxie.com]

- 12. quora.com [quora.com]

- 13. labproinc.com [labproinc.com]

- 14. universitywafer.com [universitywafer.com]

- 15. Defect Inspection Techniques in SiC PMC [pmc.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [Technical Support Center: Reducing Defects and Variations in Silicon Wafers]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1239273#reducing-defects-and-variations-in-silicon-wafers-during-fabrication]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com