# Technical Support Center: Reducing Crystalline Defects in Silicon-28 Ingots

Author: BenchChem Technical Support Team. Date: December 2025

Aimed at researchers, scientists, and drug development professionals, this technical support center provides detailed troubleshooting guides and frequently asked questions (FAQs) to address common challenges encountered during the growth of high-purity **Silicon-28** (Si-28) ingots. While Si-28 is specifically targeted, the principles and protocols outlined are largely applicable to the production of any electronic-grade high-purity silicon.

This resource offers structured data tables for easy comparison of key parameters, detailed experimental protocols for crucial defect reduction techniques, and visual workflows to clarify complex processes.

## **Troubleshooting Guides**

This section addresses specific issues that may arise during Si-28 ingot growth, providing potential causes and recommended solutions in a straightforward question-and-answer format.

# Troubleshooting & Optimization

Check Availability & Pricing

| Issue / Observation                                          | Potential Causes                                                                                                                                                                                                                            | Recommended Actions & Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Dislocation Density in Ingot                            | - Excessive thermal stress due to high temperature gradients.  [1][2] - Seed crystal quality is poor or improperly handled Particulate contamination at the solid-liquid interface.                                                         | - Reduce Thermal Gradients: Optimize the furnace's hot zone design and insulation. Employ slower cooling rates after growth.[1] - Seed Crystal Preparation: Use a high- quality, dislocation-free seed crystal. Implement a "necking" process where the crystal diameter is reduced to a few millimeters to terminate dislocations from the seed.[3] - Maintain Cleanliness: Ensure the polysilicon charge and the furnace environment are of the highest purity to avoid particulate contamination. |

| Presence of Voids or Crystal-<br>Originated Particles (COPs) | - High vacancy concentration due to rapid pulling rates or high thermal gradients.[4] - Insufficient control of the V/G ratio (pulling rate divided by the axial thermal gradient).[1] - Thermal stress-induced vacancy supersaturation.[4] | - Control V/G Ratio: Precisely control the pulling rate and thermal gradient to maintain a slightly interstitial-rich or near-stoichiometric condition at the solidification front.[1] - Reduce Pulling Rate: A slower pulling rate allows more time for vacancy annihilation and reduces their incorporation into the crystal.[4] - Annealing: Post-growth annealing can help dissolve existing voids.                                                                                              |

| Elevated Metallic Impurity Concentrations                    | - Contamination from the quartz crucible (in the Czochralski method).[5] - Impurities present in the                                                                                                                                        | - Utilize Float-Zone (FZ)  Method: For the highest purity, the FZ method is preferred as it avoids contact with a                                                                                                                                                                                                                                                                                                                                                                                    |

# Troubleshooting & Optimization

Check Availability & Pricing

|                                      | starting polycrystalline silicon Contamination from the furnace components.                                                                                                      | crucible.[6][7] - Implement Gettering: Employ intrinsic or extrinsic gettering techniques to draw impurities away from the active device regions of the final wafers.[8] - High-Purity Materials: Start with the highest purity polycrystalline silicon available and ensure all furnace components are made from high-purity materials.[9]        |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Formation of Stacking Faults         | - Agglomeration of silicon self-<br>interstitials Metallic<br>contamination, particularly<br>from oxidation processes<br>Surface damage or<br>contamination on the<br>substrate. | - Control Interstitial Concentration: Optimize the V/G ratio to avoid a high supersaturation of self- interstitials Gettering: Implement gettering to remove metallic impurities that can nucleate stacking faults.[8] - Surface Preparation: Ensure the substrate surface is meticulously cleaned and free of any damage before epitaxial growth. |

| Inhomogeneous Dopant<br>Distribution | - Fluctuations in the melt<br>temperature and convection<br>Inconsistent pulling and<br>rotation rates Segregation of<br>dopants at the solid-liquid<br>interface.               | - Stabilize Melt Dynamics: Use magnetic fields to suppress turbulent convection in the melt (in the CZ method) Precise Control of Growth Parameters: Maintain stable and precise control over the pulling and rotation rates.[10] - Consider FZ Doping: The FZ method allows for more uniform doping through gasphase doping.[3]                   |

## Frequently Asked Questions (FAQs)

Q1: What are the primary types of crystalline defects in Silicon-28 ingots?

A1: Crystalline defects in silicon are broadly categorized as:

- Point Defects: These include vacancies (a missing silicon atom), self-interstitials (a silicon atom in a non-lattice position), and impurity atoms.[11]

- Line Defects (Dislocations): These are one-dimensional defects that disrupt the crystal lattice, impacting its mechanical and electrical properties.[11]

- Area Defects: These include stacking faults (a disruption in the stacking sequence of crystallographic planes) and grain boundaries.[11]

- Volume Defects: These are three-dimensional defects such as voids (agglomerations of vacancies) and precipitates of impurities like oxygen or metals.[11]

Q2: What is the difference between the Czochralski (CZ) and Float-Zone (FZ) methods for Si-28 growth, and which is better for minimizing defects?

A2: The Czochralski (CZ) method involves pulling a single crystal from a molten silicon bath contained in a quartz crucible.[10] The Float-Zone (FZ) method involves passing a molten zone along a polycrystalline rod, which recrystallizes as a single crystal without the need for a crucible.[6][7] For achieving the highest purity and lowest defect density, the FZ method is generally superior as it avoids contamination from the crucible, particularly oxygen.[3] However, the CZ method is more cost-effective for producing large-diameter ingots.[12]

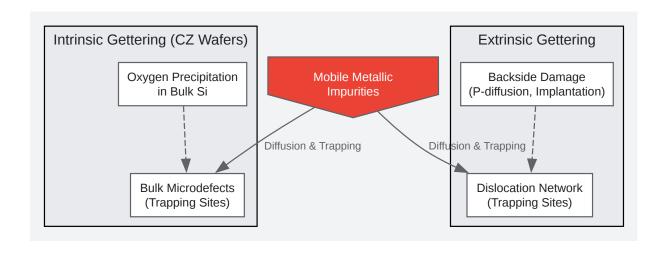

Q3: What is "gettering" and how does it help reduce defects?

A3: Gettering is a process that removes metallic impurities from the active regions of a silicon wafer by creating trapping sites in other, less critical areas.[8] There are two main types:

- Intrinsic Gettering: This method uses oxygen precipitates within the bulk of Czochralskigrown silicon wafers as trapping sites for impurities.[13]

- Extrinsic Gettering: This involves creating a damaged layer on the backside of the wafer (e.g., through sandblasting, ion implantation, or phosphorus diffusion) to act as a sink for

impurities.[8]

Q4: How do thermal stress and temperature gradients contribute to defect formation?

A4: High thermal gradients during crystal growth and cooling induce stress in the ingot.[1] If this stress exceeds the elastic limit of silicon at high temperatures, it is relieved by the formation of dislocations.[2] Thermal stress can also influence the concentration of point defects, with compressive stress favoring the formation of vacancies, which can then agglomerate into voids. [4]

Q5: What are the acceptable impurity levels for high-purity Silicon-28?

A5: For electronic-grade silicon (EGS), which serves as a proxy for the requirements of Si-28, extremely high purity is necessary. Metallic impurities should be in the parts per billion (ppb) range or lower, while non-metallic impurities like carbon and oxygen should be less than a few parts per million (ppm).[9]

### **Data Presentation**

The following tables summarize key quantitative data related to defect control in high-purity silicon growth.

Table 1: Typical Impurity Concentration Limits in Electronic-Grade Silicon (EGS)

| Impurity Type                       | Typical Concentration in EGS |  |

|-------------------------------------|------------------------------|--|

| Metals (e.g., Iron, Copper, Nickel) | < 1 ppb[14]                  |  |

| Boron                               | < 0.05 ppb[14]               |  |

| Phosphorus                          | < 0.05 ppb[14]               |  |

| Carbon                              | < 1000 ppb (1 ppm)[14]       |  |

| Oxygen (FZ Method)                  | < 5 x 1015 atoms/cm3[3]      |  |

| Oxygen (CZ Method)                  | ~1018 atoms/cm3[13]          |  |

Table 2: Influence of Czochralski Growth Parameters on Dislocation Density

| Pull Rate (cm/h)     | Rotation Rate (rpm) | Resulting<br>Dislocation Density | Observations                                                     |

|----------------------|---------------------|----------------------------------|------------------------------------------------------------------|

| 7.62                 | 12                  | Relatively low and constant      | Nearly ideal radial stress pattern.                              |

| Higher Pull Rates    | Variable            | Tends to increase                | Can lead to non-ideal stress patterns and plastic flow.          |

| Lower Pull Rates     | Variable            | Can be higher than optimal       | May result in a convex solid-liquid interface, affecting stress. |

| Lower Rotation Rates | Variable            | Can increase thermal gradients   | Potentially leads to higher dislocation densities.               |

(Data derived from a study on the effects of growth parameters on dislocation density.)

## **Experimental Protocols**

Protocol 1: Czochralski (CZ) Crystal Growth for Low-Defect Silicon

- Crucible Charging: Load a high-purity quartz crucible with electronic-grade polycrystalline silicon. Dopant elements can be added at this stage for desired resistivity.[10]

- Melting: Heat the polysilicon in an inert argon atmosphere to above its melting point (approximately 1425°C).[10]

- Seed Dipping: Lower a precisely oriented, dislocation-free single-crystal silicon seed into the molten silicon.[15]

- Necking: Initially, pull the seed at a high rate to create a thin "neck" of 3-5 mm in diameter.

This process helps to eliminate any dislocations propagating from the seed.

- Shoulder Growth: Gradually decrease the pull rate and adjust the temperature to widen the crystal to the desired diameter.

#### Troubleshooting & Optimization

- Body Growth: Maintain a constant pull rate and rotation speed to grow the main body of the ingot with a uniform diameter. Precise control of the temperature gradients, pull rate, and rotation speed is crucial to minimize defects.[10]

- Tail Growth: Increase the pull rate to gradually reduce the diameter at the end of the ingot.

- Cooling: After extraction from the melt, cool the ingot slowly and under controlled conditions to minimize thermal stress and the formation of new defects.

Protocol 2: Float-Zone (FZ) Crystal Growth for High-Purity Silicon

- Setup: Mount a high-purity polycrystalline silicon rod vertically in a vacuum or inert gas chamber. A seed crystal is placed at the bottom.[6][7]

- Zone Melting: Use a radio-frequency (RF) heating coil to create a narrow molten zone at the bottom of the polysilicon rod, in contact with the seed crystal.[3]

- Crystal Growth: Slowly move the RF coil upwards. The molten zone moves with the coil, and as it moves, the silicon behind it solidifies, growing as a single crystal with the orientation of the seed.[3]

- Purification: Most impurities are more soluble in the molten silicon than in the solid. As the molten zone moves up the rod, it carries the impurities with it, concentrating them at the top end of the ingot, which can be cut off later.[6]

- Doping (Optional): Dopant gases can be introduced into the inert atmosphere to achieve uniform doping of the growing crystal.[3]

Protocol 3: Intrinsic Gettering via Double Pre-annealing

- High-Temperature Annealing: Anneal the Czochralski-grown silicon wafer at a high temperature (e.g., ~1000-1100°C) in a non-oxygen ambient (e.g., nitrogen). This step out-diffuses oxygen from the near-surface region, creating a "denuded zone."[16][17]

- Low-Temperature Annealing: Follow with a low-temperature anneal (e.g., ~650°C). This step promotes the nucleation of oxygen precipitates in the bulk of the wafer, where the oxygen concentration remains high.[16][17]

High-Temperature Growth: A final high-temperature step (e.g., ~1000°C) causes these nuclei

to grow into stable precipitates, which act as gettering sites for metallic impurities during

subsequent device processing.

#### Protocol 4: Extrinsic Gettering via Phosphorus Diffusion

- Phosphorus Source Deposition: Apply a phosphorus source, such as phosphorus oxychloride (POCl3), to the backside of the silicon wafer.[8]

- Diffusion Anneal: Heat the wafer to a high temperature (e.g., 800-950°C) in a controlled atmosphere.[18] This causes phosphorus to diffuse into the silicon lattice on the backside.

- Defect Formation: The high concentration of phosphorus atoms creates a layer with a high density of dislocations and other lattice defects.

- Impurity Trapping: During this and subsequent high-temperature processing steps, mobile metallic impurities in the wafer will diffuse to and become trapped in this highly defected backside layer.[8]

### **Mandatory Visualization**

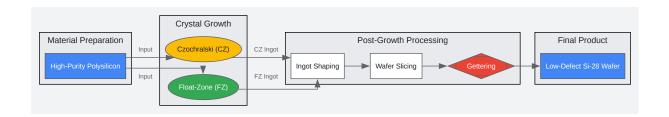

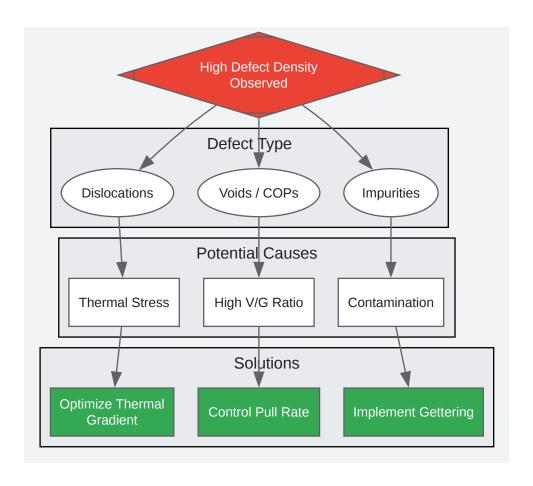

Below are diagrams created using the Graphviz (DOT language) to illustrate key workflows and relationships in reducing crystalline defects in **Silicon-28** ingots.

Click to download full resolution via product page

Caption: High-level workflow for producing low-defect Si-28 wafers.

Click to download full resolution via product page

Caption: Troubleshooting logic for common crystalline defects.

Click to download full resolution via product page

Caption: Pathways for intrinsic and extrinsic gettering of impurities.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. mdpi.com [mdpi.com]

- 2. arxiv.org [arxiv.org]

- 3. medium.com [medium.com]

- 4. researchgate.net [researchgate.net]

- 5. www2.irb.hr [www2.irb.hr]

- 6. Float-zone silicon Wikipedia [en.wikipedia.org]

- 7. Understanding the Float Zone Method [waferworld.com]

- 8. Phosphorus diffusion gettering process of multicrystalline silicon using a sacrificial porous silicon layer PubMed [pubmed.ncbi.nlm.nih.gov]

- 9. chem.libretexts.org [chem.libretexts.org]

- 10. Czochralski method Wikipedia [en.wikipedia.org]

- 11. Crystalline Defects in Silicon: A Guide to Buying Silicon Wafers [waferworld.com]

- 12. youtube.com [youtube.com]

- 13. cityu.edu.hk [cityu.edu.hk]

- 14. Electronic Grade Silicon → Term [pollution.sustainability-directory.com]

- 15. youtube.com [youtube.com]

- 16. pubs.aip.org [pubs.aip.org]

- 17. pubs.aip.org [pubs.aip.org]

- 18. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: Reducing Crystalline Defects in Silicon-28 Ingots]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1257143#reducing-crystalline-defects-in-silicon-28-ingots]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com