### Technical Support Center: Reducing Contact Resistance in MoS<sub>2</sub> Transistors

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                    |           |

|----------------------|--------------------|-----------|

| Compound Name:       | Molybdenum sulfide |           |

| Cat. No.:            | B1676702           | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and professionals working to minimize contact resistance in Molybdenum Disulfide (MoS<sub>2</sub>) field-effect transistors (FETs).

## Frequently Asked Questions (FAQs) & Troubleshooting

## Q1: My measured contact resistance is excessively high. What are the primary causes?

A1: High contact resistance (Rc) in MoS<sub>2</sub> transistors is a common issue that primarily stems from two phenomena: the Schottky barrier at the metal-MoS<sub>2</sub> interface and Fermi-level pinning.

- Schottky Barrier: A significant energy barrier, known as a Schottky barrier, often forms at the junction between the metal contact and the MoS<sub>2</sub> semiconductor. This barrier impedes the efficient injection of charge carriers (electrons) from the metal into the MoS<sub>2</sub> channel, leading to high resistance. The height of this barrier is a critical factor determining device performance.

- Fermi-Level Pinning: Ideally, the Schottky barrier height could be minimized by choosing a metal with a work function that perfectly matches the electron affinity of MoS<sub>2</sub>. However, in practice, the metal's Fermi level often gets "pinned" within the MoS<sub>2</sub> bandgap due to interface states, such as defects or vacancies in the MoS<sub>2</sub> crystal.[1] This pinning effect

makes the contact resistance less dependent on the choice of metal work function than theoretical models would suggest, often resulting in a stubbornly high Schottky barrier.[1]

Interface Contamination: Residues from fabrication processes (e.g., lithography), poor adhesion of the contact metal, or the formation of an oxide layer at the interface can introduce additional scattering and trapping sites, further increasing contact resistance.

### Q2: How do I select an appropriate contact metal to minimize resistance?

A2: While Fermi-level pinning can complicate metal selection, choosing the right metal is still a critical step. Low work function metals are generally preferred for n-type MoS<sub>2</sub> to reduce the Schottky barrier height.

However, the morphology and chemical interaction at the interface are equally important. For instance, studies have shown that silver (Ag) contacts can lead to significantly better electrical performance than titanium (Ti) contacts, which are also commonly used.[2][3] This difference is attributed to the smoother and denser film formed by Ag on MoS<sub>2</sub>, which results in higher carrier transport efficiency.[2][3][4] In contrast, Ti films can form pinholes and have a higher surface roughness, degrading contact quality.[2][5] Using an interlayer, such as graphene, can also decouple the MoS<sub>2</sub> from the metal, mitigating Fermi-level pinning and enabling a wider range of effective contact metals.[6][7]

### Q3: I'm observing non-linear I-V curves, particularly at low drain bias. How can I achieve more Ohmic contacts?

A3: Non-linear (non-Ohmic) current-voltage (I-V) characteristics are a classic sign of a significant Schottky barrier. Several strategies can be employed to promote more Ohmic behavior:

Annealing: Post-fabrication annealing is a critical step for improving contacts. Annealing can remove contaminants, improve metal adhesion, and promote diffusion of the metal into the MoS<sub>2</sub>, which dopes the contact region and reduces the barrier width for carrier tunneling.[8]

[9][10]

- Surface Treatments: Treating the MoS<sub>2</sub> surface before metal deposition can passivate defects like sulfur vacancies. A simple sulfur-based treatment has been shown to reduce the density of surface states, decrease the Schottky barrier height, and lead to a significant drop in contact resistance for high work function metals like Nickel (Ni) and Palladium (Pd).[11] [12][13]

- Phase Engineering: Inducing a phase transition in the MoS<sub>2</sub> under the contact regions from

the semiconducting 2H phase to the metallic 1T phase can dramatically lower contact

resistance.[14] This can be achieved through methods like chemical treatment (e.g., using

organolithium compounds) or plasma exposure.[14]

# Q4: My device performance is inconsistent across different fabrication batches. What contributes to this variability and how can I improve it?

A4: Variability often arises from inconsistent interface quality. Intrinsic defects in the MoS<sub>2</sub> material itself can dominate contact resistance and introduce unpredictability.[11] To improve consistency:

- Standardize Surface Preparation: Implement a rigorous and repeatable cleaning and surface treatment protocol before every metal deposition. Sulfur-based treatments have been noted to not only reduce resistance but also nearly eliminate contact variability.[11][12]

- Control Deposition Conditions: The conditions during metal deposition, such as vacuum pressure, are crucial. Lowering the deposition pressure can improve the quality of the metal-MoS<sub>2</sub> interface and lead to lower contact resistance.[15]

- Insert a Buffer Layer: Using a uniform interlayer, such as Al<sub>2</sub>O<sub>3</sub> deposited via atomic layer deposition (ALD), can passivate the MoS<sub>2</sub> surface and prevent direct interaction between the metal and semiconductor, reducing variability.[16] Graphene is another excellent buffer layer that provides a clean, van der Waals interface.[6][17]

### **Data Summary: Contact Resistance Comparison**

The following tables summarize quantitative data from various experimental approaches to reducing contact resistance in MoS<sub>2</sub> transistors.

**Table 1: Effect of Annealing on Contact Resistance**

| Contact Metal   | MoS <sub>2</sub><br>Thickness | As-Deposited<br>Rc (kΩ·μm) | Annealing<br>Temp. (°C) | Post-<br>Annealing Rc<br>(kΩ·μm) |

|-----------------|-------------------------------|----------------------------|-------------------------|----------------------------------|

| Ag              | Few-layer (5-14)              | 0.8 - 3.5[10][18]          | 250 - 300[10][18]       | 0.2 - 0.7[10][18]                |

| (Not specified) | Single-crystal                | 209.3[8]                   | 300 (Stepped)[8]        | 4.7[8]                           |

**Table 2: Comparison of Different Contact Strategies**

| Contact Strategy              | MoS₂ Type                 | Key Result                                                    | Contact Resistance<br>(Rc)               |

|-------------------------------|---------------------------|---------------------------------------------------------------|------------------------------------------|

| Metal Selection               |                           |                                                               |                                          |

| Ag vs. Ti Contacts            | Monolayer & Few-<br>layer | Ag contacts yield >60x higher ON-state current than Ti.[2][5] | Not explicitly stated, but lower for Ag. |

| Interlayer Insertion          | _                         |                                                               |                                          |

| Graphene/Ti<br>Heterocontact  | Few-layer                 | 3.3x improvement in<br>Rc compared to Ti<br>alone.[20]        | 3.7 ± 0.3 kΩ·μm[20]                      |

| Nickel-Etched<br>Graphene     | (Not specified)           | ~2 orders of magnitude enhancement over pure Ni.[17]          | As low as 200<br>Ω·μm[17]                |

| ALD Al₂O₃ Interlayer          | Single-layer CVD          | Rc reduced by over two orders of magnitude.[16]               | 250 kΩ·μm[16]                            |

| Surface/Interface Doping      |                           |                                                               |                                          |

| Sulfur Treatment (Ni contact) | Multilayer                | >6x drop in contact resistance.[12]                           | (Not specified)                          |

| Sulfur Treatment (Pd contact) | Multilayer                | >10x drop in contact resistance.[12]                          | (Not specified)                          |

| LiPON Buffer Layer            | Few-layer                 | Rc reduced to 20% of its pre-doping value.                    | (Not specified)                          |

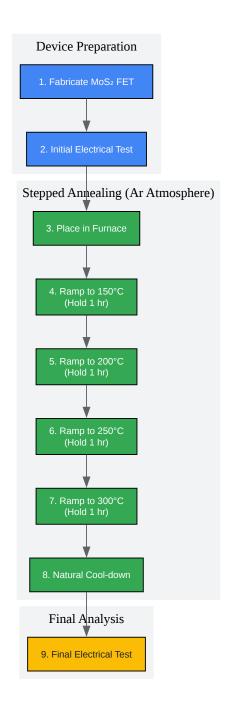

# Experimental Protocols & Visualizations Protocol 1: Stepped Annealing for Contact Improvement

### Troubleshooting & Optimization

This protocol describes an innovative stepped annealing process shown to dramatically reduce contact resistance.[8]

- Device Fabrication: Fabricate MoS<sub>2</sub> back-gated FETs on a Si/SiO<sub>2</sub> substrate using standard lithography and metal deposition techniques.

- Initial Characterization: Perform initial electrical measurements to determine the baseline device performance and contact resistance.

- Stepped Annealing Procedure:

- Place the fabricated devices in a tube furnace with a controlled Argon (Ar) atmosphere.

- Step 1: Ramp the temperature to 150°C and hold for 1 hour.

- Step 2: Increase the temperature to 200°C and hold for 1 hour.

- Step 3: Increase the temperature to 250°C and hold for 1 hour.

- Step 4: Increase the temperature to the optimal 300°C and hold for 1 hour.

- Allow the furnace to cool down naturally to room temperature under the Ar atmosphere.

- Final Characterization: Re-measure the electrical properties of the devices to quantify the improvement in contact resistance, mobility, and on/off ratio.

Click to download full resolution via product page

Workflow for stepped annealing of MoS<sub>2</sub> transistors.

### Protocol 2: Graphene Interlayer for Low-Resistance Contacts

This protocol outlines the fabrication of MoS<sub>2</sub> FETs using a graphene interlayer to achieve clean, low-resistance van der Waals contacts, avoiding lithography-induced contamination at

#### the interface.[6]

- Graphene Exfoliation: Mechanically exfoliate two single-layer graphene stripes onto a 300 nm SiO<sub>2</sub>/Si substrate. These will serve as the source and drain back-contacts.

- MoS<sub>2</sub> Channel Transfer: Mechanically exfoliate a MoS<sub>2</sub> flake (monolayer or multilayer).

Using a dry alignment transfer technique, place the MoS<sub>2</sub> flake directly on top of the two graphene electrodes, bridging the gap between them. This creates an atomically clean van der Waals interface.[6]

- Metal Lead Fabrication:

- Use standard electron-beam lithography to define the pattern for the final metal leads that will connect to the graphene contacts.

- Deposit Cr/Au (e.g., 10/50 nm) via thermal evaporation.

- Perform a lift-off process to remove excess metal, leaving the final device structure.

- Characterization: Perform electrical transport studies in a dark, vacuum environment to characterize the device, which should exhibit linear I-V behavior indicative of Ohmic contacts.

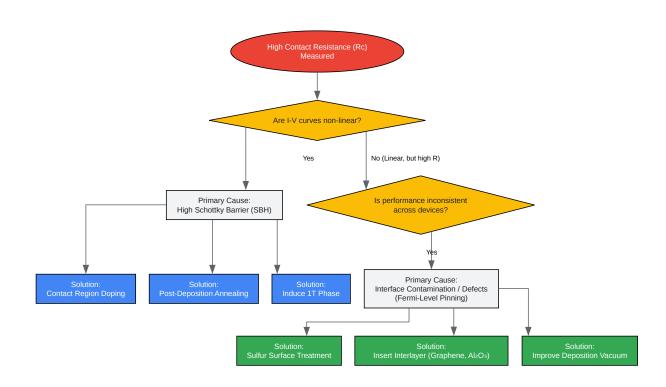

### **Troubleshooting Logic for High Contact Resistance**

The following diagram provides a logical workflow for diagnosing and addressing high contact resistance in your MoS<sub>2</sub> devices.

Click to download full resolution via product page

Troubleshooting flowchart for high contact resistance.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

• 1. pubs.aip.org [pubs.aip.org]

#### Troubleshooting & Optimization

- 2. pubs.acs.org [pubs.acs.org]

- 3. Influence of Metal¿MoS2 Interface on MoS2 Transistor Performance: Comparison of Ag and Ti Contacts | NIST [nist.gov]

- 4. Influence of metal-MoS2 interface on MoS2 transistor performance: comparison of Ag and Ti contacts. | Semantic Scholar [semanticscholar.org]

- 5. researchgate.net [researchgate.net]

- 6. arxiv.org [arxiv.org]

- 7. researchgate.net [researchgate.net]

- 8. Reducing MoS2 FET contact resistance by stepped annealing to optimize device performance Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 9. researchgate.net [researchgate.net]

- 10. pubs.aip.org [pubs.aip.org]

- 11. [PDF] Surface State Engineering of Metal/MoS2 Contacts Using Sulfur Treatment for Reduced Contact Resistance and Variability | Semantic Scholar [semanticscholar.org]

- 12. arxiv.org [arxiv.org]

- 13. researchgate.net [researchgate.net]

- 14. pubs.acs.org [pubs.acs.org]

- 15. ieeexplore.ieee.org [ieeexplore.ieee.org]

- 16. pubs.aip.org [pubs.aip.org]

- 17. Low resistance metal contacts to MoS2 devices with nickel-etched-graphene electrodes -PubMed [pubmed.ncbi.nlm.nih.gov]

- 18. Annealed Ag contacts to MoS2 field-effect transistors [ouci.dntb.gov.ua]

- 19. scite.ai [scite.ai]

- 20. engineering.purdue.edu [engineering.purdue.edu]

- To cite this document: BenchChem. [Technical Support Center: Reducing Contact Resistance in MoS<sub>2</sub> Transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1676702#reducing-contact-resistance-in-mostransistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

### BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com