Check Availability & Pricing

# Technical Support Center: Reducing Charge Trapping in TCP-Based Organic Semiconductors

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                                        |           |

|----------------------|----------------------------------------|-----------|

| Compound Name:       | 1,3,5-Tri(9H-carbazol-9-<br>yl)benzene |           |

| Cat. No.:            | B139494                                | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with tetracyanophenyl-porphyrin (TCP)-based organic semiconductors. The information provided is designed to help address common experimental challenges related to charge trapping, a critical factor limiting device performance.

### Frequently Asked Questions (FAQs)

Q1: What is charge trapping in TCP-based organic semiconductors and how does it affect my device?

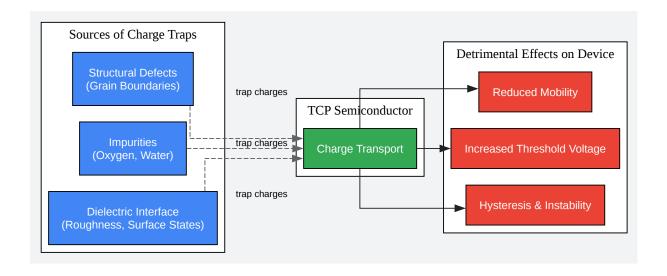

A1: Charge trapping is a phenomenon where charge carriers (electrons or holes) moving through the TCP semiconductor layer become localized at defect sites, impurities, or grain boundaries.[1][2] These trapped charges are temporarily or permanently unable to contribute to the electrical current, leading to several adverse effects on device performance:

- Reduced Charge Carrier Mobility: Trapped charges scatter mobile carriers, reducing their overall velocity in the applied electric field.

- Increased Threshold Voltage: A higher gate voltage is required to turn on the transistor as the initial applied voltage must first fill the trap states before accumulating free carriers in the channel.[2]

### Troubleshooting & Optimization

- Device Instability and Hysteresis: The slow trapping and de-trapping of charges can lead to a shift in the threshold voltage during operation and a difference in the current-voltage characteristics depending on the direction of the voltage sweep (hysteresis).[2]

- Lower ON/OFF Ratio: Increased off-current due to trapped charges can reduce the switching performance of transistors.

Q2: What are the common sources of charge traps in TCP-based semiconductor devices?

A2: Charge traps in TCP-based devices can be intrinsic to the material or introduced during fabrication and handling. Common sources include:

- Structural Defects: Imperfections in the molecular packing of the TCP thin film, such as grain boundaries and disordered regions, can create energetic traps.

- Impurities: Contaminants from synthesis or the environment, such as oxygen and water molecules, are known to create trap states.[1]

- Dielectric Interface: The interface between the TCP semiconductor and the gate dielectric is a critical region where charge trapping can occur due to surface roughness, dangling bonds, or chemical residues.[1][2]

- Processing Solvents: Residual solvent molecules within the semiconductor film can act as charge traps.

Q3: How can I characterize the extent of charge trapping in my TCP-based transistors?

A3: Several electrical characterization techniques can be used to quantify charge trapping:

- Subthreshold Swing (SS): The subthreshold swing, extracted from the transfer characteristics of a field-effect transistor (FET), provides an estimate of the total trap density at the semiconductor/dielectric interface. A steeper subthreshold swing (smaller SS value) indicates a lower trap density.

- Temperature-Dependent Mobility: Measuring the charge carrier mobility at different temperatures can reveal the presence of shallow or deep trap states. In many trap-limited transport models, mobility shows a characteristic temperature dependence.

• Gate Bias Stress Measurements: Applying a constant gate voltage for an extended period and observing the shift in the threshold voltage can provide information about the stability of the device and the dynamics of charge trapping.[2]

## **Troubleshooting Guides**

This section provides solutions to common problems encountered during the fabrication and testing of TCP-based organic semiconductor devices.

Issue 1: Low Charge Carrier Mobility in a TCP-based OFET

## Troubleshooting & Optimization

Check Availability & Pricing

| Possible Cause                              | Troubleshooting Step                                                                                                                                                                                                                                           | Expected Outcome                                                                                                                                               |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Poor Film Morphology / High<br>Trap Density | Optimize the deposition conditions of the TCP layer. For solution-processed films, experiment with different solvents, solution concentrations, and substrate temperatures. For vacuum-deposited films, control the substrate temperature and deposition rate. | An optimized deposition process will lead to a more ordered film with larger crystalline domains and fewer grain boundaries, resulting in higher mobility.     |

| Unfavorable Dielectric<br>Interface         | Treat the surface of the gate dielectric before depositing the TCP layer. Common treatments include using self-assembled monolayers (SAMs) like octadecyltrichlorosilane (OTS) or hexamethyldisilazane (HMDS).[1][2][3]                                        | A well-treated dielectric surface can promote better ordering of the TCP molecules at the interface and passivate surface traps, leading to improved mobility. |

| Residual Impurities                         | Perform a post-deposition thermal annealing step. Annealing can help remove residual solvents and improve the molecular packing of the film. The optimal annealing temperature and time will depend on the specific TCP derivative and substrate.              | A properly annealed film will have a lower density of trap states associated with impurities and structural disorder, resulting in higher mobility.            |

Issue 2: Significant Hysteresis in the Transfer Characteristics

| Possible Cause                                        | Troubleshooting Step                                                                                                                                                                        | Expected Outcome                                                                                                                                |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Mobile Ions in the Dielectric                         | If using a polymer dielectric, ensure it is thoroughly dried before use. For silicon dioxide dielectrics, a high-temperature anneal under vacuum can remove adsorbed water.                 | Reducing mobile ions in the dielectric will minimize their drift under an applied gate bias, thereby reducing hysteresis.                       |

| Slow Charge Trapping/De-<br>trapping at the Interface | Use a gate dielectric with a low density of surface traps. Fluorinated polymer dielectrics like Cytop have been shown to have "cleaner" surfaces with fewer trap sites compared to SiO2.[1] | A cleaner semiconductor-<br>dielectric interface will have<br>fewer sites for slow charge<br>trapping, leading to a reduction<br>in hysteresis. |

| Exposure to Air and Moisture                          | Encapsulate the device to protect it from the ambient environment. Perform all measurements in an inert atmosphere (e.g., a nitrogenfilled glovebox).                                       | Encapsulation will prevent the introduction of extrinsic traps from oxygen and water, improving device stability and reducing hysteresis.[1]    |

## **Quantitative Data Summary**

The following tables summarize typical performance metrics for organic field-effect transistors (OFETs) and the impact of various optimization strategies. Note that these values are illustrative and will vary depending on the specific TCP derivative, device architecture, and experimental conditions.

Table 1: Effect of Dielectric Surface Treatment on Porphyrin-based OFET Performance

| Dielectric       | Surface<br>Treatment | Mobility<br>(cm²/Vs) | Threshold<br>Voltage (V) | ON/OFF Ratio                      |

|------------------|----------------------|----------------------|--------------------------|-----------------------------------|

| SiO <sub>2</sub> | None                 | 0.01 - 0.05          | -20 to -30               | 10 <sup>4</sup> - 10 <sup>5</sup> |

| SiO <sub>2</sub> | HMDS                 | 0.08 - 0.2           | -10 to -15               | > 10 <sup>5</sup>                 |

| SiO <sub>2</sub> | OTS                  | 0.2 - 0.5            | -5 to -10                | > 106                             |

| Cytop            | None                 | 0.3 - 0.8            | -2 to -8                 | > 106                             |

Data compiled from general knowledge of porphyrin-based OFETs and is intended for comparative purposes.

Table 2: Influence of Thermal Annealing on a Solution-Processed Porphyrin Derivative Film

| Annealing Temperature (°C) | Mobility (cm²/Vs)            | Subthreshold Swing (V/dec) |

|----------------------------|------------------------------|----------------------------|

| No Annealing               | 0.02                         | 1.5                        |

| 100                        | 0.08                         | 0.9                        |

| 150                        | 0.25                         | 0.5                        |

| 200                        | 0.15 (degradation may occur) | 0.7                        |

Illustrative data demonstrating the general trend of performance improvement with annealing up to an optimal temperature.

## **Experimental Protocols**

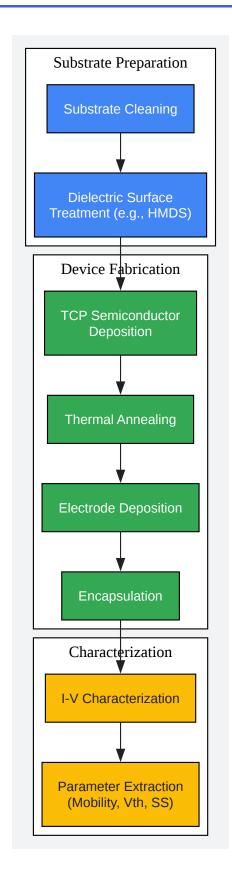

Protocol 1: Dielectric Surface Treatment with Hexamethyldisilazane (HMDS)

- Substrate Cleaning: Sequentially sonicate the SiO<sub>2</sub>/Si substrates in deionized water, acetone, and isopropanol for 15 minutes each.

- Drying: Dry the substrates with a stream of nitrogen gas and bake them on a hotplate at 120°C for 20 minutes to remove any residual moisture.

- UV-Ozone Treatment: Treat the substrates with UV-ozone for 10 minutes to remove organic residues and create a hydrophilic surface.

- HMDS Vapor Deposition: Place the cleaned substrates in a vacuum desiccator along with a small vial containing a few drops of HMDS. Evacuate the desiccator to a base pressure of <1 mTorr. The HMDS vapor will react with the hydroxyl groups on the SiO<sub>2</sub> surface.

- Reaction Time: Allow the reaction to proceed for at least 2 hours at room temperature.

- Post-Treatment Cleaning: Remove the substrates from the desiccator and rinse them with isopropanol to remove any physisorbed HMDS.

- Drying: Dry the substrates with a nitrogen stream. The surface should now be hydrophobic.

- TCP Deposition: Immediately proceed with the deposition of the TCP semiconductor layer.

#### Protocol 2: Thermal Annealing of TCP Thin Films

- Film Deposition: Deposit the TCP thin film onto the desired substrate using your established solution-based or vacuum deposition method.

- Transfer to Inert Atmosphere: Immediately transfer the sample into a nitrogen-filled glovebox or a vacuum chamber to prevent exposure to ambient air.

- Annealing Setup: Place the sample on a hotplate located inside the glovebox or vacuum chamber.

- Temperature Ramping: Slowly ramp up the temperature to the desired annealing temperature (e.g., 150°C) at a rate of 5-10°C per minute to avoid thermal shock.

- Annealing Time: Hold the sample at the target temperature for the desired duration (e.g., 30 minutes). This will need to be optimized for your specific TCP material.

- Cooling: Turn off the hotplate and allow the sample to cool down slowly to room temperature inside the inert atmosphere.

- Device Completion: Proceed with the deposition of the source/drain electrodes and device encapsulation.

### **Visualizations**

Click to download full resolution via product page

Caption: The impact of charge trap sources on device performance.

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. pubs.acs.org [pubs.acs.org]

- 2. researchgate.net [researchgate.net]

- 3. Engineering gate dielectric surface properties for enhanced polymer field-effect transistor performance Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- To cite this document: BenchChem. [Technical Support Center: Reducing Charge Trapping in TCP-Based Organic Semiconductors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b139494#reducing-charge-trapping-in-tcp-based-organic-semiconductors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com