Check Availability & Pricing

# Technical Support Center: Overcoming Lattice Mismatch in InAs Heterostructures

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                 |           |

|----------------------|-----------------|-----------|

| Compound Name:       | Indium arsenide |           |

| Cat. No.:            | B073376         | Get Quote |

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in overcoming challenges associated with lattice mismatch during the growth of **Indium Arsenide** (InAs) heterostructures.

### Frequently Asked Questions (FAQs)

Q1: What is lattice mismatch and why is it a critical issue in InAs heterostructures?

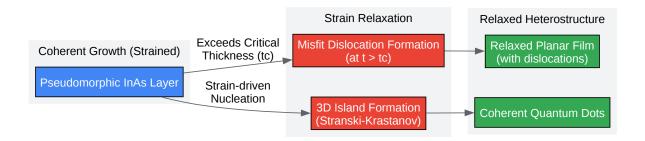

A1: Lattice mismatch refers to the difference in the crystal lattice parameters between two different semiconductor materials. In the context of InAs heterostructures, a significant mismatch exists between InAs and common substrates like Gallium Arsenide (GaAs) (~7.2%) and Silicon (Si) (~11.6%).[1][2] This mismatch induces strain in the epitaxially grown InAs layer. [3] When the strain energy becomes too large, it can be relieved through the formation of defects such as misfit dislocations, threading dislocations, and stacking faults.[3][4] These defects can degrade the crystal quality, affecting the electrical and optical properties of the material and, consequently, the performance and reliability of devices fabricated from it.[3]

Q2: What is the critical thickness for InAs growth on different substrates?

A2: The critical thickness is the maximum thickness an epitaxial layer can be grown without the formation of misfit dislocations to relieve strain. Beyond this thickness, the strain energy becomes sufficient to generate dislocations. The theoretical Matthews-Blakeslee critical thickness for InAs on GaAs is approximately 2 monolayers (ML).[5] However, the

### Troubleshooting & Optimization

experimentally observed critical thickness can vary depending on growth conditions and substrate orientation. For instance, the critical thickness of InAs on GaAs (001) is around 3 ML, but it can be increased to 5 ML on a GaAs substrate misoriented toward the[6] direction.[7] The critical thickness is influenced by factors that affect strain relaxation, such as substrate misorientation.[8]

Q3: What are the primary methods to overcome lattice mismatch when growing InAs on substrates like GaAs or Si?

A3: The primary methods to accommodate the large lattice mismatch include:

- Graded Buffer Layers: This technique involves growing a series of intermediate layers with gradually changing compositions (e.g., InxGa1-xAs on GaAs) to bridge the lattice constant of the substrate and the final InAs layer.[9][10] This gradual change helps to confine misfit dislocations within the buffer layer.

- Intermediate Buffer Layers on Silicon: For growth on Si, a common approach is to use an

initial buffer layer like Gallium Phosphide (GaP) or Germanium (Ge) followed by other defectreducing layers before the growth of the III-V materials.[11][12]

- Growth of Quantum Dots (QDs): The Stranski-Krastanov growth mode allows for the formation of defect-free, strained InAs islands (quantum dots) on a thin wetting layer.[11][13]

This is a widely used method for creating quantum light sources.

- Nanowire Growth: Growing InAs in the form of nanowires allows for lateral strain relaxation, enabling the growth of high-quality, defect-free crystals on mismatched substrates.[14]

- Aspect Ratio Trapping: This method uses patterned substrates with high-aspect-ratio trenches to trap dislocations, preventing them from propagating into the active device layers.

[15]

Q4: How do misfit dislocations form and how do they affect the material properties?

A4: Misfit dislocations are defects that form at the interface between two lattice-mismatched materials to relieve the accumulated strain energy.[4] They are typically introduced once the grown layer exceeds its critical thickness. These dislocations create a network at the interface. [16] While they help in relaxing the strain, they can also act as non-radiative recombination

centers, which can be detrimental to the performance of optoelectronic devices.[17] Furthermore, threading dislocations, which are dislocations that propagate up from the interface into the epitaxial layer, can severely degrade device performance.[17]

## **Troubleshooting Guides**

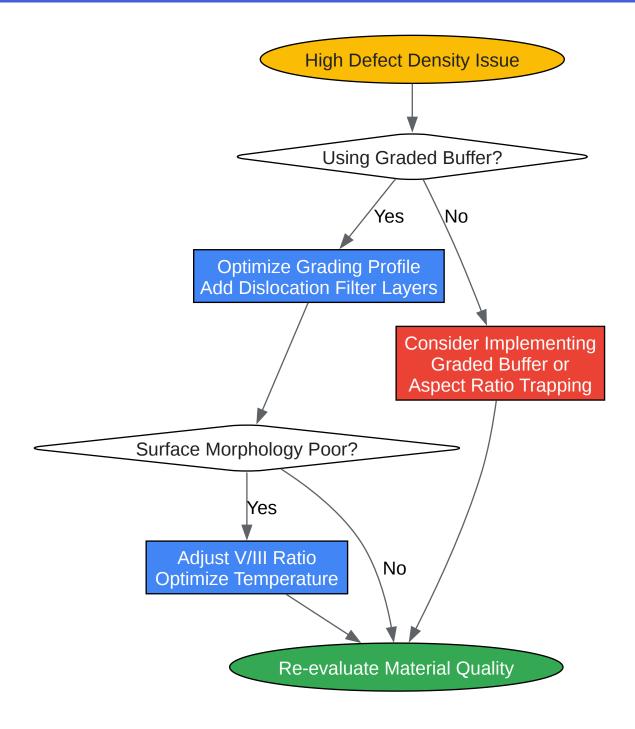

Problem 1: High Density of Threading Dislocations in the InAs Epilayer

## Troubleshooting & Optimization

Check Availability & Pricing

| Symptom                                                                              | Possible Cause                                                               | Troubleshooting Step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Poor photoluminescence (PL) intensity, high reverse leakage current in devices.      | Ineffective dislocation filtering in the buffer layer.                       | 1. Optimize Graded Buffer: If using a graded buffer, ensure the grading profile is gradual enough to allow for efficient dislocation gliding and annihilation. Consider using compositionally undulating step-graded (CUSG) buffers.  [10] 2. Introduce Dislocation Filter Layers (DFLs): Incorporate strained-layer superlattices (e.g., InGaAs/GaAs) within the buffer. The interfaces of the superlattice can bend and terminate threading dislocations.[12] 3. Optimize Growth Temperature: Growth temperature can influence dislocation mobility. A higher temperature can sometimes promote dislocation annihilation, but too high a temperature can lead to other issues like surface roughening.  [18][19] |

| Cross-hatch pattern observed<br>on the surface via Atomic<br>Force Microscopy (AFM). | Strain relaxation through misfit dislocation formation at the interface.[20] | While the cross-hatch pattern is often an indicator of strain relaxation, a very rough surface is undesirable.  Optimize the buffer layer design and growth conditions to achieve a smoother morphology post-relaxation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Problem 2: Poor Surface Morphology of the InAs Layer (e.g., 3D Islanding instead of 2D Growth)

| Symptom                                                  | Possible Cause                                                                                           | Troubleshooting Step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rough surface observed by<br>AFM or Nomarski microscopy. | Growth conditions favoring the Stranski-Krastanov growth mode beyond the intended quantum dot formation. | 1. Adjust V/III Ratio: The ratio of Group V (As) to Group III (In) flux is critical. A lower V/III ratio (more In-rich conditions) can sometimes promote a more planar growth front.[5] [18] 2. Optimize Substrate Temperature: The substrate temperature affects adatom mobility. Lowering the temperature can sometimes suppress the transition to 3D growth.[5] 3. Substrate Offcut: Using a misoriented substrate can influence the growth mode. An offcut towards the <110> direction has been shown to improve crystalline quality and surface morphology for InAs on GaAs. [21] |

| Formation of large, non-<br>uniform islands.             | Coalescence of smaller islands during growth.                                                            | Optimize the growth rate and temperature to control the nucleation density and prevent excessive island coalescence. [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Problem 3: Inconsistent or Poor Optical/Electrical Properties

| Symptom                                              | Possible Cause                                 | Troubleshooting Step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Broad photoluminescence peaks, low carrier mobility. | High density of point defects or dislocations. | 1. Characterize Defects: Use techniques like High-Resolution X-ray Diffraction (HRXRD) and Transmission Electron Microscopy (TEM) to identify the types and density of defects.[3][22] 2. Optimize Growth Purity: Ensure high-purity sources are used in MBE or MOCVD to minimize the incorporation of unintentional impurities that can act as traps. 3. Annealing: Post-growth annealing can sometimes improve material quality by allowing for the rearrangement of atoms and annihilation of some defects. |

| Unintentional n-type conductivity.                   | Presence of native defects or impurities.      | Control the V/III ratio during growth, as an excess of As vacancies can lead to n-type behavior. Ensure a clean growth environment.                                                                                                                                                                                                                                                                                                                                                                            |

# **Quantitative Data Summary**

Table 1: Lattice Constants of InAs and Common Substrates

| Material | Lattice Constant (Å) |

|----------|----------------------|

| InAs     | 6.0583               |

| GaAs     | 5.6533               |

| Si       | 5.431                |

| GaP      | 5.4505               |

| InP      | 5.8687               |

Table 2: Typical Growth Parameters for InAs on GaAs by MBE

| Parameter                          | Value          | Reference |

|------------------------------------|----------------|-----------|

| Substrate Temperature              | 380 - 560 °C   | [18]      |

| Optimal Growth Temperature         | 400 °C         | [18]      |

| As4/In Flux Ratio (BEP)            | 7.5 - 17.5     | [18]      |

| Optimal As4/In Flux Ratio          | 8.5            | [18]      |

| Growth Rate                        | ~0.75 μm/h     | [18]      |

| Resulting Electron Mobility (300K) | ~12,970 cm²/Vs | [18][21]  |

| Resulting Electron Mobility (80K)  | ~22,420 cm²/Vs | [18][21]  |

## **Experimental Protocols**

Methodology 1: Molecular Beam Epitaxy (MBE) Growth of InAs on GaAs

- Substrate Preparation: A GaAs (001) substrate is loaded into the MBE chamber. The native oxide is thermally desorbed at approximately 655 °C under an As4 overpressure.[18]

- GaAs Buffer Layer Growth: A GaAs buffer layer of about 250 nm is grown at 655 °C to ensure an atomically smooth starting surface.[18]

- InAs Growth: The substrate temperature is lowered to the desired InAs growth temperature (e.g., 400 °C). The In and As shutters are opened to initiate InAs deposition at a specific growth rate (e.g., 0.75 μm/h) and V/III flux ratio (e.g., 8.5).[18]

- In-situ Monitoring: Reflection High-Energy Electron Diffraction (RHEED) can be used to monitor the surface reconstruction and the transition from 2D to 3D growth if applicable (e.g., for quantum dot formation).

- Cool Down: After the desired thickness of InAs is grown, the shutters are closed, and the substrate is cooled down under an As overpressure to prevent surface degradation.

Methodology 2: Metal-Organic Chemical Vapor Deposition (MOCVD) Growth of InAs Nanowires on Si

- Substrate Preparation: A Si(111) substrate is cleaned to remove the native oxide, for example, using a buffered oxide etch (BOE) solution followed by a deionized water rinse.

- Loading and Annealing: The substrate is loaded into the MOCVD reactor and annealed in a hydrogen (H2) ambient at a high temperature (e.g., 635 °C) to prepare the surface.[23]

- Nanowire Growth: The temperature is set to the growth temperature (e.g., 550 °C).

Precursors such as Trimethylindium (TMIn) and Arsine (AsH3) are introduced into the reactor to initiate the catalyst-free growth of InAs nanowires.[23]

- Growth Termination: After the desired growth time, the precursor flows are stopped, and the reactor is cooled down under a protective gas flow.

### **Visualizations**

#### Click to download full resolution via product page

Caption: Pathways for strain relaxation in lattice-mismatched InAs heterostructures.

Caption: Structure of a graded buffer layer for lattice mismatch accommodation.

Click to download full resolution via product page

Caption: A logical workflow for troubleshooting high defect densities in InAs heterostructures.

### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. tohoku.repo.nii.ac.jp [tohoku.repo.nii.ac.jp]

- 2. Strain relaxation in InAs heteroepitaxy on lattice-mismatched substrates PMC [pmc.ncbi.nlm.nih.gov]

- 3. A Study of Defects in InAs/GaSb Type-II Superlattices Using High-Resolution Reciprocal Space Mapping [mdpi.com]

- 4. Theoretical Investigations for Strain Relaxation and Growth Mode of InAs Thin layers on GaAs(111)A [mdpi.com]

- 5. pubs.aip.org [pubs.aip.org]

- 6. pubs.aip.org [pubs.aip.org]

- 7. Influence of GaAs Substrate Orientation on InAs Quantum Dots: Surface Morphology, Critical Thickness, and Optical Properties - PMC [pmc.ncbi.nlm.nih.gov]

- 8. researchgate.net [researchgate.net]

- 9. mdpi.com [mdpi.com]

- 10. OPG [opg.optica.org]

- 11. Investigation into the InAs/GaAs quantum dot material epitaxially grown on silicon for O band lasers [jos.ac.cn]

- 12. researchgate.net [researchgate.net]

- 13. Selective Area Epitaxy of Axial Wurtzite -InAs Nanowire on InGaAs NW by MOCVD |

IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 14. pubs.acs.org [pubs.acs.org]

- 15. researchgate.net [researchgate.net]

- 16. pubs.acs.org [pubs.acs.org]

- 17. d-nb.info [d-nb.info]

- 18. pubs.aip.org [pubs.aip.org]

- 19. researchgate.net [researchgate.net]

- 20. researchgate.net [researchgate.net]

- 21. researchgate.net [researchgate.net]

- 22. pubs.acs.org [pubs.acs.org]

- 23. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: Overcoming Lattice Mismatch in InAs Heterostructures]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b073376#overcoming-lattice-mismatch-in-inas-heterostructures]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com