# Technical Support Center: Overcoming Copper Contamination in GaAs Device Fabrication

Author: BenchChem Technical Support Team. Date: December 2025

This guide provides researchers, scientists, and fabrication engineers with a comprehensive resource for troubleshooting and mitigating copper (Cu) contamination in **Gallium Arsenide** (GaAs) device manufacturing.

# **Frequently Asked Questions (FAQs)**

Q1: What are the common sources of copper contamination in a GaAs fabrication environment?

A1: Copper contamination can originate from various sources throughout the fabrication process. Key sources include:

- Processing Equipment: Deposition, dry etching, and electroplating tools can be significant sources.[1][2] Cross-contamination is a major risk in facilities where tools are shared between copper-based processes (like interconnects) and other processes.[1][3][4]

- Wafer Handling and Support: Copper handling foils, particularly in processes like Epitaxial Lift-Off (ELO) for flexible solar cells, can be a direct source of diffusion.[5][6]

- Metallization & Contacts: The use of copper in contact layers, interconnects, or as part of a

backside contact can lead to its diffusion into the active device regions, especially during

subsequent high-temperature annealing steps.[7][8][9]

#### Troubleshooting & Optimization

Facility Environment: Contaminants can be airborne or transferred from surfaces. Wafers

with existing bulk contamination can out-diffuse copper, contaminating process tools or other

wafers they come into contact with.[1][10]

Q2: How does copper contamination detrimentally affect my GaAs device performance?

A2: Copper is highly detrimental to GaAs devices because it acts as a deep-level impurity, creating energy levels within the semiconductor's bandgap.[11] This leads to several performance degradation mechanisms:

- Increased Recombination: The copper-induced trap levels act as efficient non-radiative recombination centers, which reduces the minority carrier lifetime.[5][6][11]

- Reduced Voltage: In solar cells, this enhanced recombination is a primary cause of reduced open-circuit voltage (Voc).[5][6][9]

- Increased Leakage Current: The presence of copper can increase junction leakage currents and degrade the gate oxide integrity in transistors.[3][7][11]

- Threshold Voltage Shifts: Copper contamination has been shown to affect the threshold voltage of transistors.[3][12]

- Physical Defects: Copper tends to aggregate at crystallographic dislocations, which can form localized "hot spots" and reduce the breakdown voltage of power devices.[11]

Q3: Why is copper so mobile in GaAs, and when is the risk of diffusion highest?

A3: Copper is a fast-diffusing impurity in GaAs, primarily moving through an interstitial mechanism.[13][14][15] Its high diffusivity means it can move from contaminated surfaces or contacts into the bulk of the wafer relatively quickly. The risk of diffusion is significantly elevated during high-temperature processes, such as thermal annealing. Studies have shown that heat treatments at temperatures of 300°C and above can induce significant copper diffusion, leading to device degradation.[5][6][7]

Q4: What are the primary analytical methods to detect and quantify copper contamination?

A4: Several highly sensitive techniques are used to identify and measure copper contamination on the surface or within the bulk of a wafer:

- Secondary Ion Mass Spectrometry (SIMS): Excellent for providing a depth profile of copper concentration, showing how far it has diffused into the device layers.[7][8]

- Total Reflection X-ray Fluorescence (TXRF): A non-destructive method ideal for quantifying surface metal contamination.[1]

- Vapor Phase Decomposition (VPD) with ICP-MS: A highly sensitive technique where the surface oxide is decomposed by acid vapor and the condensed residue is analyzed by Inductively Coupled Plasma Mass Spectrometry (ICP-MS) to measure trace metal contamination.[1][16]

- Deep Level Transient Spectroscopy (DLTS): Used to characterize the electronic properties of deep-level traps, such as those introduced by copper, within the semiconductor's bandgap.

# **Troubleshooting Guides**

Problem 1: My solar cell's open-circuit voltage (Voc) or my transistor's leakage current has degraded after an annealing step.

- Potential Cause: High-temperature annealing is a common trigger for copper diffusion from contaminated surfaces or copper-containing contacts into the active regions of the device.[5]

[6][7]

- Troubleshooting Steps:

- Identify Potential Sources: Review the fabrication process. Were copper-containing materials (e.g., support foils, contacts) present on the wafer during the anneal? Was the wafer processed in a tool previously used for copper metallization?

- Analyze for Copper: Use SIMS to analyze a test wafer from the same batch to confirm if copper has diffused into the active layers. Correlate the diffusion depth with the device junction depth.

- Implement Preventative Measures:

- If the source is a contact layer, investigate incorporating a diffusion barrier layer (e.g., Ti/Pt) between the copper and the semiconductor.[5][6]

- Consider altering the process flow to perform high-temperature annealing before depositing copper layers.[7][8]

Problem 2: I suspect cross-contamination from shared fabrication equipment.

- Potential Cause: Tools used for both copper and non-copper processes (e.g., lithography, metrology, deposition) are a primary vector for cross-contamination.[1][4] Copper particles or residues can be transferred from the tool to a "clean" wafer.

- Troubleshooting Steps:

- Isolate the Tool: Identify all shared equipment that the affected wafers passed through after a known copper-processed batch.

- Monitor Tool Contamination: Establish a protocol for wiping down critical parts of the shared tool and analyzing the wipes for copper traces. Use "witness wafers" (clean wafers run through the tool) and analyze their surface contamination using TXRF or VPD-ICP-MS.

- Implement Control Protocols:

- Strictly segregate copper and non-copper wafer carriers.[4]

- Develop and enforce cleaning procedures for shared tools between runs.[1]

- If contamination is severe and persistent, the long-term solution is to dedicate separate tools for copper processing.[1]

#### **Quantitative Data Summary**

Table 1: Effect of Copper Contamination and Annealing on GaAs Solar Cell Performance

| Condition                      | Annealing<br>Temperature | Observation                                             | Key<br>Performance<br>Impact                        | Reference |

|--------------------------------|--------------------------|---------------------------------------------------------|-----------------------------------------------------|-----------|

| Cu-backed ELO<br>cell          | ≥ 300°C                  | Signs of Cu<br>diffusion present.                       | Significant decrease in Open-Circuit Voltage (Voc). | [5],[6]   |

| Cu-backed ELO<br>cell          | ≥ 300°C                  | Short-Circuit Current (Jsc) remains largely unaffected. | Voc is the most sensitive parameter.                | [5]       |

| Flexible cell w/<br>Cu plating | High-Temp<br>Annealing   | Excess copper diffusion into the active region.         | Degradation in overall solar cell performance.      | [7],[8]   |

| Au/Cu front<br>contact grid    | 200°C                    | Intermixing of Au °C and Cu in the contact only.        |                                                     | [9]       |

| Au/Cu front contact grid       | ≥ 250°C                  | Recrystallization and diffusion into the active region. | Decrease in Voc<br>due to Cu trap<br>levels.        | [9]       |

Table 2: Comparison of Common Copper Detection Methods

| Technique  | Measures                       | Typical Use<br>Case                                         | Advantages                                             | Disadvanta<br>ges                         | Reference |

|------------|--------------------------------|-------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|-----------|

| SIMS       | Bulk<br>Concentratio<br>n      | Depth profiling of Cu diffusion.                            | High sensitivity, excellent depth resolution.          | Destructive, can be complex to quantify.  | [7],[8]   |

| TXRF       | Surface<br>Concentratio<br>n   | Routine<br>monitoring of<br>surface<br>contaminatio<br>n.   | Non-<br>destructive,<br>rapid<br>analysis.             | Less sensitive to bulk contaminatio n.    | [1]       |

| VPD-ICP-MS | Surface<br>Concentratio<br>n   | High-<br>sensitivity<br>analysis of<br>wafer<br>surfaces.   | Extremely low detection limits.                        | Destructive, requires sample preparation. | [1],[16]  |

| DLTS       | Bulk<br>Electrical<br>Activity | Characterizin<br>g Cu-induced<br>electronic<br>trap levels. | Directly measures impact on semiconducto r properties. | Measures electrically active traps only.  | [1]       |

# Experimental Protocols & Visualizations Protocol 1: Wet Chemical Cleaning for Surface Copper Removal

This protocol describes a common approach for removing metallic contaminants from a GaAs wafer surface by etching a very thin surface layer.

#### Methodology:

Organic Clean: Begin by cleaning the wafer with standard organic solvents (e.g., acetone, methanol, isopropanol) to remove any organic residues.

## Troubleshooting & Optimization

- Initial Etch & Oxidation: Immerse the wafer in a solution of NH<sub>4</sub>OH: H<sub>2</sub>O<sub>2</sub>: H<sub>2</sub>O (1:1:10). This step etches a thin layer of GaAs, removing surface metallic contaminants and forming a thin, passivating oxide layer.[17]

- Second Etch: Following a deionized (DI) water rinse, immerse the wafer in a solution of HCI:  $H_2O_2: H_2O$  (1:1:20) to continue the removal of metallic ions.[17]

- Oxide Strip: After another DI water rinse, immerse the wafer in a solution of NH₄OH: H₂O

(1:5) to strip the oxide layer formed in the previous steps.[17]

- Final Rinse & Dry: Thoroughly rinse the wafer with DI water and dry it using a nitrogen gun.

Note: Always use appropriate personal protective equipment (PPE) and perform these steps in a certified fume hood.

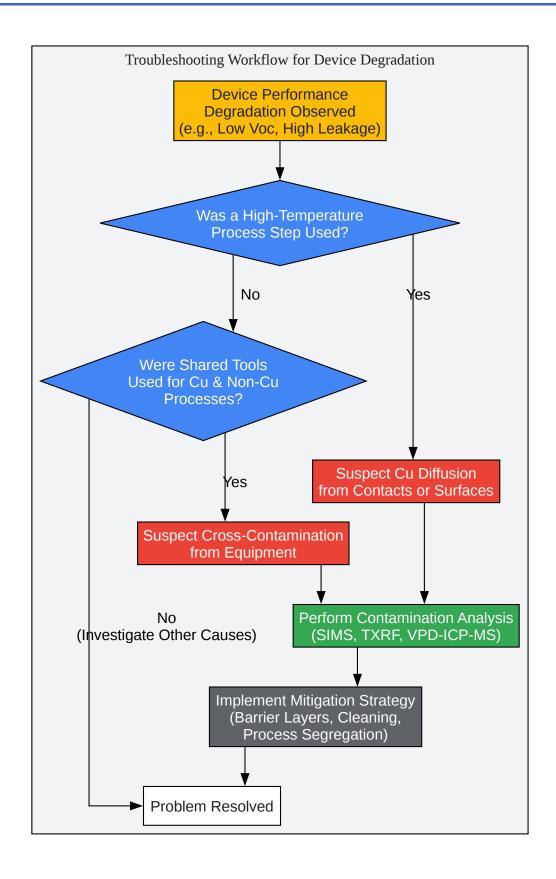

Click to download full resolution via product page

Caption: A logical workflow for troubleshooting GaAs device degradation suspected to be caused by copper contamination.

### **Protocol 2: Gettering for Impurity Mitigation**

Gettering is a process that moves contaminants from the active device region to predetermined "sinks" within the wafer bulk or on its backside, rendering them electrically harmless.

Methodology (Intrinsic Gettering Example):

- Wafer Selection: Start with a Czochralski-grown wafer containing a sufficient concentration of interstitial oxygen.

- Denuding Anneal: Perform a high-temperature anneal (e.g., >1100°C) in an inert or slightly oxidizing atmosphere. This step causes oxygen to out-diffuse from the near-surface region, creating a "denuded zone" that will be free of defects.

- Nucleation Anneal: Follow with a low-temperature anneal (e.g., 650-750°C) to nucleate oxygen precipitates in the bulk of the wafer, below the denuded zone.

- Precipitate Growth Anneal: Finally, use a medium-temperature anneal (e.g., ~1000°C) to grow the oxygen precipitates. These precipitates and the surrounding dislocation loops act as the gettering sites.[18]

- Device Fabrication: Fabricate the devices in the clean, denuded zone. During subsequent thermal steps, mobile copper impurities will be trapped by the gettering sites in the wafer bulk.[18][19]

#### Click to download full resolution via product page

Caption: Diagram of intrinsic and extrinsic gettering, where Cu impurities migrate to trapping sites during annealing.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. rdworldonline.com [rdworldonline.com]

- 2. electramet.com [electramet.com]

- 3. electrochem.org [electrochem.org]

- 4. US9093506B2 Process for fabricating gallium arsenide devices with copper contact layer

Google Patents [patents.google.com]

- 5. repository.ubn.ru.nl [repository.ubn.ru.nl]

- 6. repository.ubn.ru.nl [repository.ubn.ru.nl]

- 7. The Diffusion Effect of Copper on the Flexible GaInP/GaAs Solar Cells | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 8. researchgate.net [researchgate.net]

- 9. researchgate.net [researchgate.net]

- 10. Types of Contamination that can Affect your Wafer [waferworld.com]

- 11. researchgate.net [researchgate.net]

- 12. ir.lib.nycu.edu.tw [ir.lib.nycu.edu.tw]

- 13. researchgate.net [researchgate.net]

- 14. The behaviour of copper on gallium arsenide UBC Library Open Collections [open.library.ubc.ca]

- 15. pubs.aip.org [pubs.aip.org]

- 16. researchgate.net [researchgate.net]

- 17. jos.ac.cn [jos.ac.cn]

- 18. Classifications of Gettering Process [waferworld.com]

- 19. youtube.com [youtube.com]

- To cite this document: BenchChem. [Technical Support Center: Overcoming Copper Contamination in GaAs Device Fabrication]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b074776#overcoming-issues-with-copper-contamination-in-gaas-device-fabrication]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com