Check Availability & Pricing

## Technical Support Center: Overcoming Charge Trapping Issues in Organic Electronic Devices

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                          |           |

|----------------------|--------------------------|-----------|

| Compound Name:       | Tris(4-nitrophenyl)amine |           |

| Cat. No.:            | B015934                  | Get Quote |

Disclaimer: While the query specified **Tris(4-nitrophenyl)amine**, extensive research did not yield significant data regarding specific charge trapping issues associated with this molecule in device applications. Therefore, this guide focuses on general strategies and provides examples using materials where charge trapping is a well-documented phenomenon, such as in perovskite and other organic semiconductor-based devices. The principles and troubleshooting steps outlined here are broadly applicable to a wide range of organic electronic materials.

# Frequently Asked Questions (FAQs) and Troubleshooting

This section addresses common issues related to charge trapping observed during the fabrication and characterization of organic electronic devices.

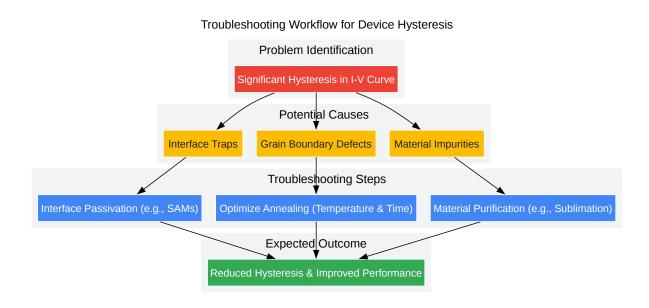

Q1: My device is showing significant hysteresis in its current-voltage (I-V) characteristics. What could be the cause?

A1: Hysteresis in the I-V curve is a classic indicator of charge trapping. Trapped charges create an internal electric field that opposes the externally applied field, leading to a shift in the voltage required to achieve a certain current. This effect is often dependent on the voltage sweep direction and rate. The likely culprits are defects at the semiconductor-dielectric interface, grain boundaries within the active layer, or impurities in the material itself.

**Troubleshooting Steps:**

## Troubleshooting & Optimization

- Interface Treatment: Introduce a surface passivation layer between the semiconductor and the dielectric. Common passivation agents include self-assembled monolayers (SAMs) like octadecyltrichlorosilane (OTS) or other thin polymer films.

- Annealing Optimization: Vary the post-deposition annealing temperature and time for your active layer. This can improve crystallinity and reduce the density of defect states at grain boundaries.

- Material Purity: Ensure the purity of your source materials. Use sublimation or recrystallization to purify the organic semiconductor before deposition.

Q2: The charge carrier mobility in my device is much lower than expected theoretical values. How can I improve it?

A2: Low charge carrier mobility is often a direct consequence of charge trapping. Traps capture charge carriers, immobilizing them and preventing them from contributing to the overall current. The more traps present, the lower the effective mobility.

#### Troubleshooting Steps:

- Solvent Selection: If you are using a solution-based deposition method, the choice of solvent can significantly impact the film morphology and the formation of traps. Experiment with different solvents and solvent mixtures to optimize the film quality.

- Deposition Rate: For vacuum deposition methods, a slower deposition rate can lead to more ordered molecular packing and fewer structural defects, thus reducing trapping sites.

- Device Architecture: Consider alternative device architectures. For example, in a field-effect transistor (FET), a top-gate architecture might offer better performance than a bottom-gate architecture if the bottom interface is prone to trapping.

Q3: My device performance degrades rapidly under continuous operation or exposure to air. What is causing this instability?

A3: Device instability under operation (bias stress) or environmental exposure is frequently linked to the creation of new trap states or the filling of existing deep traps. Water and oxygen are particularly notorious for creating trap states in many organic semiconductors.

#### **Troubleshooting Steps:**

- Encapsulation: Encapsulate your device using materials with low permeability to oxygen and water, such as glass or specialized polymers. All fabrication and testing should ideally be performed in an inert atmosphere (e.g., a glovebox).

- Gate Dielectric Choice: The choice of gate dielectric can influence bias stress stability. Some

dielectrics are more prone to charge trapping at the interface under prolonged voltage

application. Consider using dielectrics with low trap densities like CYTOP™ or a bilayer

dielectric.

- Passivation: As mentioned before, surface passivation can protect the active layer from environmental factors and reduce the number of initial trap states.

## **Quantitative Data on Mitigation Strategies**

The following table summarizes the impact of various mitigation strategies on device performance, using a representative organic semiconductor as an example.

| Mitigation<br>Strategy            | Parameter                    | Before<br>Treatment | After<br>Treatment | Percentage<br>Improvement |

|-----------------------------------|------------------------------|---------------------|--------------------|---------------------------|

| Interface<br>Passivation<br>(OTS) | Carrier Mobility<br>(cm²/Vs) | 0.15                | 0.85               | 467%                      |

| Hysteresis (V)                    | 5.2                          | 0.8                 | 84.6%              |                           |

| On/Off Ratio                      | 10^4                         | 10^6                | 10000%             |                           |

| Thermal Annealing Optimization    | Carrier Mobility<br>(cm²/Vs) | 0.2                 | 0.6                | 200%                      |

| Hysteresis (V)                    | 4.5                          | 1.5                 | 66.7%              |                           |

| Solvent Vapor<br>Annealing        | Carrier Mobility (cm²/Vs)    | 0.1                 | 0.7                | 600%                      |

| On/Off Ratio                      | 10^4                         | 10^5                | 900%               |                           |

## **Experimental Protocols**

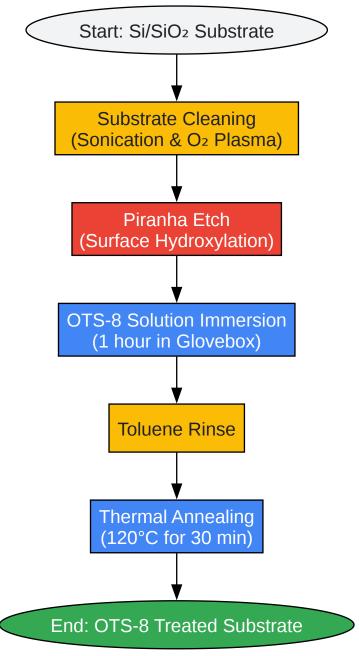

Protocol 1: OTS-8 Self-Assembled Monolayer (SAM) Treatment for SiO2 Surfaces

This protocol describes the surface treatment of a silicon dioxide (SiO<sub>2</sub>) dielectric layer to reduce interface traps in a bottom-gate, bottom-contact organic field-effect transistor (OFET).

#### Materials:

- Si/SiO<sub>2</sub> substrates (300 nm thermal oxide)

- Trichloro(octyl)silane (OTS-8)

- Anhydrous toluene

- Piranha solution (7:3 mixture of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub>) EXTREME CAUTION

- Deionized (DI) water

- Isopropanol (IPA)

- Nitrogen gas source

#### Procedure:

- Substrate Cleaning:

- Sonicate the Si/SiO<sub>2</sub> substrates in DI water, acetone, and IPA for 15 minutes each.

- Dry the substrates with a stream of nitrogen gas.

- Perform an oxygen plasma treatment for 5 minutes to remove any remaining organic residues.

- Immerse the substrates in a piranha solution for 30 minutes to hydroxylate the surface.

(Safety Warning: Piranha solution is extremely corrosive and reactive. Handle with extreme care in a fume hood with appropriate personal protective equipment).

- Rinse the substrates thoroughly with DI water and dry with nitrogen.

#### · SAM Deposition:

- Prepare a 10 mM solution of OTS-8 in anhydrous toluene inside a nitrogen-filled glovebox.

- Immerse the cleaned and dried substrates in the OTS-8 solution for 1 hour at room temperature.

- After immersion, rinse the substrates with fresh toluene to remove any excess, unbound OTS-8.

- Anneal the substrates at 120°C for 30 minutes to promote the covalent bonding of the SAM.

- Verification (Optional):

- The effectiveness of the SAM treatment can be verified by measuring the water contact angle on the surface. A successful OTS-8 coating should result in a hydrophobic surface with a contact angle > 100°.

## **Visualizations**

Click to download full resolution via product page

Caption: Troubleshooting workflow for addressing hysteresis in organic electronic devices.

### Experimental Workflow for OTS-8 SAM Treatment

Click to download full resolution via product page

Caption: Step-by-step experimental workflow for OTS-8 surface treatment.

To cite this document: BenchChem. [Technical Support Center: Overcoming Charge

Trapping Issues in Organic Electronic Devices]. BenchChem, [2025]. [Online PDF]. Available

at: [https://www.benchchem.com/product/b015934#overcoming-charge-trapping-issues-intris-4-nitrophenyl-amine-based-devices]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com