# Technical Support Center: Overcoming Challenges in Scaling Down Silicon-Based Transistors

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |          |           |

|----------------------|----------|-----------|

| Compound Name:       | Silicon  |           |

| Cat. No.:            | B1239273 | Get Quote |

This guide provides researchers, scientists, and engineers with troubleshooting advice and frequently asked questions (FAQs) related to the experimental challenges encountered when scaling down **silicon**-based transistors.

# Section 1: Frequently Asked Questions (FAQs) & Troubleshooting

This section addresses common issues in a question-and-answer format, providing specific, actionable guidance.

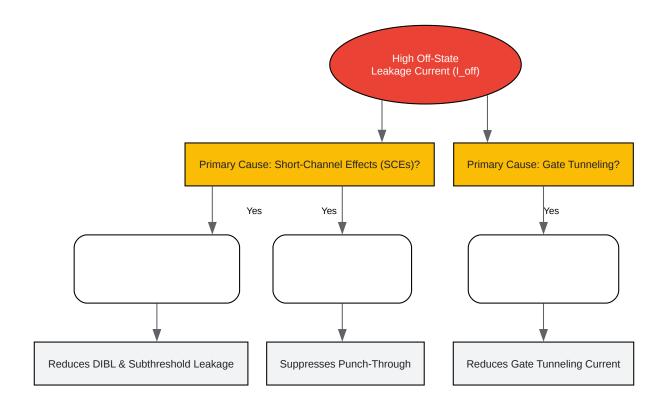

# **Issue 1: Increased Off-State Leakage Current**

Q1: My sub-10nm transistor exhibits significantly higher off-state leakage current (I\_off) than predicted by long-channel models. What are the primary causes and how can I mitigate this?

A1: High I\_off in scaled transistors is typically due to a combination of short-channel effects (SCEs) and quantum mechanical phenomena. The primary culprits are:

• Subthreshold Leakage: As threshold voltage (Vth) is scaled down to maintain performance at lower supply voltages, the gate loses its ability to completely turn the transistor off.[1][2] This allows a diffusion current to flow between the source and drain even when the gate-source voltage is below Vth.[2]

- Gate-Induced Drain Leakage (GIDL): High electric fields at the drain-gate overlap region can cause band-to-band tunneling, creating leakage current.[3]

- Gate Oxide Tunneling: With gate dielectric thicknesses shrinking to a few nanometers, electrons can tunnel directly through the insulator from the gate to the channel, or from the source/drain to the gate.[1][4][5] This becomes a dominant leakage mechanism in technologies below 100nm.[5][6]

- Drain-Induced Barrier Lowering (DIBL): In short-channel devices, the drain's electric field can lower the potential barrier at the source, making it easier for electrons to be injected into the channel, thus increasing leakage.[7][8]

#### **Troubleshooting Steps:**

- Architectural Modification: Transition from planar MOSFETs to multi-gate architectures like

FinFETs or Gate-All-Around (GAA) FETs. These structures provide superior electrostatic

control over the channel, significantly reducing DIBL and subthreshold leakage.[9][10][11][12]

GAAFETs, where the gate fully surrounds the channel, offer the best control.[9][11][12]

- Material Enhancement (High-k Dielectrics): Replace the traditional Silicon Dioxide (SiO<sub>2</sub>)

gate dielectric with a high-k material like Hafnium Oxide (HfO<sub>2</sub>). This allows for a physically

thicker dielectric layer while maintaining the same equivalent oxide thickness (EOT),

drastically reducing gate tunneling current.[13]

- Doping Profile Engineering: Employ non-uniform doping techniques, such as halo or pocket implants, to create localized, highly doped regions near the source and drain. This helps to suppress punch-through and reduce the influence of the drain field on the source barrier.[7]

# **Issue 2: Device Performance Variability**

Q2: I'm observing significant variations in threshold voltage (Vth) across identical transistors on the same die. What is causing this and how can it be controlled?

A2: At nanoscale dimensions, device variability is a major challenge, primarily driven by:

Random Dopant Fluctuation (RDF): When the number of dopant atoms in the channel region

is only in the tens or hundreds, statistical variations in their exact number and position can

cause significant fluctuations in Vth.[14][15] This is a fundamental challenge as device dimensions shrink.[13][14]

Line Edge Roughness (LER): Imperfections in the lithography and etching processes lead to variations in the width of the gate and fin structures. This geometric variation directly translates into electrical performance variation.

#### **Troubleshooting Steps:**

- Adopt Undoped or Lightly-Doped Channels: Architectures like FinFETs and GAAFETs can be designed with undoped or lightly doped channels, which inherently suppresses RDF.[15]

- Transition to GAAFETs: Compared to FinFETs, GAAFETs have shown better resilience to variability induced by effects like metal gate granularity (MGG) and LER, especially at sub-10nm gate lengths.[16]

- Improve Lithography and Etching Processes: The adoption of Extreme Ultraviolet (EUV)

lithography provides higher resolution and can reduce LER compared to older deep

ultraviolet (DUV) multi-patterning techniques.[17] However, EUV itself has challenges with

stochastics that must be carefully managed.[18]

## **Issue 3: Interconnect and Thermal Bottlenecks**

Q3: My circuit performance is not scaling as expected with transistor size. I suspect issues with interconnects and heat. How can I diagnose and address these problems?

A3: As transistors get smaller and faster, the performance of the overall circuit becomes limited by the wires (interconnects) that connect them and the heat they generate.

- Interconnect Bottleneck: The resistance-capacitance (RC) delay of the copper interconnects

does not scale at the same rate as the transistor gate delay.[19] Tightly packed wires lead to

increased parasitic capacitance and resistance, causing signals to propagate more slowly

and consume more power.[19][20] This problem becomes increasingly severe at each

technology node.[19]

- Heat Dissipation: The increased density of transistors, especially in 3D stacked architectures, leads to higher power density and significant heat generation.[21] Inadequate

heat removal can degrade performance, reduce reliability, and cause device failure.[22][23]

#### **Troubleshooting Steps:**

- Interconnect Material Research: Explore alternatives to copper for the narrowest interconnect layers. Materials like Cobalt (Co) and Ruthenium (Ru) are being investigated as they can offer lower resistivity at very small dimensions.[19][24]

- 3D Integration and Thermal Management: For 3D ICs, incorporate thermal management solutions directly into the architecture. This includes:

- Thermal Through-Silicon Vias (TTSVs): These are vertical interconnects designed specifically for heat conduction, providing a path for heat to escape from stacked dies.[23]

- Microfluidic Cooling: Embed micro-channels within the chip stack to circulate a dielectric coolant, actively removing heat from the hottest layers.[25]

- High-Conductivity Insulators: Replace standard interlayer dielectrics with materials that have high thermal conductivity, such as Aluminum Nitride (AIN) or hexagonal Boron Nitride (hBN), to improve passive heat spreading.[26]

Section 2: Quantitative Data Summaries

Table 1: Performance Comparison of Transistor

Architectures (Planar vs. FinFET vs. GAAFET)

| Parameter             | Planar FET (28nm)     | FinFET (7nm)      | GAAFET (3nm)                   |

|-----------------------|-----------------------|-------------------|--------------------------------|

| Electrostatic Control | Poor                  | Good              | Excellent[9]                   |

| Subthreshold Slope    | > 80 mV/dec           | ~65-70 mV/dec     | < 65 mV/dec                    |

| Static Power Leakage  | High                  | Reduced           | ~25-30% lower vs.<br>FinFET[9] |

| Dynamic Power         | Baseline              | Reduced           | ~10-15% lower vs.<br>FinFET[9] |

| Drive Current         | Baseline              | High              | Higher than FinFET[11]         |

| Key Scaling Limiter   | Short-Channel Effects | Fin Width Scaling | Manufacturing Complexity[12]   |

# **Table 2: Properties of Common High-k Gate Dielectric Materials**

| Material                                 | Dielectric Constant<br>(k) | Band Gap (eV) | Conduction Band<br>Offset with Si (eV) |

|------------------------------------------|----------------------------|---------------|----------------------------------------|

| SiO <sub>2</sub> (Baseline)              | 3.9                        | 9.0           | 3.2                                    |

| Al <sub>2</sub> O <sub>3</sub> (Alumina) | ~9                         | 8.8           | 2.8                                    |

| HfO <sub>2</sub> (Hafnia)                | ~25                        | 5.8           | 1.5                                    |

| ZrO <sub>2</sub> (Zirconia)              | ~25                        | 5.8           | 1.4                                    |

Note: A higher 'k' value allows for a thicker film to reduce leakage, but a sufficient band offset (>1 eV) is critical to prevent Schottky emission.

# **Section 3: Experimental Protocols**

Protocol 1: Atomic Layer Deposition (ALD) of HfO<sub>2</sub> Highk Dielectric

# Troubleshooting & Optimization

This protocol outlines the key steps for depositing a Hafnium Oxide (HfO<sub>2</sub>) thin film on a **silicon** substrate using ALD, a common technique for creating high-quality, uniform dielectric layers.

Objective: To deposit a conformal, pinhole-free HfO2 film with precise thickness control.

#### Materials & Equipment:

- ALD Reactor Chamber

- P-type Silicon (100) wafers

- Hafnium precursor: Tetrakis(dimethylamido)hafnium(IV) (TDMAH)

- Oxidant precursor: Deionized (DI) water (H<sub>2</sub>O) or Ozone (O<sub>3</sub>)

- High-purity Nitrogen (N2) gas for purging

- Substrate cleaning solutions (e.g., Piranha etch, HF dip)

#### Methodology:

- Substrate Preparation: a. Perform a standard RCA clean or Piranha etch on the silicon

wafer to remove organic residues. b. Execute a dilute hydrofluoric acid (HF) dip to remove

the native oxide and create a hydrogen-terminated surface. This is a critical step for

controlling the interfacial layer.[27] c. Immediately transfer the wafer into the ALD reactor

load-lock to prevent re-oxidation.

- ALD Process Cycle: The process consists of repeated cycles, each adding a sub-monolayer of material. a. Step 1 (TDMAH Pulse): Introduce the TDMAH precursor into the chamber. It will react with the hydroxyl (-OH) groups on the wafer surface. b. Step 2 (N<sub>2</sub> Purge): Purge the chamber with inert N<sub>2</sub> gas to remove any unreacted precursor and gaseous byproducts. c. Step 3 (H<sub>2</sub>O Pulse): Introduce the H<sub>2</sub>O vapor (oxidant) into the chamber. It reacts with the surface-bound hafnium precursor, forming HfO<sub>2</sub> and regenerating the -OH surface termination. d. Step 4 (N<sub>2</sub> Purge): Purge the chamber again with N<sub>2</sub> to remove unreacted water and byproducts.

- Deposition & Annealing: a. Repeat the ALD cycle (Steps 2a-2d) until the desired film thickness is achieved. The growth per cycle is typically ~1 Å. b. Perform a post-deposition anneal (PDA) in an N<sub>2</sub> or O<sub>2</sub> environment. This step is crucial for densifying the film, removing defects, and improving its electrical properties.[27]

- Characterization: a. Use ellipsometry or X-ray reflectometry (XRR) to measure film thickness.

b. Use X-ray photoelectron spectroscopy (XPS) to analyze chemical composition and bonding states at the Si-HfO<sub>2</sub> interface.[27] c. Fabricate metal-insulator-semiconductor (MIS) capacitors to measure electrical properties like capacitance-voltage (C-V) for determining the k-value and leakage current density (J-V).

## **Section 4: Visualizations**

Click to download full resolution via product page

Caption: Troubleshooting workflow for high off-state leakage current.

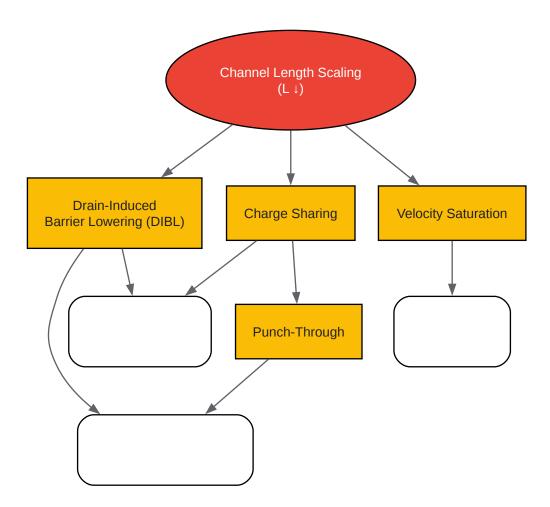

#### Click to download full resolution via product page

Caption: Evolution of transistor architecture from Planar to FinFET and GAAFET.

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. inf.ufrgs.br [inf.ufrgs.br]

- 2. youtube.com [youtube.com]

- 3. mdpi.com [mdpi.com]

- 4. cecs.uci.edu [cecs.uci.edu]

- 5. eecg.utoronto.ca [eecg.utoronto.ca]

- 6. mixsignal.wordpress.com [mixsignal.wordpress.com]

- 7. pnrsolution.org [pnrsolution.org]

- 8. www0.cs.ucl.ac.uk [www0.cs.ucl.ac.uk]

- 9. FinFET Vs GAAFET: Performance Comparison In Nanometer Nodes [eureka.patsnap.com]

- 10. researchgate.net [researchgate.net]

- 11. Comparing FinFETs vs. GAAFETs | System Analysis Blog | Cadence [resources.systemanalysis.cadence.com]

- 12. techlevated.com [techlevated.com]

- 13. ir.lib.nycu.edu.tw [ir.lib.nycu.edu.tw]

- 14. ijert.org [ijert.org]

- 15. taylorandfrancis.com [taylorandfrancis.com]

- 16. researchgate.net [researchgate.net]

- 17. researchgate.net [researchgate.net]

- 18. semiengineering.com [semiengineering.com]

- 19. semiengineering.com [semiengineering.com]

- 20. Interconnect bottleneck Wikipedia [en.wikipedia.org]

- 21. drpress.org [drpress.org]

- 22. mdpi.com [mdpi.com]

- 23. researchgate.net [researchgate.net]

- 24. researchgate.net [researchgate.net]

- 25. Beat the Heat in 3D Chip Stacks with Embedded Cooling | Electronics Cooling [electronics-cooling.com]

- 26. poplab.stanford.edu [poplab.stanford.edu]

- 27. chem.rutgers.edu [chem.rutgers.edu]

- To cite this document: BenchChem. [Technical Support Center: Overcoming Challenges in Scaling Down Silicon-Based Transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1239273#overcoming-challenges-in-scaling-down-silicon-based-transistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com